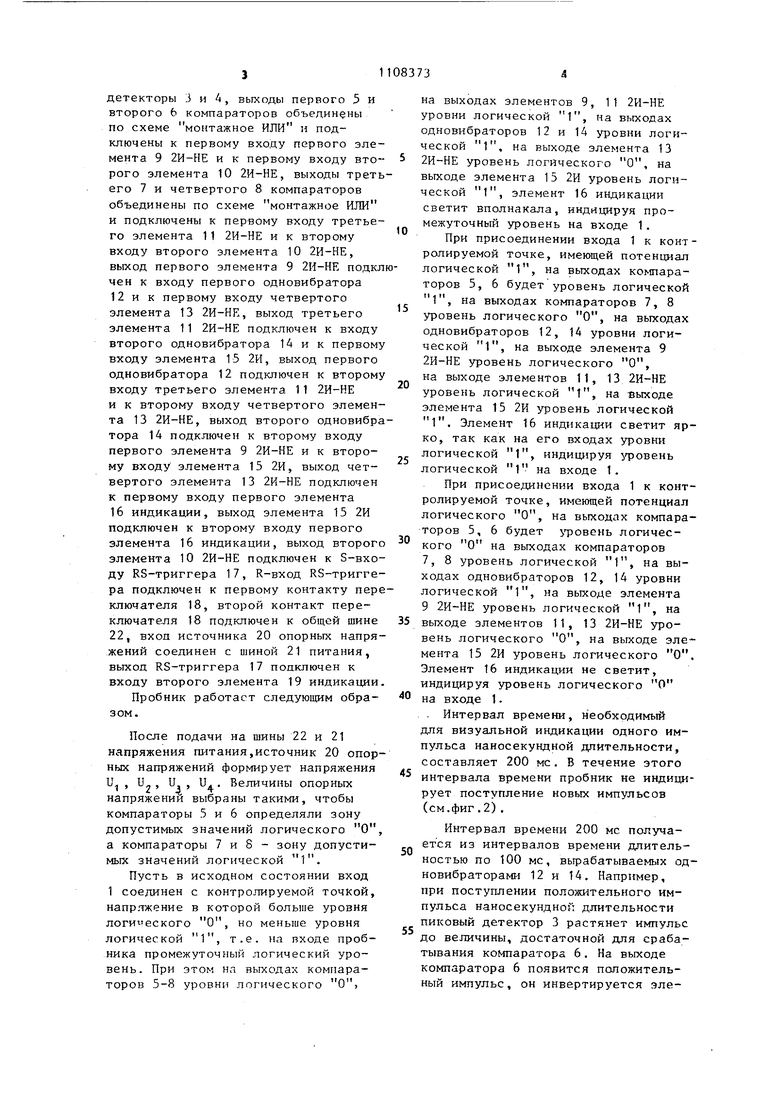

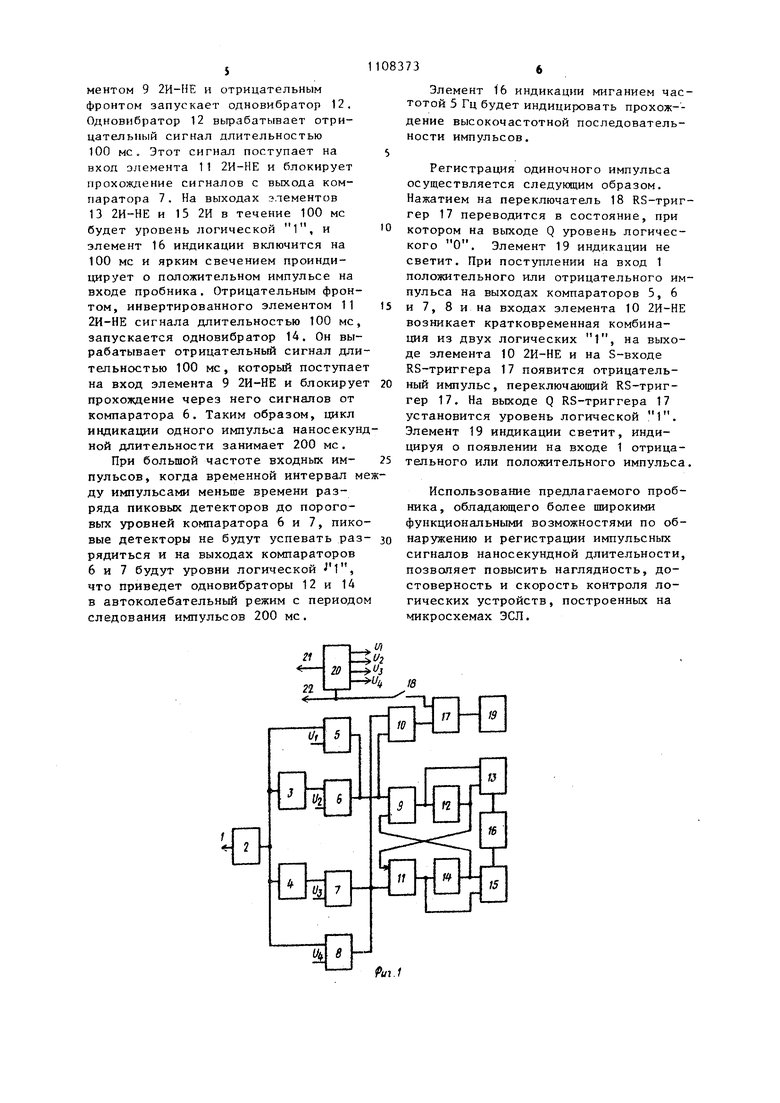

Изобретение относится к электроизмерительной технике и может быть использовано для проверки устройств построенных на логических элементах эмиттерно-связанной логики (ЭСЛ), Известен логический тестер для проверки устройств на логических элементах ЭСЛ, отобража зций логичес кие уровни на выводах проверяемых микросхем. Тестер содержит шесть компараторов, выходы которых соединены с входами двух схем ИЛИ и входами схемы И соответственно, источник опорных напряжений, последовательно включенные три усилителя и три индикаторных элемента, соответствующие входы компараторов соедине ны с блоком СОНаиболее близким к изобретению по технической сущности является пробник, содержащий четыре компаратора, одни входы которых соединены с соответствующими исто никами опор ного напряжения, а другие входы - с входом пробника через схему защиты и три индикаторных элемента, управляемых соответствующими комгсаратора ми 2. Недостаток указанных пробников заключается в ограниченных функцио--.. нальных возможностях - пробники инд цируют только статические или медленно меняющиеся (длительность импульса не менее 100 мс) сигналы, в то время как проверяемые микросхе мы ЭСЛ работают с сигналами наносекундной длительности, Целью изобретения является расши рение функциональных возможностей пробника за счет обнаружения и регистрации импульсных сигналов наносекундной длительности. Цель достигается тем, что в проб ник, содержащий четыре компаратора первые входы которых соединены с соответствующими выходами источника опорных напряжений, вторые входы первого и четвертого компараторов с входом пробника через блок защиты и два индикатора, введены два пиковых детектора, два одновибратора, четыре элемента 2И-НЕ, элемент 2И, RS-триггер и переключатель, при это первый пиковый детектор включен меж ду BF.ixonoM блока защиты и вторым входом второго компаратора, второй пиковый детектор включен между выходом блока 3au iiT-t,i и вторым входом третьего компаратора , выхоль; первог и второго KONmapaTopOB объединены по схеме монтажное ИЛИ и подключены к первому входу первого элемента 2И-НЕ и к первому входу второго элемента 2И-НЕ, выходы третьего и четвертого компараторов объединены по схеме монтажное ИЛИ и подключены к первому входу третьего элемента 2И-НЕ и к второму входу второго элемента 2И-НЕ, выход первого элемента 2И-НЕ подключен к входу первого одновибратора и к первому входу четвертого элемента 2И-НЕ, выход третьего элемента 2И-НЕ подключен к входу второго одновибратора и к первому входу элемента 2И, выход первого одновибратора подключен к второму входу третьего элемента 2И-НЕ и к второму входу четвертого элемента 2И-НЕ, выход второго одновибратора подключен к второму входу первого элемента 2И-НЕ и к второму входу элемента 2И, выход четвертого элемента 2И-НЕ подключен к первому входу первого элемента индикации, выход элемента 2И подключен к второ му входу первого элемента индикации, выход второго элемента 2И-НЕ подключен к S-входу RS-триггера, R-вход RS-триггера подключен-к первому кон .. i..-ij ХЧУ.. такту переключателя, второй контакт переключателя подключен к общей шине, вход источника опорных напряжений соединен с шиной питания, выход RS-триггера подключен к входу второго элемента индикации, На фиг. 1 представлена блок-схема предлагаемого пробника; на фиг, 2 - режимы работы пробника. Пробник содержит вход 1, блок 2 защиты, пиковые детекторы 3, 4, компараторы 5-8, элементы 9, 10, 11 2И-НЕ, одповибратор 12, элемент 13 2И-НЕ, одновибратор 14, элемент 15 2И, элемент 16 индикации, RS-триггер 17, переключатель 18, элемент 19 индикации, источник 20 опорных напряжений, шину 21 питания, общую щину22. При реализации данного устройства следует учитывать, что пиковые детекторы 3, 4 выполнены по основной схеме амплитудных детекторов и имеют цепи разряда - входные цепи компараторов 6, 7. Вторые входы первого 5 и четвертого В компараторов соединены с выходом блока 2 защиты, вторые входы второго 6 и третьего 7 компараторов соединены с выходом блсп-са 2 защиты через соответствующие пиковыс детекторы 3 и А, выходы первого 5 и второго 6 компараторов объединены по схеме монтажное ИЛИ и подключены к первому входу первого элемента 9 2И-НЕ и к первому входу второго элемента 10 2И-НЕ, выходы треть его 7 и четвертого 8 компараторов объединены по схеме монтажное ИЛИ и подключены к первому входу третьего элемента 11 2И-НЕ и к второму входу второго элемента 10 2И-НЕ, выход первого элемента 9 2И-НЕ подкл чен к входу первого одновибратора 12 и к первому входу четвертого элемента 13 2И-НЕ, выход третьего элемента 11 2И-НЕ подключен к входу второго одновибратора 14 и к первом входу элемента 15 2И, выход первого одновибратора 12 подключен к втором входу третьего элемента 11 2И-НЕ и к второму входу четвертого элемен та 13 2И-НЕ, выход второго одновибр тора 14 подключен к второму входу первого элемента 9 2И-НЕ и к второму входу элемента 15 2И, выход четвертого элемента 13 2И-НЕ подключен к первому входу первого элемента 16 индикации, выход элемента 15 2И подключен к второму входу первого элемента 16 индикации, выход второг элемента 10 2И-НЕ подключен к S-вхо ду RS-триггера 17, R-вход RS-тригге ра подключен к первому контакту пер ключателя 18, второй контакт переключателя 18 подключен к общей шине 22, вход источника 20 опорных напря жений соединен с шиной 21 питания, выход RS-триггера 17 подключен к входу второго элемента 19 индикации Пробник работает следующим образом. После подачи на шины 22 и 21 напряжения питания,источник 20 опор ных напряжений формирует напряжения и , „, и , и. . Величины опорных напряжении выбраны такими, чтобы компараторы 5 и 6 определяли зону допустимых значений логического а компараторы 7 и 8 - зону допустимых значений логической 1. Пусть в исходном состоянии вход 1 соединен с контролируемой точкой, напряжение в которой больше уровня логического О, но меньше уровня логической 1, т.е. на входе пробника промежуточный логический уровень. При этом на выходах компараторов 5-8 уровня логического 0 на выходах элементов 9, 11 2И-НЕ уровни логической 1, на выходах одновибраторов 12 и 14 уровни логической 1, на выходе элемента 13 2И-НЕ уровень логического О, на выходе элемента 15 2И уровень логической 1, элемент 16 индикации светит вполнакала, индицируя промежуточный уровень на входе 1. При присоединении входа 1 к контролируемой точке, имеющей потенциал логической 1, на выходах компараторов 5, 6 будет уровень логической 1, на выходах компараторов 7, 8 уровень логического О, на выходах одновибраторов 12, 1А уровни логической 1, на выходе элемента 9 2И-НЕ уровень логического О, на выходе элементов 11, 13 2И-НЕ уровень логической 1, на выходе элемента 15 2И уровень логической 1. Элемент 16 индикации светит ярко, так как на его входах уровни логической 1, индицируя .фовень логической 1 на входе 1. При присоединении входа 1 к контролируемой точке, имеющей потенциал логического О, на выходах компараторов 5, 6 будет фовень логического О на выходах компараторов 7, 8 уровень логической 1, на выходах одновибраторов 12, 14 уровни логической 1, на выходе элемента 9 2И-НЕ уровень логической 1, на выходе элементов 11, 13 2И-НЕ уровень логического О, на выходе элемента 15 2И уровень логического О. Элемент 16 индикации не светит, индицируя уровень логического О на входе 1. Интервал времени, необходимый для визуальной индикации одного импульса наносекундной длительности, составляет 200 мс. В течение этого интервала времени пробник не индицирует поступление новых импульсов (см.фиг.2). Интервал времени 200 мс получается из интервалов времени длительностью по 100 мс, вьфабатываемых одновибраторами 12 и 14. Например, при поступлении положительного импульса наносекундной длительности пиковый детектор 3 растянет импульс до величины, достаточной для срабатывания компаратора 6. На вьгходе компаратора 6 появится положительный импульс, он инвертируется элементом 9 2И-НЕ и отрицательным фронтом запускает одновибратор 12. Одновнбратор 12 вьфабатывает отрицательный сигнал длительностью 100 мс. Этот сигнал поступает на вход элемента 11 2И-НЕ и блокирует прохождение сигналов с выхода компаратора 7. На выходах элементов 13 2И-НЕ и 15 2И в течение 100 мс будет уровень логической 1, и элемент 16 индикации включится на 100 мс и ярким свечением проиндицирует о положительном импульсе на входе пробника. Отрицательным фронтом, инвертированного элементом 11 2И-НЕ сигнала длительностью 100 мс, запускается одновибратор 14. Он вырабатывает отрицательный сигнал длительностью 100 мс, который поступает на вход элемента 9 2И-НЕ и блокирует прохождение через него сигналов от компаратора 6. Таким образом, цикл индикации одного импульса наносекундной длительности занимает 200 мс.

При большой частоте входных импульсов, когда временной интервал меду импульсами меньше времени разряда пиковых детекторов до пороговых уровней компаратора 6 и 7, пиковые детекторы не будут успевать разрядиться и на выходах компараторов 6 и 7 будут уровни логической 1, что приведет одновибраторы 12 и 14 в автоколебательный режим с периодом следования импульсов 200 мс.

Элемент 16 индикации миганием частотой 5 Гц будет индицировать прохож-дение высокочастотной последовательности импульсов.

Регистрация одиночного импульса осуществляется следующим образом. Нажатием на переключатель 18 RS-триггер 17 переводится в состояние, при котором на выходе Q уровень логического О. Элемент 19 индикации не светит. При поступлении на вход 1 положительного или отрицательного импульса на выходах компараторов 5, 6 и 7, 8 и на входах элемента 10 2И-НЕ возникает кратковременная комбинация из двух логических 1, на выходе элемента 10 2И-НЕ и на S-входе RS-триггера 17 появится отрицательный импульс, переключающий RS-триггер 17. На выходе Q RS-триггера 17 установится уровень логической 1. Элемент 19 индикации светит, индицируя о появлении на входе 1 отрицательного или положительного импульса

Использование предлагаемого пробника, обладающего более широкими функциональными возможностями по обнаружению и регистрации импульсных сигналов наносекундной длительности, позволяет повысить наглядность, достоверность и скорость контроля логических устройств, построенных на микросхемах ЭСЛ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ТЕСТЕР | 1997 |

|

RU2133475C1 |

| Логический пробник | 1983 |

|

SU1216746A1 |

| Ультразвуковой эхо-импульсный толщиномер | 1990 |

|

SU1781538A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1310755A1 |

| Логический пробник | 1980 |

|

SU917144A1 |

| Устройство для индицирования текущего времени | 1989 |

|

SU1661719A1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Устройство для контроля импульсных трансформаторов в составе электронных блоков | 1987 |

|

SU1471158A1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Катетер | 1990 |

|

SU1813456A1 |

ПРОБНИК ДЛЯ ПРОВЕРКИ ЛОГИГИЧЕСКИХ УСТРОЙСТВ НА МИКРОСХЕМАХ ЭМИТТЕРНО-СВЯЗАННОЙ ЛОГИКИ, содержащий четыре компаратора, первые входы которых соединены с соответствующими выходами источр1ика опорных напряжений, вторые входы первого и четвертого компараторов - с входом пробника через блок защиты и два индикатора, отличающийся тем, что, с целью расш грения функциональных возможностей за счет обнаружения и регистрации импульсных сигналов наносекундной дли- ельности, в него введены цва пиковых детектора, два одновибратора, четьфе элемента 2 И-НЕ, элемент 2 И, RS-триггер и переключатель, при этом первый пиковый детектор включен между выходом блока защиты и вторым входом второго компаратора, второй пиковый детектор включен между выходом блока защиты и вторым входом третьего компаратора, выходы первого и второго компараторов объединены по схеме монтажное ИЛИ и подключены к первому входу первого элемента 2И-НЕ и к первому входу второго элемента 2И-НЕ, выходы третьего и четвертого компараторов объединены по схеме монтажное ИЛИ, и подключены к .первому входу третьего элемента 2И-НЕ и к второму входу второго элемента 2И-НЕ, выход первого элемента 2И-НЕ подключен к входу первого одновибратора и к первому входу четвертого элемента 2И-НЕ, выход третьего элемента 2И-НЕ подключен к входу второго одновибратора и к первому входу элемента 2И, выход первого одновибратора подключен к второму входу третьего элемента 2И-НЕ и к второму входу четвертого элемента 2И-НЕ, выход второго одновибратора подключен к второму входу первого элемента 2И-НЕ и к второму входу элемента 2И, выход четвертого О С элемента 2И-НЕ подключен к первому входу первого элемента индикации, выход элемента 2И подключен к второму входу первого элемента индика00 ции, выход второго элемента 2И-НЕ оо подключен к S-входу RS-тряггера, R-вход RS-триггера подключен к перОд вому контакту переключателя, второй контакт переключателя подключен к . общей шине, вход источника опорных напряжений соединен с шиной питания, выход RS-триггера подключен к входу второго элемента индикации.

1- индикатор не сдетит

1- индикатор светит вполнакала

J- индикатор сбетит рко

t,HC

Фиг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический тестер | 1978 |

|

SU748263A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4189673, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-08-15—Публикация

1983-01-19—Подача