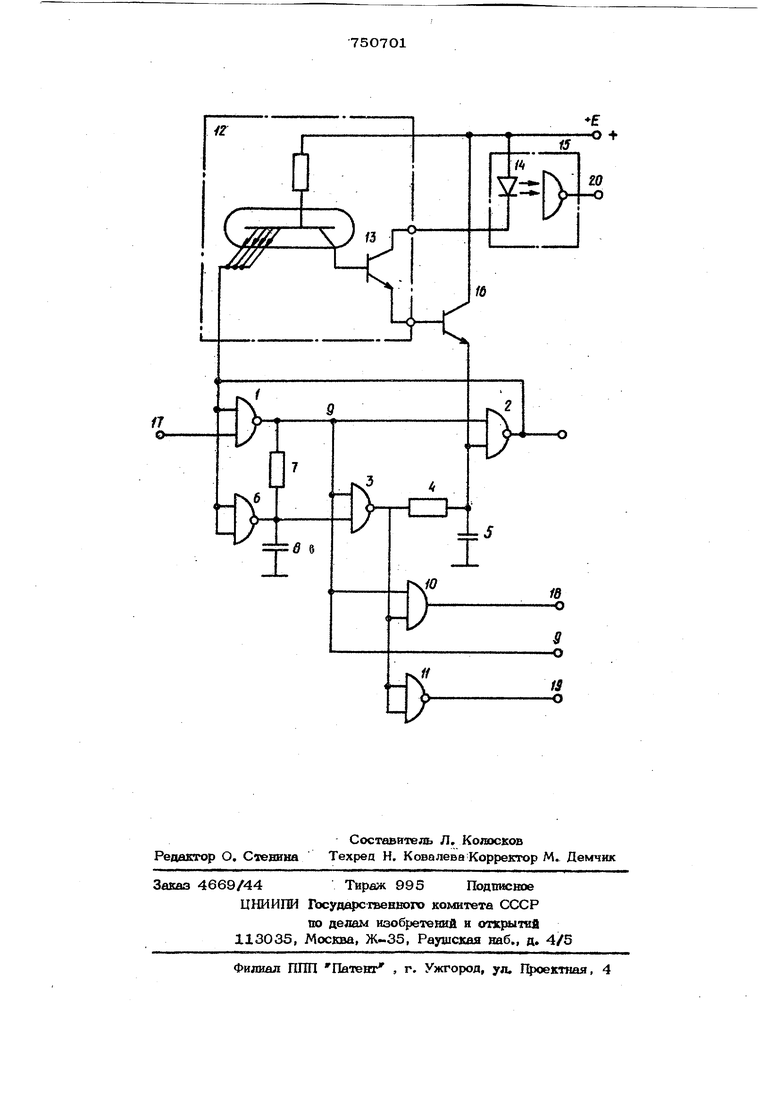

Изобретение относится к импульсной технике и может быть использовано в раз личных цифровых устройс-гаах и устройс-рвах дискретной автоматики. Известен формирователь импульсов, со держащий триггер, выполненный на вентц лях ТТЛ И-НЕ, вход которого через времязадающую цепь соединен с выходом логического элемента И-НЕ, охваченного через резисторный делитель отрицательной обратной связи, вхоа которого через диод подключен к единичному выходу трнт Гбра PL, Однако время восстановления таких формирователей велико, так как пос ле возвращения триггера в заданное устой чивое состояние заряд времязадающего конденсатора происходит в основном через эквивалентное сопротивление в коолзк торной цепи выходного транзистора логического элемента и связанного с ним времязадакнцего резистора Наиболее близким по отношению к предложенному устройству является формирователь иктульсов, содержащий триггер на элементах И-НЕ, вход которого соединен через времязадающуго цепь с выходом логического элемеита И-НЕ, один вход которого соединен с единичным выходом триг.. гера непосредственно, а другой - через дополнительную интегрирующую цепь Г2.. Однако такой формировате/ также имеет большое время восстановления из-за того, что разряд конденсатора донолнительнсЛ (штегрирующей цепи и заряд конденсатора времязадаюшей цепи проходит через резисторы, величина тем больше, чем. больше длительность, которые необходимо формировать. Кроме того, перечисленные устройства не обладают расширенными фyнкциcя{aльнь ми возможностями. Цель изобретения - уменьшение времени восстановления устройства и расширение его фуншиональных возможностей. Указанная цель достигается за счет того, что в формирователе импульсов, содержащий триггер на элементах И-НЕ, первьй вход которого соединен через время375задающую цепь с выходом: логического эл мента И-НЕ, один вход которого соединен с единичным выходом триггера непосредст венно, а другой - через интегрирующую це введены логический элемент И-НЕ со свобохшым коллектором, расширитель числа входов ИЛИ, п - р - п -транзистор, инвертор, логический элемент И и оптронн и инвертор переключатель, при этом нулевой выход триггера соединен через логический элемент И-НЕ со свободным коллектором с выходом интегрирующей цепи и подключен ко аходам расширителя числа входов ИЛИ, в коллекторной цепи выходного тран зистора которого включен излучающий диод оптронного инвертора-переключателя, анодом подключенный к источнику питания и коллектору п-р-п транзистора, база которого соединена с эмиттером выХОД110ГО транзистора расширителя числа входов ИЛИ, а эмиттер- к первому входу триггера, причем один выход логическо го элемента И соединен с выходом логического элемента И-НЕ и входом инвертора, а второй его вход соедтюн с единичным выходом триггера. На чертеже представлена принципиальная схема предлагаемого формирователя им пульсов. , Формирователь импульсов, вьтолненный на логических элементах, содержите триггер на элементах И-НЕ 1, 2, охваченных перекрестными связями единичный, выход триггера соединен со своим первым входом через последовательно соединенные логИ ческий элемент И-НЕ 3 и времязадающую цепь, состоящую из резистора 4 и конденсатора 5. Нулевой выход триггера соедине с входами логического элемента И-НЕ 6, свободный коллектор которого подключен к выходу интегрирующей цепи, состоящей из резистора 7 и конденсатора 8, и одному из входов логического элемента И-НЕ 3, второй вход которого соединен с единичным выходом 9 триггера и одним из входов логического элемента И 10, второй . вход которого соединен с выходом логичес кого элемента 3 и входами инвертора 11. Нулевой выход триггера соединен также с входами расширителя числа входов ИЛИ 12, в коллекторной цепи выходного транзистора 13 которого включен излучающий диод 14 оптронного инвертора-переключателя 15, анод которого подключен к источ нику питания и коллектору П-р-П-транзисто ра 16, база которого соединена с эмиттером, транзистора 13, а эмиттер - с первы входом триггера. „ 14 Схема работает следующим образом. В исходном состоянии на сигнальный вход 17 триггера подается положитёльньш потенциал. Нри этом на единичном и нулевом выходах триггера действуют соответственно низкий и высокий уровни напряжения. Под дейс тием высокого уровня напрялсеиия на нулевом ввцсоде триггера выходной транзистор 13 расширителя числа входов ИЛИ ип -р-ГУ-транзистор 16, а также выходной транзистор логического элемента 6 открыты и насыщены. При этом конденсатор 5 заряжен практически, до нат1р:яжения источника питания. Конденсатор 8 разряжен через насыщенный выходной транзистор логического элемента 6. На выходах. 18. и 19 действуют низкие (нулевые) уровни напряжения. На выходе 20 оптронного инвертора-переключателя 15 действует высокий уровень напряжения. При поступлении отрицательного импульса на сигнальный вход 17 триггера последний переходит в прот1шоположное состояние , характеризуемое ж гической единицей на единичном выходе триггера и логическим нулем - на нулевом. При этом транзистор 16 и выходной транзистор лошческого элемента 6 скачкообразно закрываются и в дальнейшем, в течение всего времени квазиустойчивого рав- новееия, на работу-схемы неоказьшают никакого влияния. Под действием высокого уровня напряжения на единичном выходе триггера происходит заряд конденсатора 8 через резистор 7 и сопротивление в цепи коллектора выходного транзистора ло гического элемента 1. Через время, загдаваемое интегрирующей цепью, напряжение на нвм достигает порога срабатьтания элемента 3. В результате воздействия высоких уровней напряжения на обоих входах лoг Recкoгo элемента З.на его выходе устанавливается уровень логического нуля Ковденсатор 5, заряи нный через насыщенный транзистор 16 практически до уровня напряжения питания, начинает разряжаться через резистор 4 и сопротивление промежутка кол;юктор-эмиттер выходного транзистора логического элемента 3. Через время, определяемое времязадающей цепью, напряжение на конденсаторе 5 достигает порот срабатьшания элемента 2 и триггер возвратится в исходное состояние, заканчивая формирование импульса. Под воздействием высокого напряжения на нулевом выходе триггера заряднь й транзистор 10 и выходной транзнстор логического элемента 6 открывают ся и насьшдаются. При этом конденсатор 8 разряжается через сопротивлени.е участ ка коллектор-эмиттер насьЕценного выходного транзистора элемента 6, а конденсатор 5 быстро дозаряжается через насыщен ный зарядный транзистор 16, В момент заряда конденсатора 5 через излучающий диод 14 протекает ток дозаряда, возбуждающий оптронный инйертор шрекяю- чате ль, на выходе 20 которого формируется короткий отрицательный импульс конец формирования. Таким образом, применение устройства форсированного дозаряда одного из времязадающих конденсаторов и принудительный разряд другого позволяет уменьшить время восстановлюния устройства. Кроме того, вследствие того, что конденсатор 5 удается дозарядить до более высокого уровня (по сравнению с прототипом) длительность форг ируемого импульса автоматически увеличивается. Предложенный формирователь импульсов обладает расширенными функциональными возможностями, так как позволяет дополнитюльно формировать импульс конец формирования, а также положительные имтгул сы различной длительности: снимаемый с выхода 18 логического элемента Ю, и снимаемый с выхода 19 логического элемента 11, Формула изобретения Формирователь импульсов, содержащий триггер на элементах И-НЕ, первый вход которого соединен через времязадающую цепь с выходом логического элемента И-НЕ, один вход которого соеди{ген с едиНИчным выходом триггера непосредственно, а другой - через интегрирующую цепь, отличающийся тем, что,с целью уменьшения времени восстановления и расширеетя функциональных возмоишостей устройства, в него введены логический элемент И-НЕ со свободным коллэктором, расширитель числа входов ИЛИ, п р-птранзистор, инвертор, лошческий элемент И и оптронный инвертор-переключатель, при этом нулевой выход триггера соединен через логический элемент И-НЕ со сво бодным коллектором с выходом интегрир тсщей цепи и подключен ко входам расширителя числа входов ИЛИ, в коллекторной цепи выходного транзистора которого включен излучающий диод оптронного инвертора-переключателя, анодом подключенный к источнику питания и коллектору V -Р-Л-трс-нзистора, база которого соединена с алиттером выходного транзистора расширителя числа входов И/М, а эмиттер - к тюрвому входу триггера,причем один вход логического элемента И соединен с выходом логического элемента И-НЕ и входом инвертора, а второй его вход соедйНЕН с единичным выходом триггера. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР М 539367, кл. Н 03 К 3/284, 1975. 2.Авторское свидетельство СССР №487449, кл. Н 03 К 3/28, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одновибратор | 1978 |

|

SU733088A1 |

| Формирователь импульсов | 1979 |

|

SU841096A1 |

| Генератор импульсов | 1978 |

|

SU790109A1 |

| Одновибратор | 1976 |

|

SU612392A1 |

| Преобразователь последовательности импульсов в прямоугольный импульс | 1978 |

|

SU752775A1 |

| Ждущий мультивибратор | 1977 |

|

SU674203A1 |

| Формирователь импульсов | 1981 |

|

SU1018213A1 |

| Одновибратор | 1977 |

|

SU632058A1 |

| Генератор прямоугольных импульсов | 1979 |

|

SU855949A1 |

| Устройство задержки импульсов | 1979 |

|

SU856000A1 |

Авторы

Даты

1980-07-23—Публикация

1978-06-05—Подача