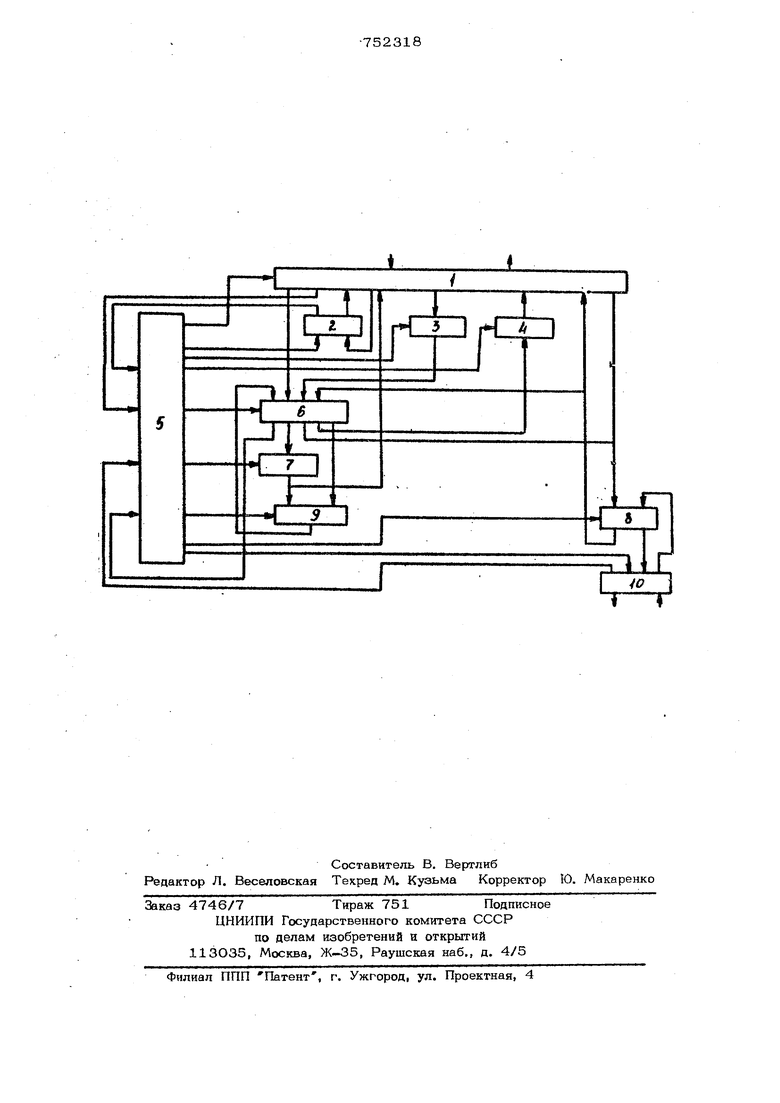

Изобретение относится к цифровой вычислительной технике и может быть использовано для ввода-вывода информации в цифровых вычислительнык машинах и системах, в которых взаимосвязь устройств осуществляется через магистральный канал или общую шину, Известны мультиплексные каналы, содержащие блок для сопряжения с внешними устройствами, регистр информации, блок местной памяти, управляющий блок, регистр для хранения управляющей информации, блок модификации адресов и счета данных, блок для сопряжения с процессором и блок для сопряжения с оперативной памятью |lj, Недостатком этих устройств являются ограниченные функциональные возможности канала, обусловленные невозможностью работы с процессором, подключенным по магистрали типа общая шина. Наиболее близким по технической сущ,ности к предлагаемому является мультиплексный канал, содержащий регистр уп- равляющей информации, блок местной памяти, первый вход и первый выход которого соединены соответственно с вым выходом и первым входом регистра управляющей информации, блок модификации адресов и счета данных, информационный вход которого соед{гаен со вторым выходом регистра управляющей информации, а выход - со вторым входом блокп местной памяти, буферный регистр, блок для сопряжения с внешними устройствами, первый вход и первый выход которого соединены соответственно с первым выходом и первым входом буферного регистра, управляющий блок, первый, второй, третий, четвертый выходы которого соединены соответственно с управляющими входами регистра управляющей информации, блока местной памяти, блока модификации адресов и счета данных, буфе| ного регистра, пятый выход, первый и второй входы управл5пощего блока соединены соответственно со вторым входом, вторым выходом блока для сопряжения с внешними устройствами и с третьим выходом регистра управляющей информа ции. Кроме того, этот мультиплексный канал содержит блок для сопряжения с процессором и блок для сопряжения с оперативной памятью 21. Недостаток этого канала состоит в ограниченных функциональных возможностях, что не позволяет обеспечить работу канала с процессором, подключенным к. общей магистрали. Цель изобретения - расширение функ циональных возможностей канала за счет обеспечения его работы с магистралью типа общая шина. Поставленная цель достигается тем, что в мультиплексный канал, содержащий блок сопряжения с процессором, пер вые. вход и выход которого являются первыми входом и выходом канала, ре™ гистр управляющей информации, блок местной памяти, первые вход и выход которого соединены соответственно с пер выми выходом и входом регистра управ- Лйсющей информации, блок модификации адресов и счета данных, информационный вход которого соединен со вторым выхО дом регистру, управляющей информации, а выход - со вторым входом блока мест ной памяти, буферный регистр, блок соп ряжения с внешними устройствами, пер- вые вход и выход которого соединены соответственно с первыми выходом и входом буферного регистра, управляющий блбк, первый, второй, третий и четверты выходы которого соединены соответствен но со вторым, входом регистра управляющей информации, третьим входом блока местной памяти, управляющим входом .блока модификации адресов и счета данных и вторым входом буферного регистра, пятый выход и первый и второй входы управляющего блока соединены соот ветственно со вторыми входом и выходом блока сопряжения с внешними устройствами и с третьим выходом регистра управляющей информации, третьи вход и выход блока сопряжения с внещними уст ройствами являются соответственно вторыми входом и выходом канала, введены регистр команд н -состояний, регистр адреса, регистр выходной информации, причем вторые вход и выход блока сопряжения с процессором соединены соответст- венно с первыми выходом и входом ре л истра команд и состояний, второй выход и второй вход которого соединены соот ветствэнно с третьим входом н шестым 7 84 выходом управляющего блока, третий и четвертый входы блока сопрояжения с процессором соединены соответственно с выходом блока модификации адресов и счета данных и выходом регистра выходной информации, первый вход которого соединен с четвертым выходом регистра управляющей информации, пятый выход которого соединен с третьим выходом бло ка сопряжения с процессором и третьим входом буферного регистра, второй выход которого соединен с пятым входом блока сопряжения с процессором и треты им входом регистра управляющей тюфор- мадии, четвертый и пятый входы которого соединены соответственно с четвертым выходом блока сопряжения с процессором и выходом регистра адреса, первый вход которого соединен с пятым выходом блока сопряжения с процессором, шестой выход которого соединен с четвертым входом управляющего блока, седьмой , восьмой и девятый выходы которого соединены с соответственно со вторы- ми входами регистра адреса, регистра выходной информации и шестым входом блока сопряжения с процессором. На чертеже показана блок-схема мулй«. типлексного канала. : Мультиплексный канал содержит блок 1 сопряжения с процессором, регистр 2 команд и состояний, в котором хранятся .код команды ввода-еьшода, признак готовности, признак результата, признаки прерываний и признак уточнения прерывания, регистр 3 адреса, содержащий регистр адреса внешнего устройства и буферный регистр адреса первого командного слова канала, регистр 4 выходной ин рмации, содержащий регистр слова состояния канала и регистр кода прерыва- ния, управляющий блок 5, регистр 6 уп- равлшощей информации, содержащий регистры для хранения адреса командного слова канала, адреса внешнего устройст ва, кода операции, счета байтов, адреса данных, блок 7 модификации адресов и счета данных, буферный регистр 8, содер жащий регистр абонента н регистр канала, блок Э местной памяти и блок 1О сопряжения с внешними устройствами. Устройство работает следующим образом, Работа мультиплексного канала запускается в результате последовательных операций в магистральном канале. При задании команды Начать ввод вьтод процессор (на чертеже не показан) загру5жает через блок 1 в регистр 3 адрес первого командного слова канала и адрес внешнего устройства, а регистр 2 - код команды ввода-вывода. При этом управл щим блоком 5 сбрасывается признак го- товности в регистре 2. Код команды ввода-«ывода с выхода Ьегистра 2 поступает на вход управляющего блока 5. После окончания текущего Цикла передачи данных адрес первого командного слова канала и адрес внеш- йего устройства записываются из регист ра 3 в регистр 6, Управляющий блок 5 Ьыдает сигнал, запускающий выборку бло tcoM 1 командного слова канала из one- ративной памяти (на чертеже не показано) в регистр 6 в режиме прямого доступа. В процессе выборки блок 7 модифицирует адрес командного слова канала. Блоком 10 осуществляется выборка одного из внешних устройств (на чертеже не показаны) по адресу, содержащемуся в регистре 6, и выдача кода операции. ; Управляющий блок 5 устанавливает в регистр 2 признак результата, отражающий возможность вьгаолнения команды Начать ввод-вывод при текущих состоя ниях канала, подканала и внешнего устройства, С установкой признака результата восстанавливается признак готовности в регистре 2. При мультиплексном режиме работы управляющая информация из регистра 6 и блока 7 записывается в соответствующую ячейку блока 9. После выдачи команды Начать вводвывод процессор периодически анализирует информацию, содержащуюся в регистре 2 в ожидании формирования признака результата, завершение которого определяется по установке признака гото ности в регистре 2. Операция ввод-«ывода продолжается мультиплексным каналом после появления запроса от внешнего устройства, поступающего через блок Ю в управляющи блок 5. Полученный от внешнего устройства адрес через регистр 8 записьгоается в регистр 6 и используется для выборки управляющей информации операции вводавывода из блока 9 в регистр 6. При операции чтения байт данных, выданный устройством, через блок Ю загр жается в регистр 8. Управляющий блок 5 выдает в блок 1 сигнал, запускающий операцию записи на магистральном канале. В режиме прямого доступа байт данных из регистри. 8 загружается в опера- 18 тивную память по адресту, хранящемуся в регистре 6. После этого по сигналу, поступившему от управляющего блока 5, блок 7 модифицирует адрес данных и счет байтов. Выполнение мультиплексным каналом операции записи осуществляется аналогично выполнению операции чтения. В процессе передачи данных, при наличии соответствующих признаков в регистре 6, мультиплексный канал выполняет зацепление по данным или по команде. Управляющий блок 5 выдает указание, по которому блок 1 осуществляет чтение очередного командного слова канала из оперативной памяти в регистр 6 в режиме прямого доступа. При окончании передачи данных или при аппаратных ошибках управляющий блок 5 устанавливает в регистре 2 признак прерывания. С выхода регистра 2 признак прерывания поступает на вход блока 1, который (формирует запрос на| прерывание в магистральном канале. При обслуживании прерывания процессор через блок 1 читает содержимое регистра 2 и анализирует причину прерывания. В случае прерывания, обусловленного окончанием передачи данных, процессор имеет возможность через блок 1 установить в регистре 2 признак утошения прерывания, по которому управл5иощий блок 5 организует формирование слова состояния канала и кода прерывания (адреса внешнего устройства для которого сформулировано прерывание в регистре 4). По окончании формирования слова состояния и кода прерывания управляющий блок 5 устанавливает признак готовности в регистре 2. Установив признак уточнения прерывания, процессор периодически анализирует регистр 2 в ожидании завершения формирования слова состояния канала и кода прерывания, признаком чего является восстановление признака готовности. После этого процессор имеет возможность через блок 1 обратиться к регистру 4 для чтения слова состояния канала и кода прерывания. Восстановление признака готовности в регистре 2 сопровождается сбросом кода операции, признака прерывания, отражающего окончание передачи данных, и призна. ка уточнения прерывания. При сброшенном признаке готовности в регистре 2 мультиплексного канала вы-

дача процессором команд мупьтитшексно му каналу запрещена.

Таким образом, мультиплексный канал благодаря введению новык блоков может быть использован в системак, где связь мелоду устройствами осуществляется че рез магистральный канал или общую шину Тем самым обеспечивается возможность использования в таких системах внешних устройств, подключенных к интерфейсу

ввода-вывода ЕС ЭВМ. Кроме того, при выполнении мультиплексным каналом операции ввода-вывода имеется возможность использования подключенных к магистральному каналу внешних запоминающих устройств.

При использовании предложенного мультиплексного канала отпадает необходимость в аппаратных изменениях в контролерах внешних устройств ЕС ЭВМ при подключении их к ЭВМ с интерфейсами типа магистральный канал или общая шина. Возможность использования мультиплексного канала в таких системах, кроме того позволяет освободить процессор от выполнения операций ввода вывода, что повышает фективность его использования. Формула изобретения

Мультиплексный канал, содержащий блок сопряжения с процессором, первые вход и выход которого являются первыми входом и выходом канала регистр управляющей информации, блок местной памяти, первые вход и выход которого соединены соответственно с первыми выходом и входом регистра управляющей информации, блок модификации адресов и счета данных, информационный вход которого соединен со вторым выходом регистра управляющей информации, а выход - со вторым входом блока местной памяти, буферный регистр, блок сопряжения, с внешними устройствами, первые вход и выход которого соединены соот- . ветственно с первыми выходом и входом буферного регистра, управляющий блок, первый, второй, третий и четвертый выходы которого соединены соответственно со вторым входом регистра управляющей информации, третьим входом блока мест- ной памяти, управляющим входом блока модификации и счета данных и вторым входом буферного регистра, пятый выход

и первый и второй входы управляющего блока соединены соответственно со вто рыми входом и выходом блока сопряжения с внешними устройствами и с треть им выходом регистра управляющей информации, третьи вход и выход блока сопряжения с внешними устройствами являются соответственно вторыми входом и выходом канала, отличающийся тем, что, с целью расширения функциональных возможностей канала за счет обеспечения его-работы с магистралью типа общая ошна, в него введены регистр команд и состояний, регистр адреса и регистр выходной информации, причем вторые вход и выход блока сопрямсения с процессором соединены соответственно с первыми выходом и входом регистра команд и состояний, второй выход и второй вход которого соединены соответственно с третьим входом и шестым выходом управляющего блока, третий и четвертый входы сопряжения с процессором соединены соответственно с выходом блока модификации адресов и счета данных и выходом регистра вы- ходной информации, первый вход которо- Го соединен с четвертым выходом регистра управляющей информации, пятый выход которого соединен с третьим выходом блока сопряжения с процессором и третьим входом буферного регистра, второй выход которого соединен с пятым входом блока сопряжения с процессором и третьим входом регистра управляющей информации, четвертый и пятый входы которого соединены соответственно с четвертым выходом блока сопряжения с процессором и выходом регистра адреса, первый вход которого соединен с пятым выходом блока сопряжения с процессором, шестой выход которого соединен с четвертым входом управляющего блока, седьмой, восьмой и девятый выходы которого соединены соответственно со вторыми входами регистра адреса, регистра выходной информации н шестым входом блока сопряжения с процессором.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3336582; кл. 34О-172.5, 1968.

2,Авторское свидетельство СССР № 525079, кл. Q Об F 3/О4, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1980 |

|

SU938277A2 |

| Устройство сопряжения с магистралью | 1977 |

|

SU693364A1 |

| Мультиплексный канал | 1976 |

|

SU613316A1 |

| Мультиплексный канал | 1979 |

|

SU860044A2 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал | 1978 |

|

SU750473A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-17—Подача