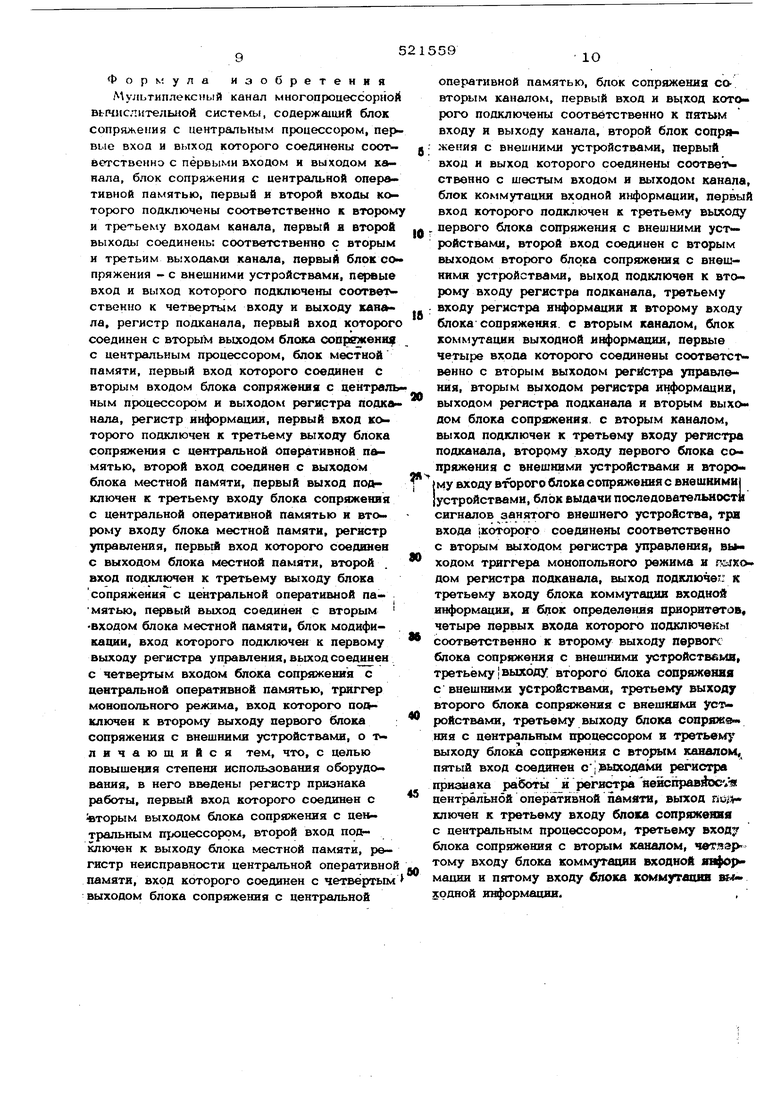

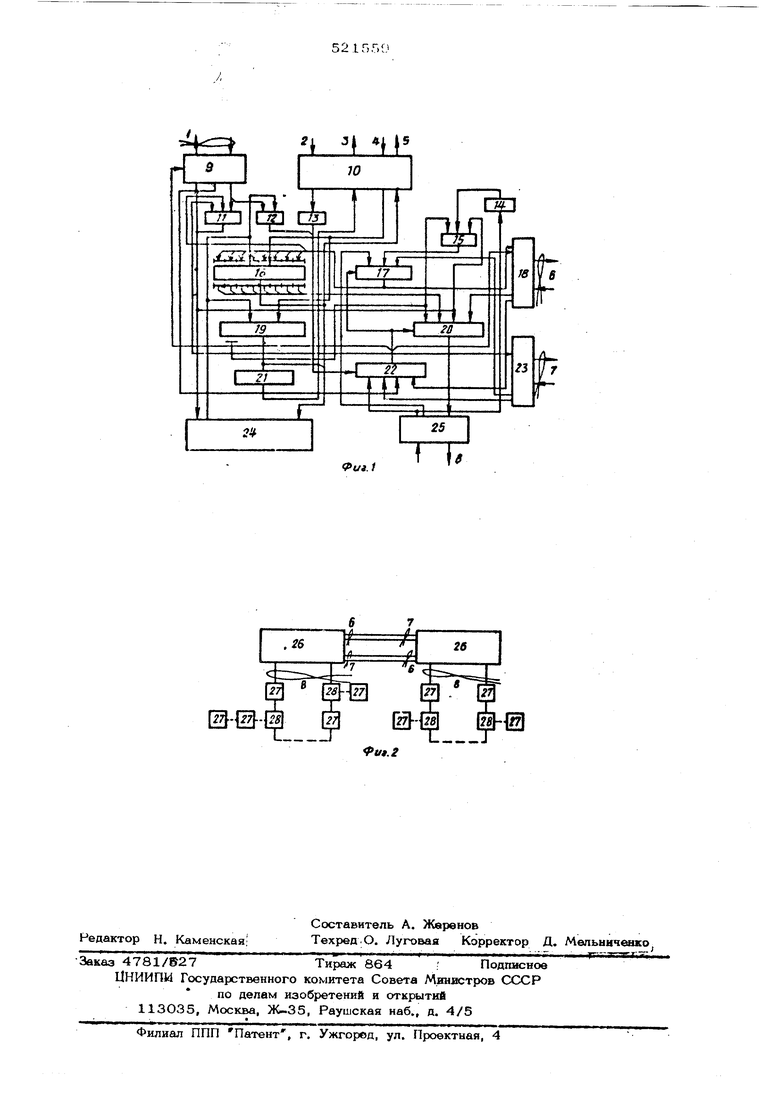

(54) МУЛЬТИПЛЕКСНЫЙ КАНАЛ МНОГОПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ центрального прсщессора многопроцессорной системы. В известных вычислительных системах указанная возможность реализуется во внешкизс устройствах (например, в устройстве сопряжения с накопителями на магзЕшткых дисках или на кшгннтныя лентах), нмекшшх возможность подключений к двум каналам кнтерфейса, ввода/вывода. Для обеспечения переключения устройства при работе с каналом испол;ьзук)тся комйнды рвзераированне и { азъединение , 1Подавлякхцее же больший- ство угггройстБ ввода/вывода этих систем имеют возможность подключеЕШя только к одному каналу и не отражают специфига мно гопронессорных систем. Создание общего поля для нескольких процессоров из таких знешких устройств при применеггаи стандартных каналов требует |;)азработки сггециальных устройств сопряжения. Недостйтками известного технического решекия, ориентированного только на повышении надежности, явля отся: необходимость установления конфигуращш системы (связей определенных внешних устройств с определенкьгми каналами ввода/вывода) с помошью специальной команды до начале работы внешних устройств-по обмену данными, т.е. статкчесясой настройки системы, что требует , наличия в центральном процессоре, канале и самоё аппаратуре соответствующих воэмож ностей; распределен-ие внешних устройств между каналами ввода/вывода (и далее цен«. тральными процессорами) возможно только с дискретностью до интерфейса ввода/вывода т.е. неско/гькнх внешних устройств, поэтому все устройства, подключенные к данному интерфейсу ввода/вывода, доступны только каЛалу, в конфигурацию которого он в этот мо мент входЕЕТ, поэтому некоторые внешние устройства могут быть ке ;загру кены (или вообще не работать), но другюму каналу до изменения конфигурации они не доступны; изменение конфигурации при отказе внешнего устройства возможно только по команде центрального процессора, который делает ВЬЕ вод об исправности внешних устройств к ре конфигурирует систему. Цель изобретения - повышение степени использования оборудования мультиплексного канала. Это достигается тем, что в канал введены регистр признака работы, первый вход которого соединен с вторым выходом блока сопряжения с центральным процессором, вто рой вход подключен к выходу блока местной памяти, регистр неисправности центральной оперативной памяти, вход которого соединен с четвертым выходом блока сопряжения с нейтральной оперативной памятью, блок со- Ijpsi/tUMiHH с вторым каналом, первый вход и выход которого подключены соответственно к пятым входу и выходу канала, второй блок сопряжения с внешни.ч-ш устройствами, пер- .i вый вход и выход которого соединены: соответственно с шестым входом и выходом канала, блок коммутации входной HiBfiopMauHK, вход которого подключен к третьему выходу первого блока сопряжения с внешними устройствами, второй вход соединен с вторым В1.1ХОДОМ второго блока сопряжения с внешними устройствами, а выход подключен к второму входу рзегистра подканала, третьему входу регистра И1в|юрмакии и второму входу, блока сопряжения с вторым каналом, блок коммутации выходной информации, первые четыре входа которого соединены соответственно с вторым выходом регнс тра управления, вторым выходом регистра информации, выходрм регистра подканала и вторым выходом блока сопряжения с вторым каналом, выход подключен к третьему входу регистра подканала, второму входу первого блока сопряжения с внешними устройствами и второму входу второго блока сопряжения с внешними устройствами, блок выдачи последовательности сигналов занятого внешнего устройства, три входа которого соединены соответственно с вторым выходом регистра управления, выходом триггера монопольного режима и выходом регистра подканала, выход подключен к третьему входу блока коммутации входной информации, л блок опрюделения приоритетов, четыре первых входа которого подключены соответственно к второму выходу первого блока сопряжения с внешю ми устройствами, третьему выходу второго блока сопряжения с устройстЕЗмн, третьему выходу блока сопряжения с центральным процессором и, третьим выходом блока сопряжения с вторым каналом, пятый вход соединен с выходами регистра признака работы и регистра неисправности централ ной оперативной памяти, выход подключен к третьему входу блока сопряжения с центральИз м процессором, третьему входу блока со- iipsDKeHHH с вторым каналом, четвертому 6хо« ду I блока коммутации входной информации и пятому входу коммутации выходной информации. Это позволяет без применения специальных команд (требуквдих доработки центрального процессора) распределять внешние устройства общего поля между центральными процессорами и дискретностью до внешнего устройства. На фиг. 1 показана структурная схлма мультиплексного канала (канал I и/ш каналИ) многопроцессорной вычислительной системы; на фиг. 2 - структурная схема общего поля устройств ввода/вывода, (внешней памяти) многопроцессорной системы, образованного с применением мультиплексного канала, на которых обозначены: 1 «- шиног связи канала с центральным гфоцессороК;} 2 - шина сигнала неисправности центральной опвра тивной памяти; 3 - выходные и;ины адреса ячейки центральной оперативной памя.и; 4- выходные шины ,мации., поступаюшей от центральной оперативной , памяти; 5-. выходные шины информации, передавд емой в центральную оперативную память; 6- интерфейс ввода/вывода сопряжещяя с каналом ff; 7 интерфейс ввода/вывода со-, пряжения с внеиншми устройствами канапа 8 интерфейс ввода/вывода для кошслюч НИИ внешних устройств каната I , Структурная схема мультиплексного ка нагш (фиг. l) содержит блок 9 сопряжения с центральнь М процессором; блок 10 сокряжэ1тя с центральной оперативной памятью; „регистр 11 подканала; регистр 12 признака работы;регистр 13 неисправности центральной оперативной памяти (или канала Ц, кро ме схем сопряжеш5я с каналом Н ), сигнал неисправности поступает по шине 2 и вырабатываетсй в канале; триггер 14 монопольного режима; блок 15 выдачи последователь ности сигналов занятого внешнего устройства; регистр 16 информации; блок 17 комму таднл входной информации; блок 18 сопряже ния с вторым каналом; регистр 19 управлвния, фиксирующий ключ зашиты, адрес унрав ляюшего слова канала (адрес данных), код операции, флажки, счет данных; блок 2О кок мутации выходной информации; блок 21 моди фикации; блок 22 определения приоритетов, которые распределены следующим образом: трюбование абонента на обслуживание от соб ственных внешних устройств канала Е , HHCTV. рукция от собственного центрального процессора, инструкция от второго центрального процессора через канал Я ; блок 2 3 сопряжения с внешними устройствами блок 24 мест ной памяти; блок 25 сопряжения с внешними устройствами. Для получения общего поля внешних уст- ройств (фиг. 2) два мультиплексных канала (один из которых условно назван канал, другой - канал ц) соей гаяются с помошью интерфейсов 6 и 7 ввода/вывода между собой, к интерфейсу 8 ввода/вывода подключены внешние устройства 27 и устройства 28 управления внешними устройствами. Мультиплексный канал управляется инcf рукциями и вьшолняет все операции по вводу/выводу информации, определяемые коман- дами единой системы электр чных вычислительных машин (ЕС-ЭВМ). Инструкция состоит из 32 разрядов О-31 ((разряды0-7- код инструкции, разряды 16-18 - адрес канала, разряд 23 (24) признак работы с рнешаим устройством второго канала, разряды 24-31 - адрес вне1№него устройства). Адресное слово канала содержит- 32 разряда 0-31 (разряды 0-3 - ключ защиты, разряды . « адрес управляюшего слова канала). Управляющее слово канала состоит из 64 разрядов О-63 (разряды 0-7 - код опер)ации, разряды 8-31 - адрес данных, paapstдь 32-36 флажки, разряды 47-63 данчьтх). Работа канала с внешни у устройством начинается по инструкции начать ввод/вывод, поступающей от центрального процеосора в блок 9 сопряжения с центральным процессором через .шины 1. Инструкция фиксируется в блоке 9 и при отсугствки сигналов более высокого приоритета на входе блока 22 определеддая приоритетоа, адрес внешнего устройства переписывается на регистр 11 подканшш, а признак работы с внешним устройством канала If на регистр 12. При отсутствии на регистр® 12 признака работы с внешним устройством каиала и по адресу на регистре 11 начинается выборка упрЗЕШяющей информации из блока 24 местной памяти на регистр 19 управления. При отсутствии в управляющей н 1формации признака работы данного внешнего устроййтва начинается его начальная выборка: адрес внешнего устройства через блок 2 О коммр. тации выходкой т1формации выдается в блок 25 сопряжения с внешними устройствами, Блок 25 осуществляет выборку, получает оъ« веткый адрес по шинам 8 интерфейса ввода/ вывода, сравнивает его. Параллельно в центральную одеративную память выдается на ишны 3 адрес ячейки йентральной оперативной памяти, формируемый блоком 1О сопряжения с центральной -оперативной-памятью. По этому адресу на регистр ТГ9 прочитывается адресное слово канала я далее по этому адресу управляющее слово канала. Изме нение ;адресов производится блоком 21 модификации. В процессе фиксации на регистре 19 управляющей информации последняя записывается в блок 24 местной памяти в зону, отведенную для ее хранения. Команда с регистра 19 выдается через блок 20 в блок25 и далее внешнему устройству. Полученный, от внешнего устройства нулевой байт состояния анализируется блоком 25, соответствукший сигнал через блок 22 выдается в блок 9, где используется для формирования и выдачи в центральный процессор по шинам 1 коа условия начала и продолжения операции. сли на регистре 12 зафиксирован признак аботы с внешним устройством II , означаюишй, что инструкция адресуется внешнему устройству канала Н, то по сигналу из блока 22 через блок 20 адрес пересылается в блок 23 сопряжения канала с внешними устройствами. Далее процесс установления канала с внешним устройством канала ЦТ не отличается от описанного выше. Только в разряде зоны блока 24 местной памяти мультиплексного канала, отведенной для фик- сащш состояния регистра 12, записывается работы с внешним устройством канала И . Сигнал начальной выборки с адресом внешнего устройства, приходящий в блок 18 сопряжения с вторым каналом из интерфейса 6 воспринимается как поступление команды (инструкции) от канала 1Г , направленной к внешним устройствам канала I . Анёлизиру- ется состояние триггера 14 монопольного регистра и при наличии монопольного режима блоком 15 выдачи последовательности сигналов занятого внешнего устройства выдается через блок 17 и блок 18 в канал по интерфейсу 6 байт состояния Внешнее устройство занято. При отсутствии на входе блока 22 сигналов с вьюшим приоритетом из блока 24 выбирается управляющая информация адресуемого подканала и подканал анализируется на занятость. Если подканал (внешнее устройство) занят, то блок 15 через блоки 17 и 18 и интерфейс 6 выдает байт состояния Внешнее устройство занято каналу И . Если подканал не занят, адрес внешнего устройства и сигнал начальной выборки блоком 20 транслируется в блок 25 и далее во внешнее устройство. Поступающи от внешнего устройства сигналы через интер фейс 8 ввода/вывода, блоки 25 я 1-7 транспируются в блок 18 и далее в канал Л без анализа их в канале I . При поступлении в блок 2 5 и далее на вход блока 22 требования от абонента на обслуживание блок 25 осуществляет выборк адреса этого абонента. Адрес абонента чере блок 17 заносится на регистр 11 подканала Из блока 24 считывается управляющая информация подканала на регистры 19, 12. При отсутствии на регистре 12 признака ра боты с внешним устройством кан&ла Я , на регистре 13 признака неисправности канала (центральной оперативной памяти) и наличии на регистре 19 команды определяется, что данное внешнее устройство работает с кана- . Дальнейшая работа записи(или считывания) дашпз1х ведется каналом.I . В соот

ветствии с управляюшей информацией подканала байты данных при операции Записать из регистра 16 информации чер.эз блоки 20 и 25 пересылаются внешнему устройству. При операции Считать байты данных из

чество используемых устройств не должно превосходить числа подканалов канала, а суммарная производительность одновременно работающих устройств не должна превышать производительности работающего канала. блока 25 через блок 17 поступают на регистр 16. После сформирования полного сло ва (или пересылки его внешнему устройству) следует модификация адреса блоком 21 модификации и запись (чтение) нового слова в (из) центральной оперативной памяти. Байт состояьшя и прерывание при работе внешнего устройства на канал I выдаются в этот канал. При наличии на регистре 12 признака работы с каналом Ц , или на регистре 13 признака неисправности канала Ц (центральной оперативной памяти) и отсутствии на регистре 19 команды, требование абонента из блока 25 транслируется через блоки 17 и 18 в каналП. По сигналу выборки адрес через блоки 17 и 18 также выдается в канал Н . Обмен дальт нейшей информацией , в том числе и прием байтов состояния через блоки 25, 17 и 18 (или блоки 18, 2О и 25 в зависимости от направления передачи информации) идет между внешними устройствами канала I и каналом П. Требование, абонента на обслуживание, поступающее от канала П через блок 23 начинает отрабатываться при отсутствии на входе блока 22 сигнала запроса абонента на обслуживание своего :комплекта внешних устройств. В блоке 23 формируется последовательность сигналов выборки и выдается в канал Н через интерфейс ввода/вывода 7, Полученный блоком 23 адрес через блок 17 пересылается на регистр 11 и из блока 24 выбирается управляющая информация. При наличии на регистре 12 признака работы с внешним устройством канала If организуется через блок 17 (или блок 20) обмен данными между регистром 16 и блоком 23.Посту-. пивший байт состояния и сигнал прерывания из блока 23 через блок 17 выдается в оперативную память и центральный процессор, с которым работает внешнее устройство. Следует заметить, что каналы позволяют организовать два независимых потока обмена информацией в следующих, двух случаях: первый централь1шй процессор (оперативная память) - канал 1 - внешние устройства канала и второй центральный процессор (оперативная память) - канал Я - внешние устройства канала Л; первый центральный процессор (оперативная память) - канал I - канал II - внещнне устройства канала Ц и второй центральный процессор (оперативная память) - канал П канал I - внешние устройства канала Т . При работе же одного из каналов с ойдим полем внешних устройств суммарное коли- изобретения Ди-льтиплексиыЯ канал многопроцессорно вычислительной системы, содержащий блок сопряжения с центральным процессором, пе{ вые вход и выход которого соединены ветственно с первыми входом и выходом канала, блок сопр51жения с центральной оперативной памятью, первый в второй входы которого подключены соответственно к втором и третьему входам канала, первый в второй выходы соединены соответственно с вторым и третьим выходакш канала, первый блок со пряжения - с внешними устройствами, первые вход и выход которого подключены соответственно к четвертым входу и выходу кан ла, регистр подканала, первый вход которог соединен с вторым выходом блсжа сопреженяя с центральным процессором, блок местной памяти, первый вход которого соединен с вторым входом блока сопряжения с централь ным процессором и выxoдo { регистра подка нала, регистр информаиии, первый вход которого пошслючен к третьему выходу блока сопряжения с центральной оперативной памятью, второй вход соединен с выходом блока местной памяти, первый выход пооключен к третьему входу блока сопряжения с центральной оперативной памятью и второму входу блока местной памяти, регистр управления, первый вход которого соединен с выходом блока местной памяти, второй вход подключен к третьему выходу блока сопряжения с центральной оперативной па мятью, первый выход соединен с вторым входом блока местной памяти, блок модификации, вход которого подключен к первому выходу регистра управления, выход соединен с четвертым входом блока сопряжения с центральной оперативной памятью, триггер монопольного режима, вход которого пооключен к второму выходу первого блока сопряжения с внешними устройствами, о iw личающийся тем, что, с целью повышения степени использования оборудования, в него введены регистр признака работы, первый вход которого соединен с вторым выходом блока сопряжения с центральным процессором, второй вход подключен к выходу блока местной памяти, регистр неисправности центральной оперативной памяти, вход которого соединен с четвертьп выходом блока сопряжения с центральной оперативной памятью, блок сопряжения СОвторым каналом, первый вход и которого подключены соответственно к пятым входу и выходу канала, второй блок сопр жения с внеишими устройствами, первый вход и выход которого соединены соответ ствонно с шестым входом и выходом канала, блок коммутации входной информации, первый вход которого подключен к третьему выходу первого блока сопряжения с внешними устройствами, второй вход соединен с вторым выходом второго блока сопряжения с внешними устройствами, выход подключен к второму входу регистра подканала, третьему входу регистра информации я второму входу блока сопряжения, с вторым каналом, блок коммутации выходной информащш, первые четыре входа которого соединены соответс- вен но с вторым выходом управления, вторым выходом регистра информации, выходом регистра подканала и вторым выходом блока сопряжения, с вторым каналом, выход подключен к третьему входу регистра подканала, второму входу первого блока сопряжения с внешними устройствами и второ{му входу второго блока сопряже|шяс внешними устройствами, блок выдачи последовательности сигналов занятого внешнего устройства, три входа JKOToporo соединены соответственно с вторым выходом регистра упраэления, вь ходом триггера монопольного режима и дом регистра пощсанала, выход подключе : к третьему входу блока коммутация входной информации, и блок определения приоритетов четыре первых входа которого подключены соответственно к второму выходу первогс блока сопряжения с внешними устройствбмв, третьему I выходу; второго блока сопряження с внешними устройствами, третьему выходу второго блока сопряжения с внешними устройствами, третьему выходу блока сопряж ния с центральным процессором в третьему выходу блока сопряжения с вторым каналом, пятый вход соединен с-1 выходами регистра прихшака работы и регистра не1асправйос « центральной оперативной памяти, выход ключен к третьему входу блока сопряжеяня с центральным процессором, третьему вход блока сопряжения с вторым каналом, четзэртому входу блока коммутации входной яяфор махши и nsrroMy входу блока коммутации к ходной информации.

i

t t «И

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Система обмена | 1978 |

|

SU809138A1 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Мультиплексный канал | 1979 |

|

SU860048A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Мультиплексный канал | 1977 |

|

SU750469A1 |

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

Авторы

Даты

1976-07-15—Публикация

1973-07-16—Подача