Изобретение относится к измерительной технике и может быть использовано для исследования физических процессов.

Известен способ регистрации однократного импульсного сигнала наносекундного диапазона, основанный на записи формы сигнала на носитель информации, например на электроннолучевую трубку, фотографировании его на фотопленку 1.

Он прост в реализации, но не обеспечивает приемлемой точности регистрации при регистрации коротких импульсов.

Наиболее близким техническим решением к предлагаемому является способ регистрации однократных импульсных сигналов наносекундного диапазона, основанный на дискретизации сигналов, запоминании, считывании и фиксации дискретных уровней. Кроме того, при регистрации сигнала по известному способу производят считывание с требуемой скоростью и получают растянутую во времени копию регистрируемого сигнала 2.

Недостатком известного способа является низкая точность регистрации, обусловленная искажением сигнала при запоминании и невозможностью «тонкой дискретизации

входного сигнала из-за возникающих отражений в линии.

Цель изобретения - повышение точности регистрации однократных импульсных сигналов наносекундного диапазона.

Эта цель достигается тем, что осуществляют функциональное преобразование дискретных уровней, запо.минание их, а затем производят обратное функциональное преобразование, восстанавливая дискретный сигнал.

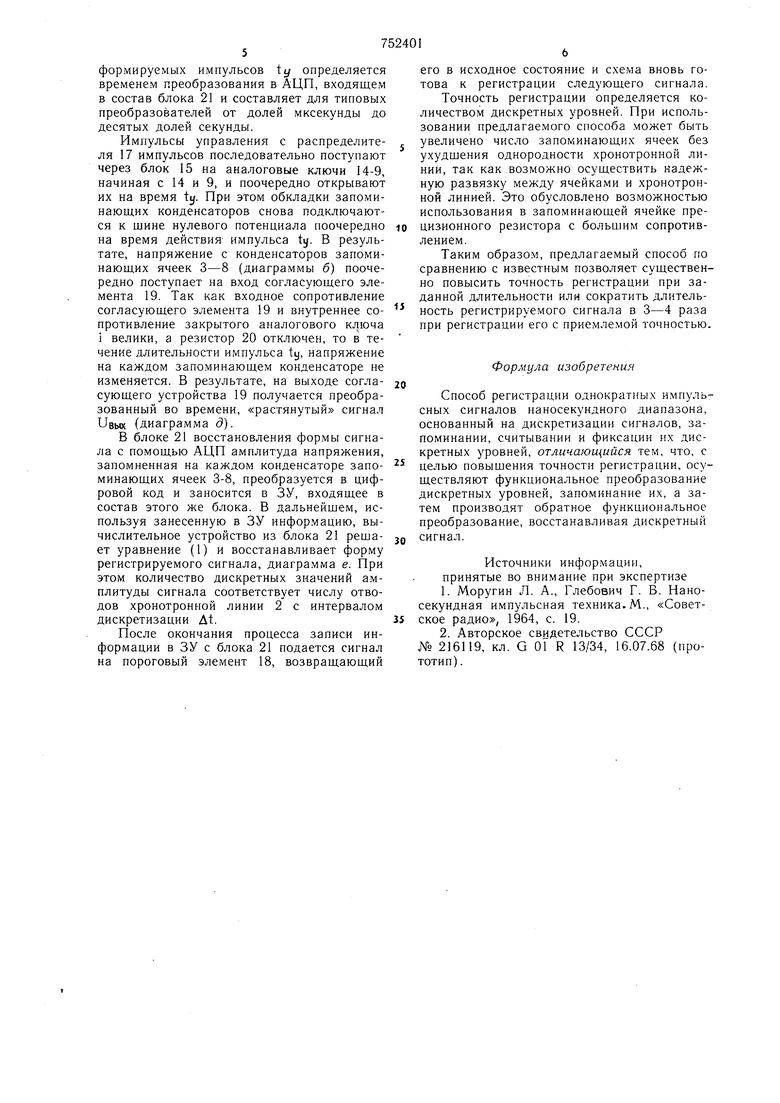

На фиг. 1 представлена функциональная

10 схема, реализующая предлагаемый способ регистрации однократных импульсов; на фиг. 2 - временные диаграммы, иллюстрирующие работу блок-схемы.

На входе функциональной схемы включен

15 аналоговый ключ 1, соединенный чере.з хронотронную линию 2 с запоминающими ячейками 3-8, каждая из которых состоит из последовательно соединенных прецизионного резистора и запоминающего конденсатора. 20 Запоминающая ячейка может быть выполнена и на других элементах, обеспечивающих запоминание и развязку линии задержки. Запоминающие ячейки 3-8 через аналоговые ключи 9-14 подключены к щине нулевого потенциала. Управление аналоговыми ключами 9-14 осуществляется сигналами с выходов соответствующих двухвходовых логических элементов ИЛИ, объединенных в логический блок 15. Одни одноименные входы логических элементов ИЛИ блока 15 объединены и подключены к управляющим входам аналоговых ключей 1 и 16. Другие входы логических элементов блока 15 подключены к блоку 17 распределения импульсов. Запускающий вход блока 17 распределения импульсов и управляющие входы аналоговых ключей 1 и 16 подключены к выходу порогового элемента 18. К выходу хронотронной линии 2 подключены входы порогового элемента 18 и согласуюа1его элемента 19. Выход хронотронной линйн 2 нагружен на резистор 20, сопротивление которого подбирается равным волновому сопротивле} ию линии 2. Резистор 20 подключен к шине нулевого потенциала через аналоговый ключ 16. К выходу согласующего элемента 19 подключен блок 21 восстановления формы регистрируемого сигнала.

Аналоговые ключи 1, 9-14 и 16 представляют собой транзисторные высокочастотные аналоговые ключи, имеющие малое внутреннее сопротивление в открытом состоянии и большое внутреннее сопротивление в закрытом состоянии. В качестве хронотронной линии 2 может быть использована, например, полосовая линия задержки с равномерно распределенными по всей длине через заданные расстояния отводами, к которым подключены запоминающие ячейки 3-8.

Входное сопротивление согласующего элемента 19 должно быть большим, так как оно определяет время хранения напряжения на конденсаторах запоминающих ячеек 3-8. В качестве согласующего блока 19 может быть использован истоковый повторитель.

Блок 21 восстановления формы сигнала включает в себя аналого-цифровой преобразователь (АЦП), запоминающее устройство (ЗУ) и вычислительное устройство, позволяющее восстановить форму регистрируемого сигнала. Выход этого блока является выходом всей блок-схемы регистрации.

Регистрация однократных импульсных сигналов осуществляется следующим образом.

Передаточная характеристика запоминающей ячейки заранее известна и такова, что напряжение регистрируемого сигнала Ugx(t), где t - временная координата, и напряжение на выходе запоминающей ячейки ивых() связаны между собой следующим соотно UBx(t)UB«x(.t «t (1),

где Т- постоянная времени цепи заряда запоминающей ячейки, превышающая длительность интервала дискретизации, определяемого требуемой точностью регистрации.

При таком соотнощении длительностей напряжения на конденсаторах запоминающих ячеек 3-8 повторяют форму входного сигнала с учетом передаточной характеристики соответствующей ячейки.

Итак, на конденсаторах запоминающих ячеек 3-8 происходит запоминание заведомо искаженного сигнала, который потом восстанавливают, используя соотношение (1).

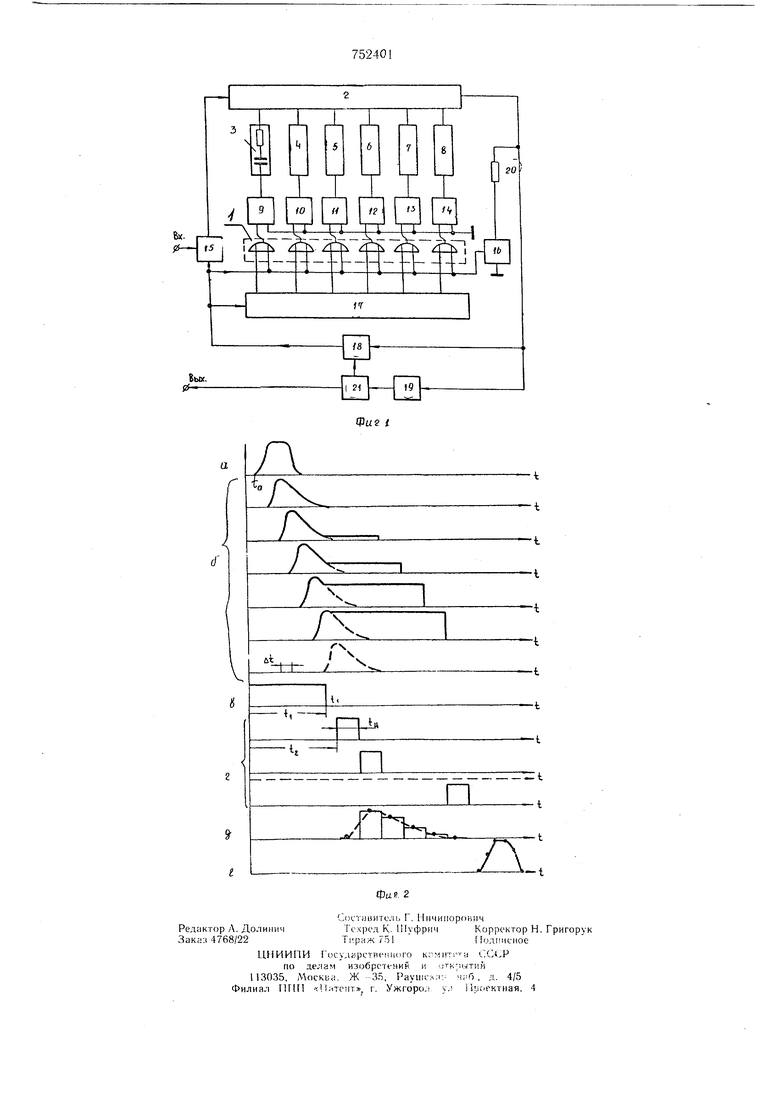

В исходном состоянии при отсутствии регистрируемого сигнала ключи 1, 9-14 и 16 открыты управляющим напряжением положительной полярности с выхода порогового элемента 18 (диаграмма в, фиг. 2), напряжения на запоминающих конденсаторах запоминающих ячеек 3-8 равны нулю, импульсы напряжения с блока 17 распределения импульсов на блок 15 логических схем не поступают. При этом запоминающие конденсаторы запоминающих ячеек 3-8 и резистор 20 через открытые ключи 9-14 и 16 подключены к щине нулевого потенциала, а вход хронотронной линии 2 задержки через открытый ключ 1 связан со входом устройства.

В мо.мент времени to регистрируемый сигнал (диаграмма а) .поступает на вход схемы, и начинает распространяться по хронотронной линии 2. Через отводы хронотронной линии 2, равномерно расположенные вдоль нее, сигнал поступает в запоминающие ячейки 3-8 через определенные иравные интервалы времени &i, диаграммы б, определяемые расстоянием между отводами хронотронной линии 2. При этом амплитуда на запоминающих конденсаторах запоминающих ячеек 3-8 в любой момент времени определяется соотнощение.м (1).

В момент времени ti передний фронт регистрируемого сигнала достигает последней ячейки 8, подключенной к последнему отводу на хронотронной линии 2.

В этот же момент срабатывает пороговый элемент 18 и с его выхода перестает поступать импульс положительной полярности, диаграмма в, управляющие напряжения на аналоговых ключах 1, 9-14 и 16 становится равным нулю, ключи закрываются и вход лронотронной линии 2 оказывается отключенным от входа схемы, запоминающие конденсаторы и резистор 20 также отключаются от шины нулевого потенциала. При этом на запоминающих конденсаторах запомина ощих ячеек 3-8 фиксируются мгновенные значения амплитуд напряжения, которые оказались на них в момент времени ti. Из сцада напряжения на пороговом устройстве 18 формируют импульс, запускаюш.ий распределитель 17 импульсов, начиная с момента tz, распределитель 17 импульсов формирует серию импульсов диаграммы г, конец каждого из которых является началом следующего, и каждый из этих импульсов последовательно поступает на соответствующий вывод распределителя 17. Длительность формируемых импульсов ty определяется временем преобразования в АЦП, входящем Б состав блока 21 и составляет для типовых преобразователей от долей мксекунды до десятых долей секунды. Импульсы управления с распределителя 17 импульсов последовательно поступают через блок 15 на аналоговые ключи 14-9, начиная с 14 и 9, и поочередно открывают их на время ty. При этом обкладки запоминающих конденсаторов снова подключаются к щине нулевого потенциала поочередно на время действия импульса . В результате, напряжение с конденсаторов запоминающих ячеек 3-8 (диаграммы б) поочередно поступает на вход согласующего элемента 19. Так как входное сопротивление согласующего элемента 19 и внутреннее сопротивление закрытого аналогового 1 велики, а резистор 20 отключен, то в течение длительности импульса ty, напряжение на каждом запоминающем конденсаторе не изменяется. В результате, на выходе согла- 20 сующего устройства 19 получается преобразованный во времени, «растянутый сигнал ивь« (диаграмма д). В блоке 21 восстановления формы сигнала с помощью АЦП амплитуда напряжения. запомненная на каждом конденсаторе запо- минающих ячеек 3-8, преобразуется в цифровой код и заносится в ЗУ, входящее в состав этого же блока. В дальнейшем, используя занесенную в ЗУ информацию, вычислительное устройство из блока 21 реша- jg ет уравнение (1) и восстанавливает форму регистрируемого сигнала, диаграмма е. При этом количество дискретных значений амплитуды сигнала соответствует числу отводов хронотронной линии 2 с интервалом дискретизации At. После окончания процесса записи информации в ЗУ с блока 21 подается сигнал на пороговый элемент 18, возвращающий 35 его в исходное состояние и схема вновь готова к регистрации следующего сигнала. Точность регистрации определяется количеством дискретных уровней. При использовании предлагаемого способа может быть увеличено число запоминающих ячеек без ухудшения однородности хронотронной линии, так как возможно осуществить надежную развязку между ячейками и хронотронной линией. Это обусловлено возможностью использования в запоминающей ячейке прецизионного резистора с большим сопротивлением. Таким образом, предлагаемый способ по сравнению с известным позволяет существенно повысить точность регистрации при заданной длительности или сократить длительность регистрируемого сигнала в 3-4 раза при регистрации его с приемлемой точностью. Формула изобретения Способ регистрации однократных импульсных сигналов наносекундного диапазона, основанный на дискретизации сигналов, запоминании, считывании и фиксации их дискретных уровней, отличающийся тем, что, с целью повышения точности регистрации, осуществляют функциональное преобразование дискретных уровней, запоминание их, а затем производят обратное функциональное преобразование, восстанавливая дискретный сигнал. Источники информации, принятые во внимание при экспертизе 1. Моругин Л. А., Глебович Г. В. Наносекундная импульсная техника. М., «Советское радио, 1964, с. 19. 2. Авторское свидетельство СССР № 216119, кл. G 01 R 13/34, 16.07.68 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ХРОНОТРОННО-СТРОБОСКОПИЧЕСКОЙ РЕГИСТРАЦИИ ОДНОКРАТНЫХ ИМПУЛЬСНЫХ ПРОЦЕССОВ | 1966 |

|

SU216119A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU960957A1 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1990 |

|

SU1758576A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU832602A1 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1989 |

|

SU1624346A1 |

| Устройство для регистрации формы повторяющихся сигналов наносекундной длительности | 1972 |

|

SU501362A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881864A1 |

| Многоканальное устройство для регистрации сигналов | 1987 |

|

SU1439675A1 |

| Устройство для регистрации информации | 1979 |

|

SU868688A1 |

| Устройство для регистрации информации | 1985 |

|

SU1308839A1 |

Авторы

Даты

1980-07-30—Публикация

1974-12-20—Подача