сл

4i

СО

со

О)

sj

сл

r«tW /±yrt 70 f±

.жJ.. Фиг.}

этом сигнал Пуск через переключатель 24 поступает на вход запуска формирователя одиночных импульсов 15, который сбрасывает состояния триггеров 11, 12, 13 и устанавливает счетчики 29, 30 в начальное состояние, определяемое соответствзпощими выходами кодов постоянных запоминающих устройств 21J 22. Логическая схема 27 формирует сигналы управления состоянием устройства и разрешения счета счетчиков 9, 10, Затем выходные импульсы таймера 8 поступают на вход запуска блока синхронизации 7, который формирует последовательно во времени импульсы на первом, втором и четвертом входах. Данная последовательность импульсов обеспечивает выборку, преобразование и запоминание мгновенных значений входного, сигнала, 1.При этом кодирование мгновенных значений сигналов осуществляется только в тех каналах, где вкл19чены переключатели в блоке 16 включения каналов. В зависимости от числа включенных каналов сумматор 19 формирует соответствующий код, который поступает на адресные входы постоянных запоминающих устройств 20-22 и коммутатора 18. После того, как триггеры 12 и 13 установятся в 1, устройство переходит в режим вывода информации. Соответствующее состояние устройства индицируется в индикаторе состояния 28. При этом в режиме ввода информации блок 5 интерполирующих устройств восстанавливает сигналы в виде непрерывных функций, которые регистрируются устройством 6, В качестве регистрирующего устройства может быть использован многоканальный самопишущий прибор. 5 ил.5 5 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Многоканальное устройство для регистрации и индикации мгновенных значений сигналов | 1985 |

|

SU1312391A1 |

| Устройство для контроля параметров двигателя внутреннего сгорания | 1988 |

|

SU1733946A1 |

| Устройство для выделения импульсов синхронизации | 1978 |

|

SU785977A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Функциональный генератор | 1984 |

|

SU1267395A1 |

| Устройство для управления частотно-регулируемым трехфазным инвертором | 1984 |

|

SU1365305A1 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

Изобретение относится к измерительной технике, может быть использовано для регистрации быстропротека- клцих процессов и позволяет расширить функциональные возможности многоканальных самопишущих приборов. Устройство- может работать в режимах однократного или непрерывного запуска, соответственно верхнее или нижнее положение переключателей 24, 25 При

1

Изобретение относится к измерительной регистрирующей технике и может быть использовано для регистрации быстро протекающих процессов (например, переходных) с преобразовани- ем масштаба времени при помощи многоканальных самопишущих приборов.

Целью изобретения является расширение функциональных возможностей путем управления длительностью интервала регистрации и количеством одновре менно работаюш51Х каналов, что способствует расширению частного диапазона и увеличению длительности интервалов времени, в которых регистрируются сигналы.

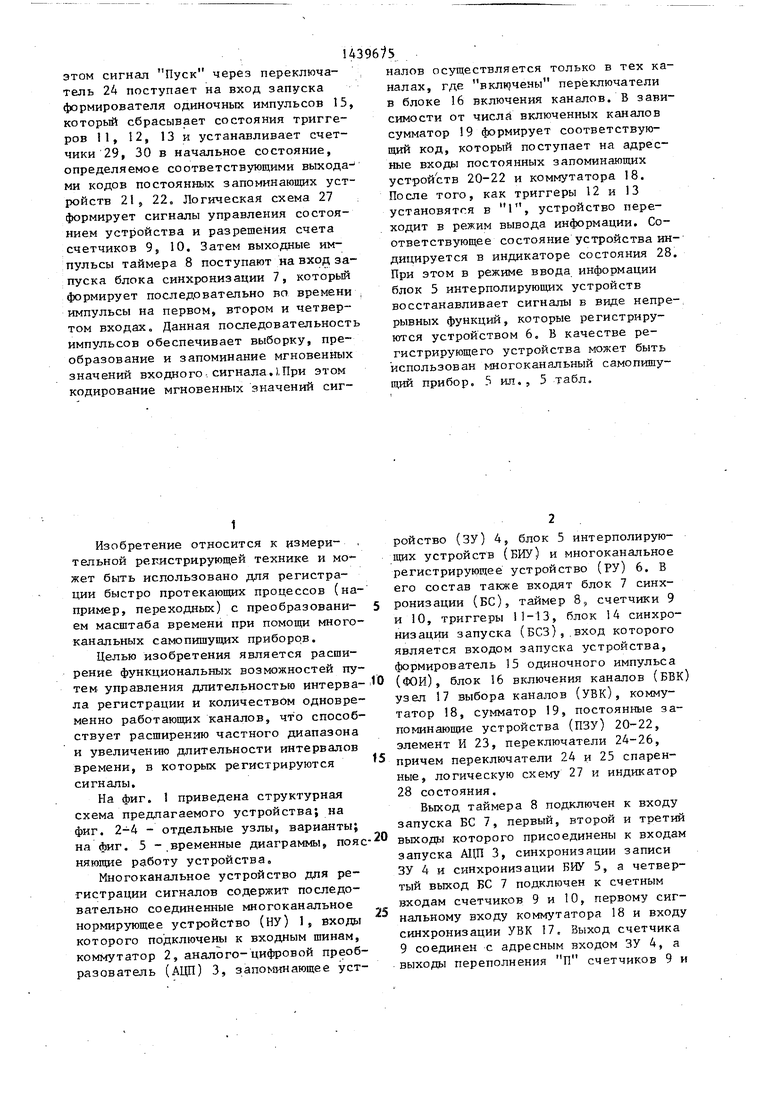

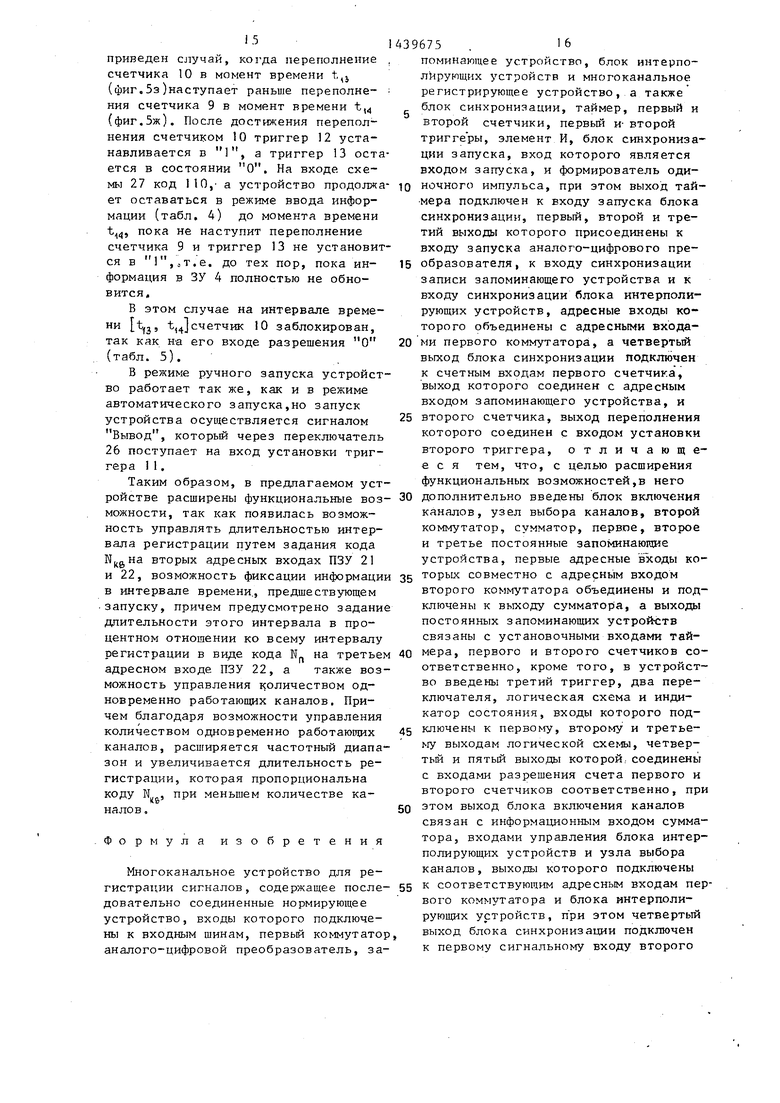

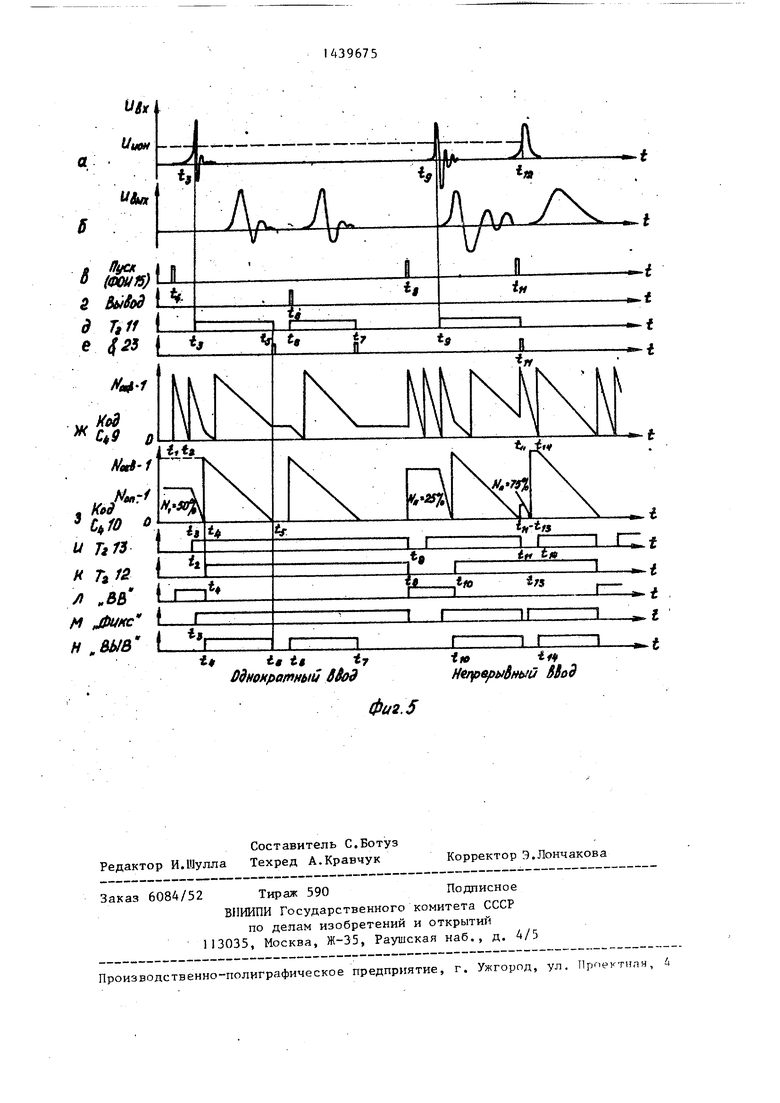

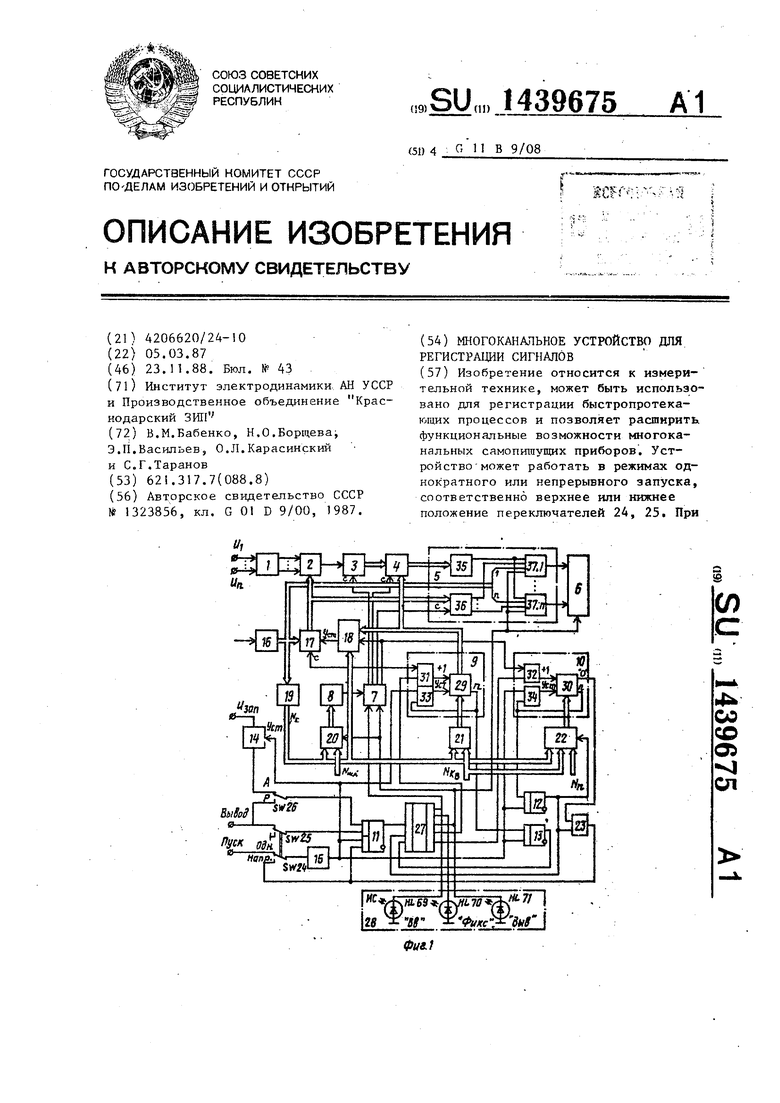

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2-4 - отдельные узлы, варианты; на фиг. 5 -.временные диаграммы, пояс няющие работу устройства.

Многоканальное устройство дпя регистрации сигналов содержит последовательно соединенные многоканальное нормирующее устройство (НУ) 1, входы которого подключены к входным щинам, коммутатор 2, аналоге-цифровой преобразователь (АЦП) 3, запоминающее устройство (ЗУ) 4, блок 5 интерполирующих устройств (БИУ) и многоканальное регистрирующее устройство (РУ) 6. В его состав также входят блок 7 синхронизации (БС), таймер В, счетчики 9 и 10, триггеры П-13, блок 14 синхронизации запуска (БСЗ),.вход которого является входом запуска устройства, формирователь 15 одиночного импульса (ФОИ), блок 16 включения каналов (БВК узел 17 выбора каналов (УВК), коммутатор 18, сумматор 19, постоянные за- поминаюшле устройства (ПЗУ) 20-22, элемент И 23, переключатели 24-26, причем переключатели 24 и 25 спаренные, логическую схему 27 и индикатор 28 состояния.

Выход таймера 8 подключен к входу запуска БС 7, первый, второй и третий выходы которого присоединены к входам запуска АЦП 3, синхронизации записи ЗУ 4 и синхронизации БИУ 5, а четвертый выход БС 7 подключен к счетным входам счетчиков 9 и 10, первому сигнальному входу коммутатора 18 и входу синхронизации УВК 17, Выход счетчика 9 соединен с адресным входом ЗУ 4, а выходы переполнения П счетчиков 9 и

3

10 подключены к входам установки триггеров 13 и 12 соответственно.Первые адресные входы ПЗУ 20-22 совместно с адресным входом коммутатора 18 объединены и подключены к выходу сумматора 19, Выходы ПЗУ 20-22 связаны установочными входами таймера 8 и сччиков 9 и 10 соответственно. Входы индикатора 28 состояний подключены к первому, второму и третьему выходам логической схемы 27, четвертый и пятый вьЕходы которой соединены с входами разрешения счета счетчиков 9 и 10 соответственно. Выход БВК 16 связан с информационньш входом сумматора 1 9 и входами управления БИУ 5 и УВК 17, Выход последнего подключен к объединенным между собой адресным входам коммутатора 2 и БИУ 5. Вход установки УВК 17 соединен с выходом Уст, коммутатора 18, вторые сигналные входы которого подключены к нескольким млад1чим разрядам счетчика 9, На вторые адресных входах ПЗУ 20 объединенных адресных входах ПЗУ 21 и .2 и третьем адресном входе ПЗУ 22 установлены соответственно коды

шага дискретизации Нщд, количества выборок NHJ и процент количества выборок регистрируемых в интервале времени, предшествующем моменту запуска N. Прямой выход триггера 12 соединен с четвертым адресным входом ПЗУ 22 и первым входом элемента И 23, Второй вход последнего соединен с выходом состояния нуля счетчика 10, а выход элемента 23 подключен к первому входу сброса триггера 11, а через переключатель 24, второй вход которого соединен с шиной Пуск, - к входу ЮИ 15, Выход последнего связан с вторым входом сброса триггера 11, входами сброса триггеров 12 и 13 и входами установки БСЗ 14 и счетчиков 9 и 0, Шина Вывод через переключатель 25 соединена с первым входом установки триггера 11, а чере переключатель 26, другой вход которого подключен к выходу БСЗ 14, под- кпюченя K.BTopoNry входу установки триггера 11. Выходы триггеров 11-13 соединены с входами логической схемы 27. Первый и третий выходы схемы 27 подключены к входам управления БС 7, причем третий выход схемы 27 подключен также к третьему адресному входу ПЗУ 20 и входам блокировки БИУ 5 и РУ 6,

10

, 15

0

25

30

Счетчики 9 и 10 построены по идентичным схемам и каждый из них содержит вычитающий счетчик 29 (ЗО), элемент И 31 (32) и элемелт ИЛИ 33 (ЗА). Выход элемента И 31 (32), входы кото- рсго являются счетным входом и входом разрешения счета счетчика 9 (Ю), подключен к счетному входу счетчика 29 (ЗО), вход синхронизации яаписи которого соединен с выходом элемента ИЛИ 33 (34), один из входов которого соединен с выходом П переполнения счетчика 29 (30), а другой вход является входом установки счетчика 9 (10).

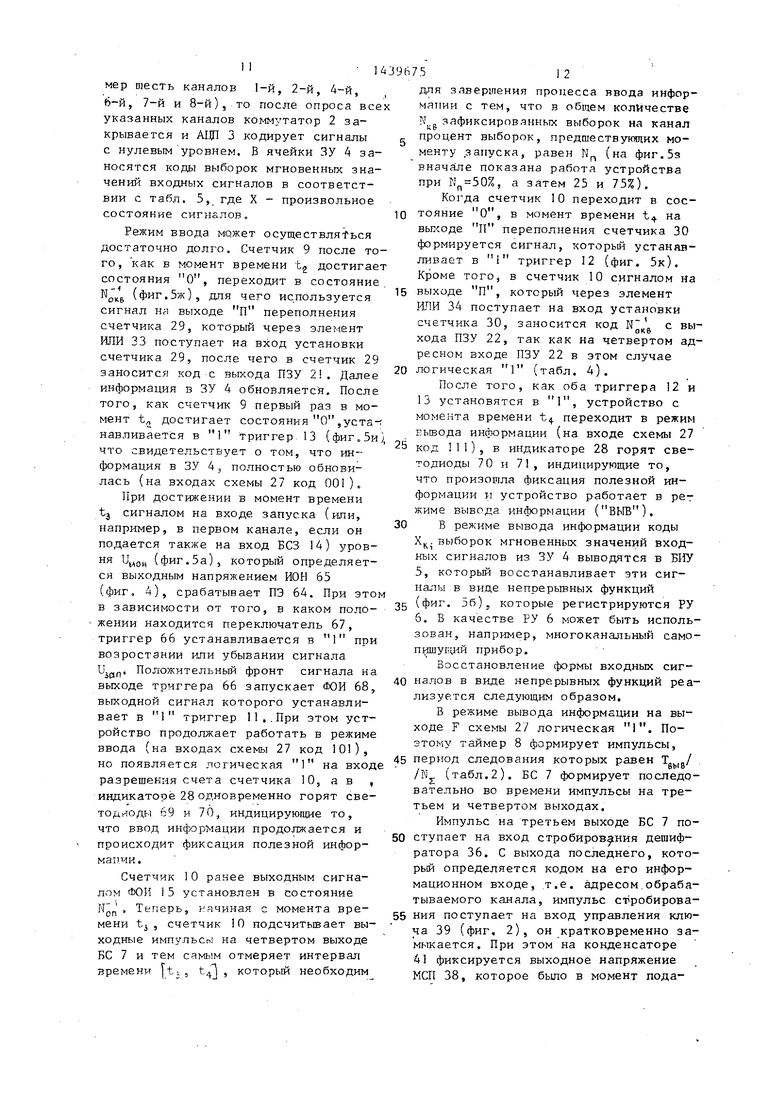

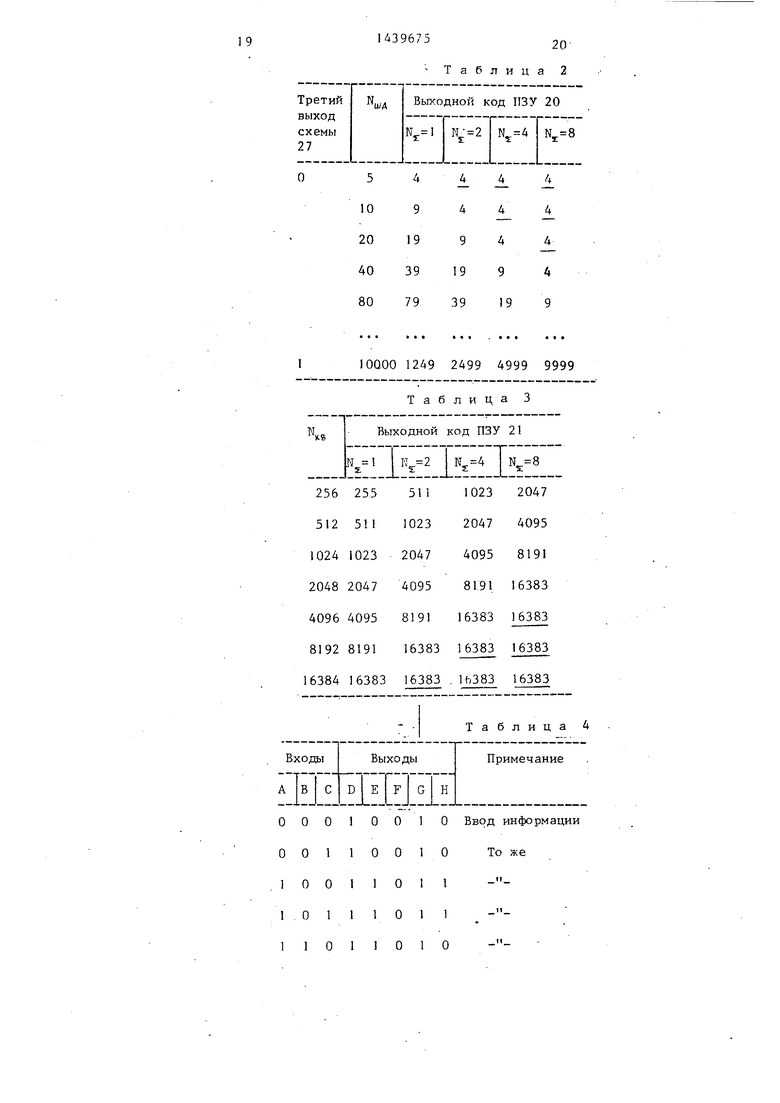

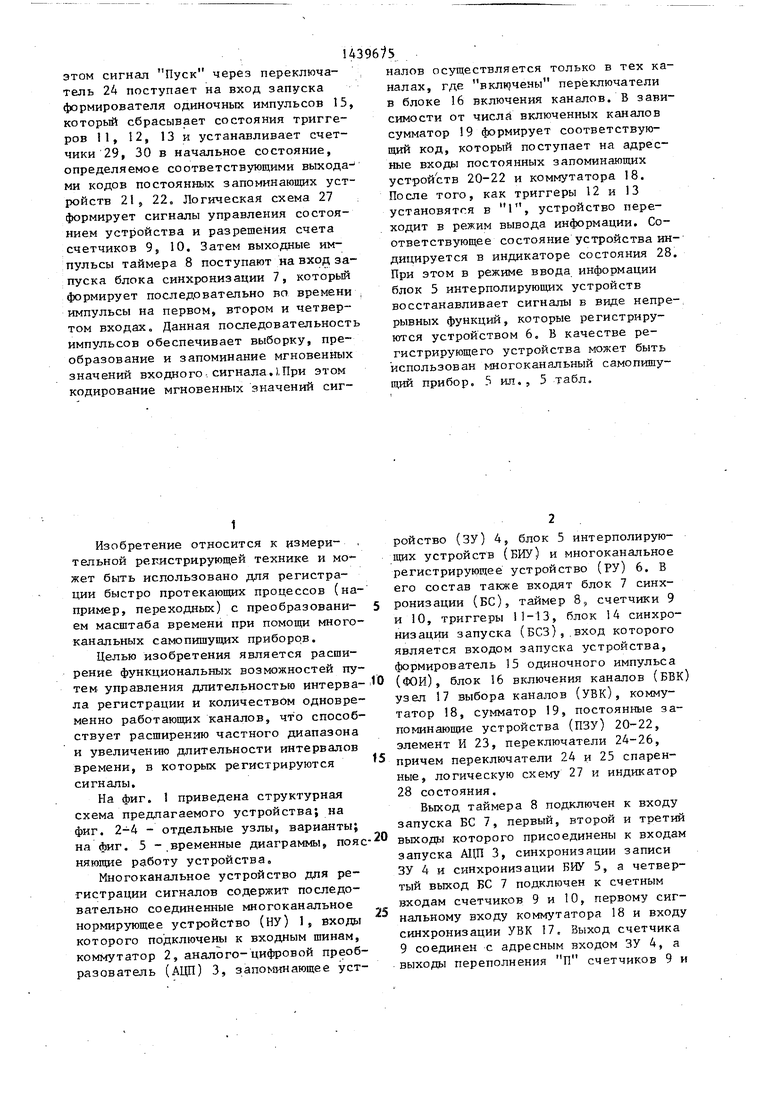

БИУ 5 содержит цифроаналоговый пре- образователь (ЦАП) 35, вход которого - является информационным входом БИУ 5, дешифратор 36, информационный вход которого является адресным входом БИУ 5, а его вход стробирования- входом синхронизации БИУ 5 и п аналоговых интерполирующих устройств (ИУ) 37,1-37.п, выходы которых являются выходами БИУ 5. Сигнальные входы ИУ.37.1-37,п объединены и подключены к выходу ЦАП 35, входы синхронизации ИУ 37.1 и 37.п подключены к выходам дешифратора 36, их первые входы разрешения являются входами управления БИУ 5 и соединены с выходом БВК 16, а вторые входы разрешения объединены и являются входом блокировки БИУ 5, который подключен к

35 третьему выходу схемы 27.

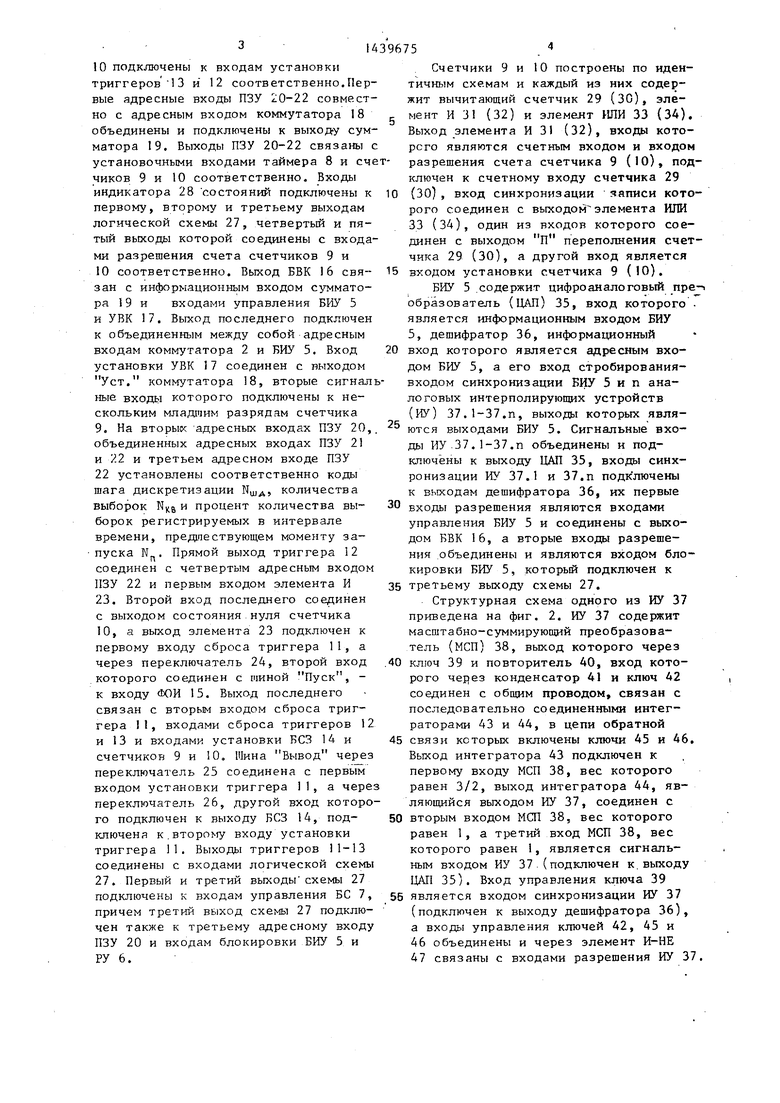

Структурная схема одного из ИУ 37 приведена на фиг, 2, ИУ 37 содержит масштабно-суммирующий преобразователь (МСП) 38, выход которого через

40 клгоч 39 и повторитель 40, вход которого через конденсатор 41 и ключ 42 соединен с обшлм проводом, связан с последовательно соединенными интеграторами 43 и 44, в цепи обратной

45 связи которых включены ключи 45 и 46. Выход интегратора 43 подключен к первому входу МСП 38, вес которого равен 3/2, выход интегратора 44, являющийся выходом ИУ 37, соединен с

50 вторым входом МСП 38, вес которого равен 1, а третий вход МСП 38, вес которого равен 1, является сигнальным входом ИУ 37 (подключен к.выходу liATl 35), Вход управления ключа 39

55 является входом синхронизации ИУ 37 (подключен к выходу дешифратора 36), а входы управления ключей 42, 45 и

46объединены и через элемент И-НЕ

47связаны с входами разрешения ИУ 37,

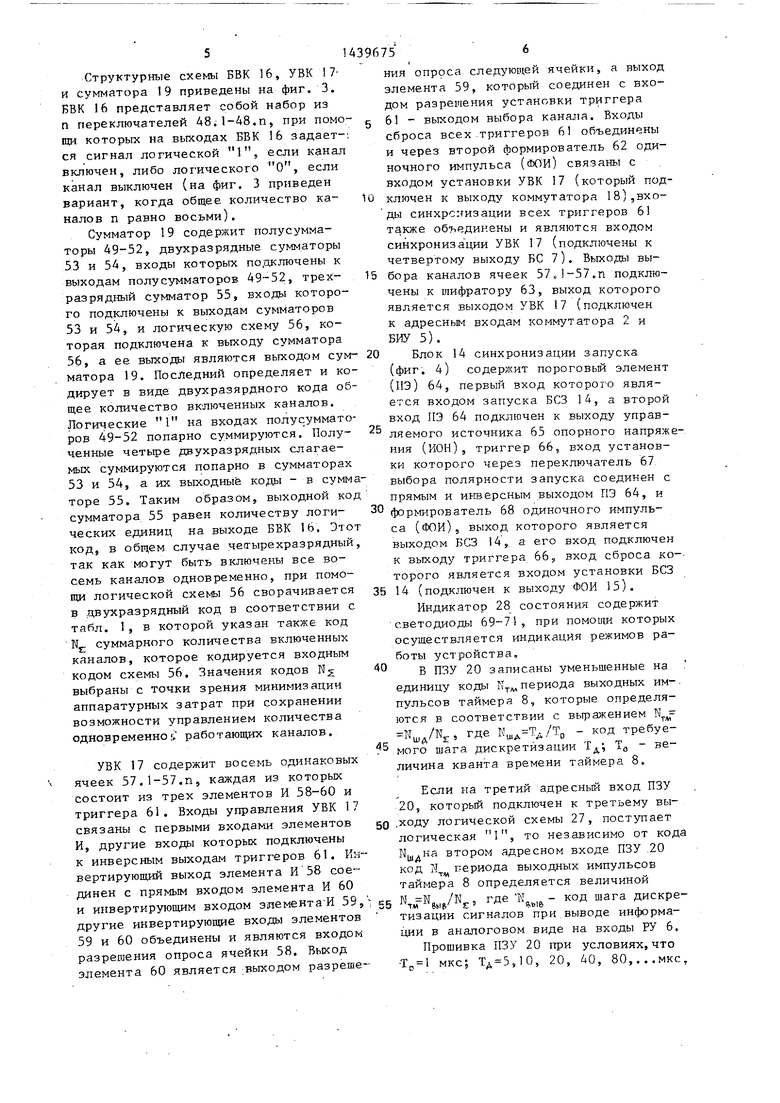

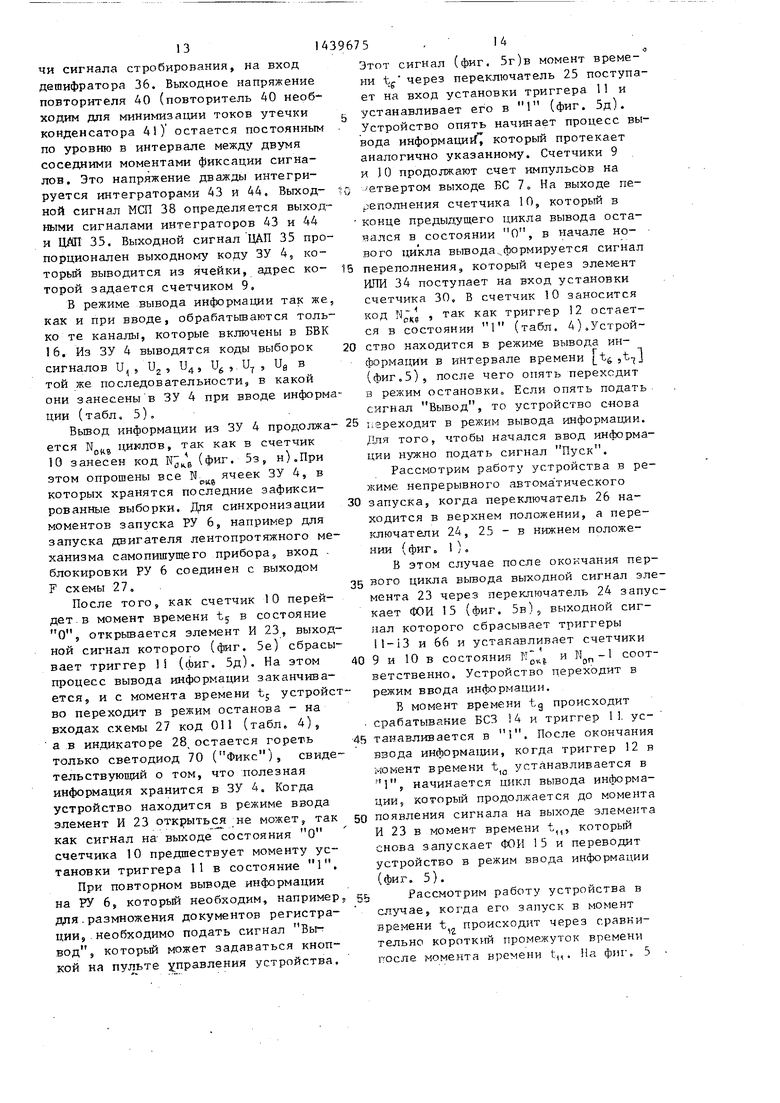

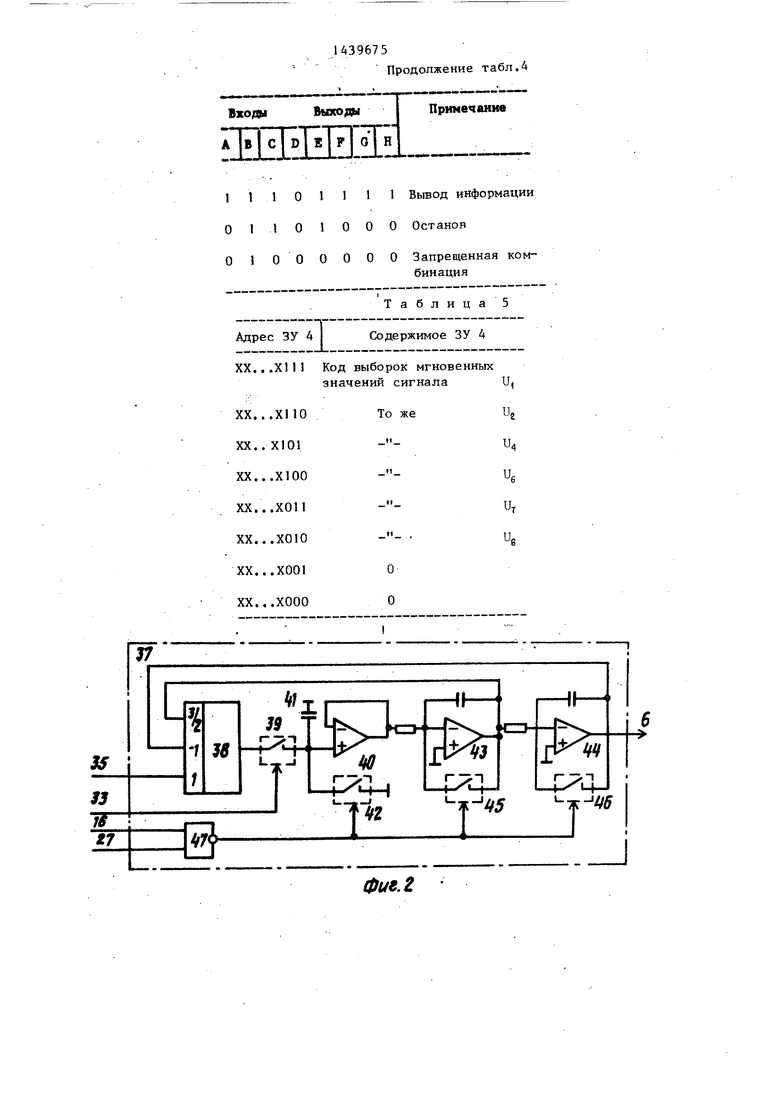

Структурные схемы БВК 16, УВК 17- и сумматора 9 приведены на фиг. 3. БВК 16 представляет собой набор из п переключателей AS.l-AS.n, при помо- 1ЦИ которьпх на выходах БВК 16 задает-; ся сигнал логической 1, если канал включен, либо логического О, если канал выключен (на фиг. 3 приведен вариант, когда общее количество каналов п равно восьми).

Сумматор 19 содержит полусумматоры 49-52, двухразрядные сумматоры 53 и 54, входы которых подалючены к выходам полусумматоров 49-52, трехразрядный сумматор 55, входы которого подключены к выходам сумматоров 53 и 54, и логическую схему 56, которая подключена к вькоду сумматора 56, а ее выходы являются выходом сум- матора 19. Последний определяет и кодирует в виде двухразярдного кода общее количество включенных каналов.

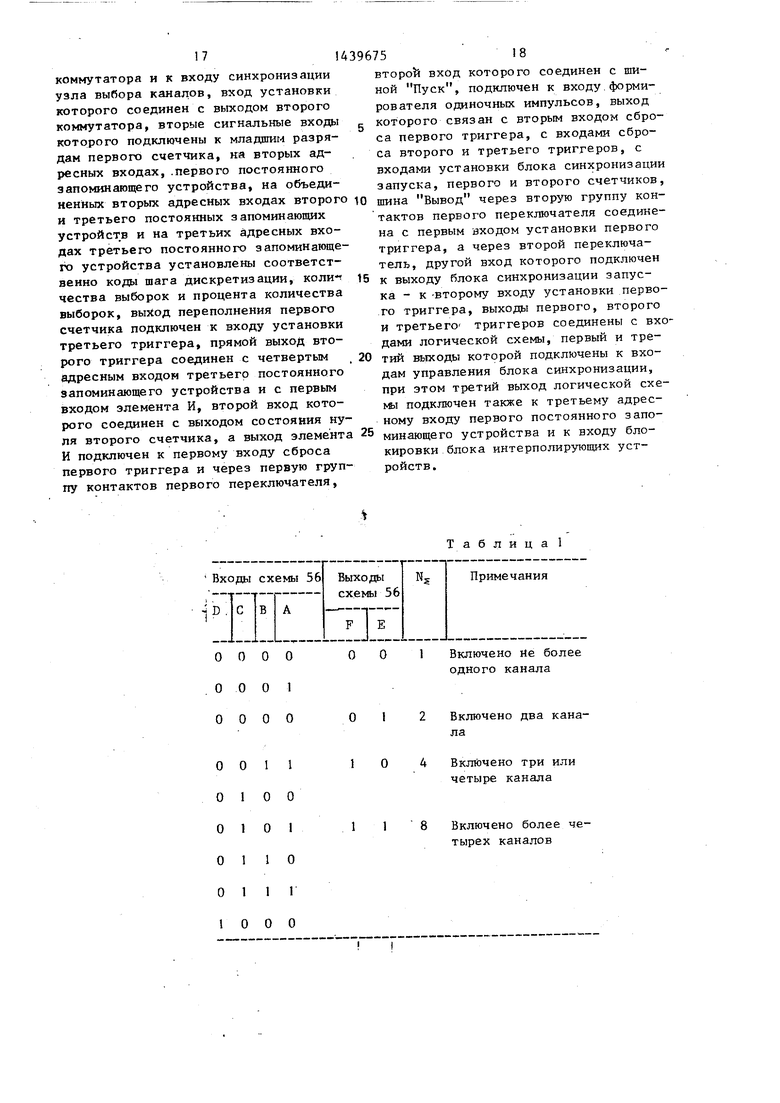

Логические 1 на входах полусумматоров 49-52 попарно суммируются. Полученные четыре рэухразрядных слагаемых суммируются попарно в сумматорах 53 и 54, а их выходные коды - в суммторе 55. Таким образом, выходной ко сумматора 55 равен количеству логических единиц на выходе БВК 16. Это код, в общем случае четырехразрядный так как могут быть включены все восемь каналов одновременно, при помощи логической схемы 56 сворачивается в двухразрядный код в соответствии с табл. 1, в которой указан также код NJ. суммарного количества включенных каналов, которое кодируется входным кодом схемы 56. Значения кодов N выбраны с точки зрения минимизации аппаратурных затрат при сохранении возможности управлением количества одновременного работающих каналов.

УВК 17 содержит восемь одинаковых ячеек 57.1-57.п5 каждая из которых состоит из трех элементов И 58-60 и триггера 61. Входы управления УВК 17 связаны с первыми входами элементов И, другие входы которых подключены к инверсным выходам триггеров 61. Инвертирующий выход элемента И 58 соединен с прямым входом элемента И 60

и инвертирующим входом злемента И 59,

другие инвертирующие входы элементов 59 и 60 объединены и являются входом разрешения опроса ячейки 58. Выход элемента 60 является выходом разреше

0

опроса следующей ячейки, а выход элемента 59, который соединен с входом разрешения установки триггера 61 - выходом выбора канала. Входы сброса всех триггеров 61 объединены и через второй формирователь 62 одиночного импульса (ОИ) связаны с входом установки УВК 17 (который под- 0 ключен к выходу коммутатора 18),входы синхронизации всех триггеров 61 также объединены и являются входом синхронизаЧщи УВК 17 (подключены к четвертому выходу БС 7). Выходы вы- 5 бора каналов ячеек 57J-57.п подключены к шифратору 63, выход которого является выходом УВК 17 (подключен к адресным входам коммутатора 2 и БИУ 5).

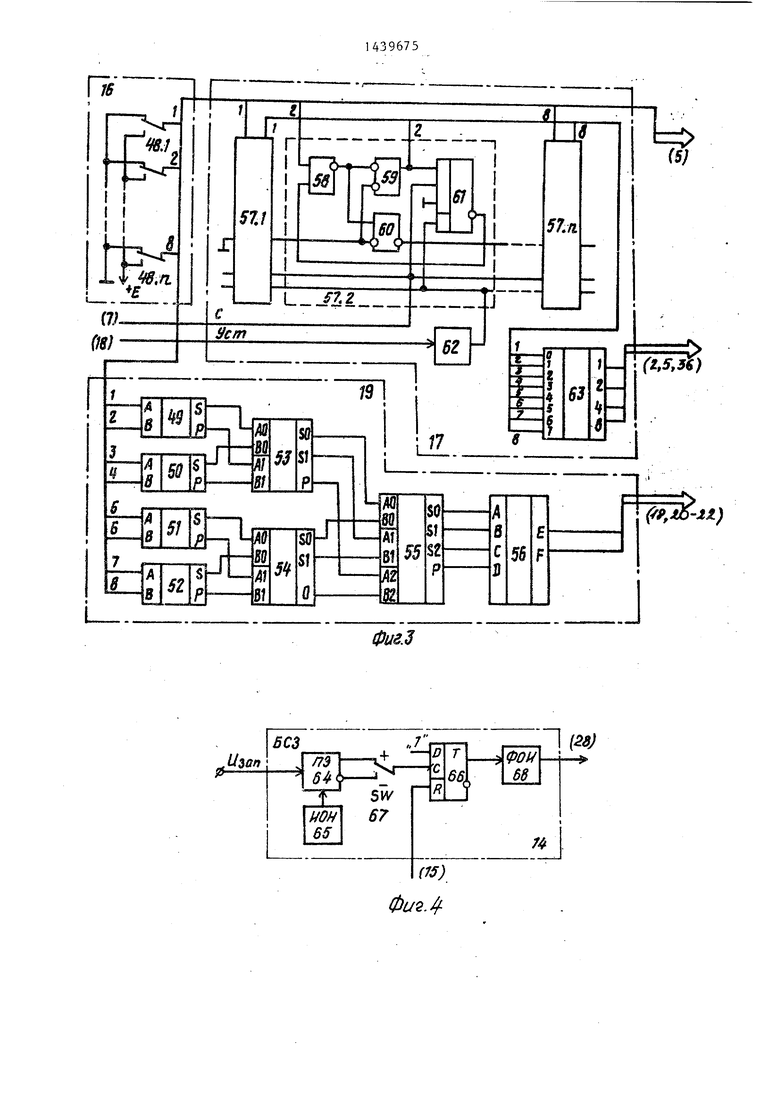

Блок 14 синхронизации запуска (фиг. 4) содержит пороговьй элемент (из) 64, первый вход которого является входом запуска БСЗ 14, а второй вход ПЭ 64 подключен к выходу управляемого источника 65 опорного напряжения (ион)5 триггер 66, вход установки которого через переключатель 67. выбора полярности запуска соединен с прямым и инверсным выходом ПЭ 64, и формирователь 68 одиночного импульса (ФОИ), выход которого является выходом БСЗ 14, а его вход подключен к выходу триггера 66, вход сброса ко- торого является входом установки БСЗ 5 14 (подключен к выходу ФОИ 15.

Индикатор 28 состояния содержит светодиоды 69-71, при помощи которых осуществляется индикация режимов работы устройства,

В ПЗУ 20 записаны уменьшенные на единицу коды N периода выходных им-- пульсов таймера 8, которые определяются в соответствии с выражением шА Тд/TO - код требуемого шага дискретизации Тд - величина кванта времени таймера 8.

5

0

5

Если на третий адресный вход ПЗУ 20, который подключен к третьему вы- 50 .ходу логической схемы 27, поступает логическая 1, то независимо от кода втором адресном входе ПЗУ .20 код N периода выходных импульсов таймера 8 определяется величиной

,/К.

где - код шага дискретизации сигналов при.выводе информации в аналоговом виде на входы РУ 6. Прошивка ПЗУ 20 при условиях, что Tj, l мкс; Тд 5,10, 20, 40, 80,...мкс,

т 1

Bbift

7

мс, приведена в табл. 2, где выходные коды ПЗУ 20 представлены десятичной системе.

Минимальная величина периода выходных импульсов таймера 8 условно выбрана 5 мкс и определяется соотно шением Т,,+ „ где 1,1,5 м длительность переходных процессов в коммутаторе ,г,1 икс - время

2;-Лцп 1

преобразования АПП 3; t jya t,5 мкс длительность цикла обращения к ЗУ Д В тех случаях, когда расчетное значение периода выходных импульсов тамера 8 меньше Тр, в ПЗУ 20 кодируется минимально допустимое значение Tjj (подчеркнутые доды в табл. 2). В ПЗУ 21 записаны уменьшенные на

Сигнал Пуск, который может за- 15 даваться кнопкой на пульте управления устройства, через переключатель. 24 поступает на вход запуска ФОН 15, который в момент времени t , формирует импульс (фиг. 5в), сбрасьгоающий

единицу коды общего количества регистрируемых выборок , которые опреде- 20 триггеры 11-13 и 66 и устанавливай- ляются как произведение кода щ„й счетчики 29 и 30 в состояния, количества выборок КБ, приходящихся на один канал, и кода суммарного количества включенных каналов. Последторые определяются выходными кодами okl оп 21 и 22 соответственно. Коды на выходах счетчиков 29 и 30 V соответственно. При помощи логической схемы 27 формируются сигналы управления состоянием устройства (выходы D, Е, Г)и сигналы разрешения счета счетчиков 9 и 10 (выходы G, Н). Схема 27 может быть реализована при помощи микросхемы ПЗУ, прошитой в соответствии с табл. 4,

ний код Ng- снимается с выхода сумма- тора 19. Вариант прошивки ПЗУ 21 для случая, когда суммарное количество включенных каналов кодируется в соответствии с табл. 1 , а объем ЗУ 4 ограничен 2 ячей.:ами (16, К) , приведен в табл. 3, где выходные коды ПЗУ 21 представлены в десятичной системе. Общее количество выборок не может

г-о

попревышать объем ЗУ 4, этому в тех случаях, когда расчетное значение кода Nong больше V, в ПЗУ .21 кодируется максимально допустимое значение кода (подчеркнутые коды в т абл. 3).

В ПЗУ 22 записаны уменьшенные на единицу коды Ngr, общего количества вы- борок, регистрируемых в интервале времени, предьчествующем моменту фиксации, которые определяются как произведение - кодов N

кв

., (1 00-Nn) N. N - код процента количества выборок, регистрируемых в интервале времени, предшествующем моменту запуска. Эти коды выводятся из ПЗУ 22 только в том случае, если сигнал на его четвертом адресном входе, подключенном к выходу триггера 12, принимает значение логического О, В противном случае, если триггер 12 установлен в 1, с выхода ПЗУ 22 снимается уменьшенный на единицу код Кр „общего количества выбо

рок, равный произведению кодов N.

независимо от значения кода И„.

Устройство может работать в нескольких режимах: однократного или непрерывного запуска (соответственно, верхнее или нижнее на фиг. 1 положение переключателей 24 и 25), автоматического или ручного запуска (верхнее или нижнее положение переключателя 26).

Рассмотрим режим однократного ав томатического запуска.

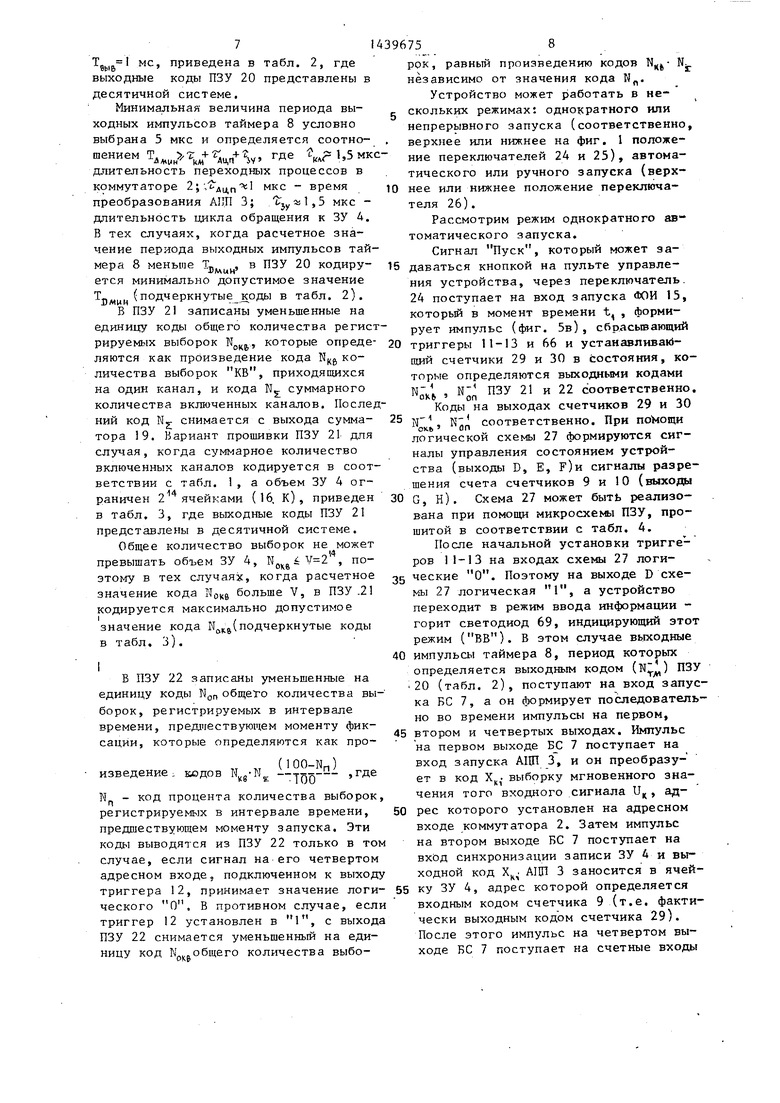

Сигнал Пуск, который может за- 5 даваться кнопкой на пульте управления устройства, через переключатель. 24 поступает на вход запуска ФОН 15, который в момент времени t , формирует импульс (фиг. 5в), сбрасьгоающий

0 триггеры 11-13 и 66 и устанавливай- щ„й счетчики 29 и 30 в состояния, ко20 триггеры 11-13 и 66 и устанавливай- щ„й счетчики 29 и 30 в состояния, ко25

30

торые определяются выходными кодами okl оп 21 и 22 соответственно. Коды на выходах счетчиков 29 и 30 V соответственно. При помощи логической схемы 27 формируются сигналы управления состоянием устройства (выходы D, Е, Г)и сигналы разрешения счета счетчиков 9 и 10 (выходы G, Н). Схема 27 может быть реализована при помощи микросхемы ПЗУ, прошитой в соответствии с табл. 4,

После начальной установки триггеров 11-13 на входах схемы 27 логи35 ческие О. Поэтому на выходе D схемы 27 логическая 1, а устройство переходит в режим ввода информации - горит светодиод 69, индицирующий этот режим (ВВ). В этом случае вьрсодные

40 импульсы таймера 8, период которых определяется выходным кодом (W) ПЗУ 20 (табл. 2), поступают на вход запуска БС 7 , а он формирует последовательно во времени импульсы на первом,

45 втором и четвертых выходах. Импульс на первом выходе БС 7 поступает на вход запуска А1Щ 3, и он преобразу- ет в код выборку мгновенного значения того входного сигнала U, ад50 рее которого установлен на адресном входе коммутатора 2. Затем импульс на втором выходе БС 7 поступает на вход синхронизации записи ЗУ 4 и выходной код Х| АЦП 3 заносится в ячей55 ку ЗУ 4, адрес которой определяется входным кодом счетчика 9 (т.е. фактически выходным кодом счетчика 29). После этого импульс на четвертом выходе БС 7 поступает на счетные входы

914

счетчиков 9 и 10 (первые входа элементов И 31 и 32) и вход синхронизации УВК 17. Однако счет этих импульсов осуществляется только счетчиком 9, так как на его входе разрешения счета логическая I (сигналы на выходе G схемы 27)5а счетчик 10 хранит свое прежнее состояние, так как на его входе разрешения счета логич.еский О - сигнал на выходе Н схемы 27 (табл. 4)

После этого устройство переходит к кодированию выборки мгновенного значения сигнала в следующем канале.При этом кодирование мгновенных значений сигналов осуществляется не во всех каналах, а только в тех, которые включены при помощи переключателей 48 в

Если включено два канала, например второй и пятый, то на выходе сумматора 19 формируется код 01 (табл.), а через -оммутатор 18 на вход установки УВК 17 поступает сигнал с самого мпадшего разряда О счетчика 9. На положительном фронте этого сигна- 15 ла выходным импульсом ФОН 62 все триггеры 61 УВК 17 сбрасываются. На Свходы синхронизации триггеров 61 поступает импульс с четвертого выхода БС 7. Однако вначале он изменить

БВК (фиг. 3).

Выбор адресов каналов, код которых 20 состояние триггеров 16 не может, так формируется на выходе УВК 17, осуще-как установка триггеров по входу С

ствляется следующим образом.

В зависимости от того, сколько каналов включено, сумматор 19 формирует соответствующий код (табл. 1), который поступает на первые адресные входы ПЗУ 20-22 и коммутатора 18. При этом, если включен только один канал, коммутатор 18 пропускает на вход ус2Б

возможна только на положительном фронте импульса при условии9 что на

входе разрешения установки I логичес- II111

кая 1, а сигнал на асинхронном входе R сброса триггеров имеет достаточную длительность, чтобы удержать триггеры 61 в сброшенном состоянии. Так же, как и в указанном случае, тановки УВК 17 сигнал с четвертого вы-30 сначала на выходе элемента 59 ячеи- хода БС 7. Положительный фронт этого ки 57.2 логическая 1, которая в

шифраторе 63 преобразуется в двоичньй код 001 адреса второго канала. Однако после прихода следующего импульса 35 на вход синхронизации УВК 17 (входы С триггеров 61) только триггер 61 в ячейке 57,2 устанавливается в 1,

сигнала запускает ФОИ 62, выходной сигнал которого сбрасывает все триггеры 6 1 в ячейках 57. На входе управления УВК 17 (например, на втором), для которого включен соответствующий

канал, логическая 1, она на выходе элемента И 58 инвертируется (-триггер 61 находится в состоянии О, поэтому на его инверсном выходе 1),со- ответственно, элемент И 60 закрьшает- ся (на его выходе разрешения опроса следующей ячейки 1), поэтому выходные сигналы всех элементов 60 в

так как на его входе I 1 с выхода элемента 59. При этом в ячейке 57,2 40 элемент И 58 закрьшается, на выходе Элемента 59 устанавливается О и появляется возможность распространения логического О через элемент 60. Этот О беспрепятственно проходит

ячейках 57, следующих за ячейкой 57,2,45 через элементы 60 в третей и четвер

той ячейкахi так как на их входы управления поступают О с выхода БВК 16, а на выходе элемента 59 ячейки 57.5 устанавливается 1, которая

50 в шифраторе 63 преобразуется в двоичный код 100 адреса пятого канала.Ес- ли включено три или четыре канала, то запуск УВК 17 осуществляется по- ; ложительным фронтом сигнала на нуле55 вом выходе счетчика 9, а если включено более четырех каналов - то сигналом на нулевом выходе счетчика 9. В том случае, если включено число каналов, не равное степени два, напри10

тольк о один канал, то код его адреса постоянно формируется на выходе УВК 17, а ЗУ 4 заполняется кодами выборок мгновенных значений только того сигнала, канал которого включен в БВК 16.

Если включено два канала, например второй и пятый, то на выходе сумматора 19 формируется код 01 (табл.), а через -оммутатор 18 на вход установки УВК 17 поступает сигнал с самого мпадшего разряда О счетчика 9. На положительном фронте этого сигна- ла выходным импульсом ФОН 62 все триггеры 61 УВК 17 сбрасываются. На Свходы синхронизации триггеров 61 поступает импульс с четвертого выхода БС 7. Однако вначале он изменить

2Б

возможна только на положительном фронте импульса при условии9 что на

входе разрешения установки I логичес- II111

кая 1, а сигнал на асинхронном входе R сброса триггеров имеет достаточную длительность, чтобы удержать триггеры 61 в сброшенном состоянии. Так же, как и в указанном случае, 30 сначала на выходе элемента 59 ячеи- ки 57.2 логическая 1, которая в

так как на его входе I 1 с выхода элемента 59. При этом в ячейке 57,2 40 элемент И 58 закрьшается, на выходе Элемента 59 устанавливается О и появляется возможность распространения логического О через элемент 60. Этот О беспрепятственно проходит

45 через элементы 60 в третей и четвер

той ячейкахi так как на их входы управления поступают О с выхода БВК 16, а на выходе элемента 59 ячейки 57.5 устанавливается 1, которая

50 в шифраторе 63 преобразуется в двоичный код 100 адреса пятого канала.Ес- ли включено три или четыре канала, то запуск УВК 17 осуществляется по- ; ложительным фронтом сигнала на нуле55 вом выходе счетчика 9, а если включено более четырех каналов - то сигналом на нулевом выходе счетчика 9. В том случае, если включено число каналов, не равное степени два, наприч 1

мер DiecTb каналов 1-й, 2-й, 4-й, Ь-й, 7-й и 8-й), то после опроса все указанных каналов коммутатор 2 закрывается и АЦП 3 кодирует сигналы с нулевым уровнем. В ячейкн ЗУ 4 заносятся коды выборок мгновенных значений входных сигналов в соответствии с табл. 5, где X - произвольное состояние сигналов,

Режим ввода может осуществля1 ься достаточно долго. Счетчик 9 после того, как в момент времени tj достигае состояния О, переходит в состояние Npi (фиг.Зж), для чего используется сигнал на выходе П переполнения счетчика 29, который через элемент ИЛИ 33 поступает на вход установки счетчика 29, после чего в счетчик 29 заносится код с выхода ПЗУ 2. Далее информация в ЗУ 4 обновляетс я. После того, как счетчик 9 первый раз в мо

мент t,, достигает состояния О,устанавливается в 1 триггер 13 (фиг„5и что свидетельствует о том, что информация в ЗУ 45 полностью обновилась (на входах схемы 27 код 001)„

При достижении в момент времени tj сигналом на входе запуска (или, например, в первом канале, если он подается также на вход БСЗ 14) уровня ,Q (фиг.За) 5 который определяется выходным напряжением ИОН 65 (фиг, 4), срабатывает ПЭ 64. При это Б зависимости от того, в каком положении находится переключатель 67, триггер 66 устанавливается в 1 при возростании или убывании сигнала 5ап Положительный фронт сигнала на выходе триггера 66 запускает «ЮИ 68, выходной сигнал которого устанавливает в 1 триггер 11.,При этом устройство продолжает работать в режиме ввода (на входах схемы 27 код 101), но появляется логическая 1 на вход разрешения счета счетчика 10, а в , индикаторе 28 одновременно горят све- тодиоды 69 и 70,, индицирующие то, что ввод информации продолжается и происходит фиксация полезной информации.

Счетчик 10 ранее выходным сигналом ФОН 15 установлен в состояние , Теперь, начиная с момента вре СП

мени

i 5

счетчик 10 подсчитывает выходные импульсы на четвертом выходе БС 7 и тем самым отмеряет интервал времени t., t , который необходим

5

2

дпя завершения процесса ввода инфор- мяпии с тем, что в общем количестве Nj, зафиксированных выборок на канал процент выборок, предшествукндих моменту запуска, равен N, (на фиг.Зз вначале показана работа устройства при , а затем 25 и 75%).

Когда счетчик 10 переходит в состояние О, в момент времени t на выходе П переполнения счетчика 30 формируется сигнал, которьй устанавливает в 1 триггер 12 (фиг. 5к). Кроме того, в счетчик 10 сигналом на выходе П, который через элемент ИЛИ 34 поступает на вход установки

30, заносится код NiA с выоМ

сч е тч ик а

хода ПЗУ 22, так как на четвертом адресном входе ПЗУ 22 в этом случае логическая 1 (табл. 4).

После того, как оба триггера 12 и 13 установятся в 1, устройство с момента времени t переходит в режим вывода информации (на входе схемы 27

КО

11), в индикаторе 28 горят све- тодиоды 70 и 71, индицирующие то, что произошла фиксация полезной информации II устройство работает в per жиме вывода информации (ВЫВ), В режиме вывода информации коды Х| вь борок мгновенных значений входных сигналов из ЗУ 4 выводятся в БИУ

5,который восстанавливает эти сигналы в виде непрерывных функций

(фиг. 5б). которые регистрируются РУ

Восстановление формы входных сигналов в виде непрерывных функций реализуется следующим образом.

В режиме вывода информации на выходе F схемы 27 логическая I. Поэтому таймер 8 формирует импульсы,

период следования которых равен /К (табл.2). БС 7 формирует последовательно во времени импульсы на третьем и четвертом выходах.

Импульс на третьем выходе БС 7 поступает на вход стробиров ния дешифратора 36. С выхода последнего, которьй определяется кодом на его информационном входе, т.е. адресом.обрабатываемого канала, импульс стробирования поступает на вход управления ключа 39 (фиг. 2), он кратковременно замыкается. При этом на конденсаторе 4 фиксируется выходное напряжение МСП 38, которое было в момент пода13

чи сигнала стробирования, на вход дешифратора 36. Выходное напряжение повторителя 40 (повторитель 40 необ- ходим для минимизации токов утечки конденсатора 41) остается постоянным по уровню в интервале между двумя соседними моментами фиксации сигналов. Это напряжение дважды интегрируется интеграторами 43 и 44. Выходной сигнал мел 38 определяется выходными сигналами интеграторов 43 и 44 и ЦЙП 35. Выходной сигнал ЦАП 35 пропорционален выходному коду ЗУ 4, который выводится из ячейки, адрес которой задается счетчиком 9

В режиме вывода информации так же, как и при вводе, обрабатьшаются только те каналы, которые включены в БВК 16, Из ЗУ 4 выводятся коды выборок сигналов и, , Uj , и, .U, Ug в той же последовательности, в какой они занесены в ЗУ 4 при вводе информа ции (табл. 5),

439675 ,14

о

Этот сигнал (фиг. 5г)в момент времени tf через переключатель 25 поступает на вход установки триггера 11 и

g устанавливает его в 1 (фиг. 5д). Устройство опять начинает процесс вывода информации который протекает аналогично указанному. Счетчики 9 и 10 продолжают счет импульсов на

0 втвертом выходе БС 7,, На выходе переполнения счетчика 10, который в конце предыдущего цикла вывода оставался в состоянии О, в начале но- во го цикла вывода,формируется сигнал

15 переполнения, который через элемент ИЛИ 34 поступает на вход установки счетчика 30, В счетчик 10 заносится код , так как триггер 12 остается в состоянии 1 (табл. 4),Устрой20 ство находится в режиме вывода информации в интервале времени t ,t-; (фиг.5), после чего опять переходит 3 режим остановки. Если опять подать сигнал Вывод, то устройство снова

Вьшод информации из ЗУ 4 продолжа- 25 переходит в режим вывода информации.

ется N-,,.. циклов, так как в счетчик .,

10 занесен код К, (фиг. 5з, н),При этом опрошены все N. ячеек ЗУ 4, в которых хранятся последние зафиксированные выборки. Дпя синхронизации моментов запуска РУ 6, например для запуска двигателя лентопротяжного механизма самопишущего прибора, вход . блокировки РУ 6 соединен с выходом F схемы 27.

После того, как счетчик 10 перейдет, в момент времени tj в состояние О, открьюается элемент И 23, выходной сигнал которого (фиг. 5е) сбрасывает триггер П (фиг. 5д). На этом процесс вывода информации заканчивается, и с момента времени tj устройсво переходит в режим останова - на входах схемы 27 код 011 (табл. 4), а в индикаторе 28 остается гореть только светодиод 70 (Фикс), свидетельствующий о том, что полезная информация хранится в ЗУ 4. Когда устройство находится в режиме ввода элемент И 23 открыться ;не может, так как сигнал на выходе состояния О счетчика 10 предшествует моменту установки триггера 11 в состояние 1.

При повторном выводе информации на РУ 6, который необходим, например для - размножения документов регистрации, . необходимо подать сигнал Вы-: вод, который может задаваться кнопкой на пульте управления устройства.

Для того, чтобы начался ввод информации нужно подать сигнал Пуск,

Рассмотрим работу устройства в реиме, непрерывного автома тического

запуска, когда переключатель 26 находится в верхнем положении, а переключатели 24, 25 - в нижнем положении (фиг, 1),

В этом случае после окончания первого цикла вьшода выходной сигнал элеента 23 через переключатель 24 запускает ФОН 15 (фиг, 5в)5 выходной сигнал которого сбрасывает триггеры 11-13 и 66 и устанавливает счетчики

9 и 10 в состояния N и соответственно. Устройство цереходит в режим ввода информации.

В момент времени tg происходит срабатывание БСЗ 4 и триггер 11. устанавливается в 1. После окончания ввода информации, когда триггер 12 в момент времени t устанавливается в 1, начинается цикл вывода информации, который продолжается до момента

появления сигнала на выходе элемента 23 в момент времени t,,, который снова запускает ФОН 15 и переводит устройство в режим ввода информации (фиг. 5).

Рассмотрим работу устройства в случае, когда его запуск в момент ремени t происходит через сравнительно короткий промежуток времен 1 после момента времени t,,. На фяг. 5

i.5

приведен случай, когда переполнение счетчика 10 в момент времени t,j (фиг.Зз)наступает раньше переполне- ния счетчика 9 в момент времени t,4 (фиг.Зж), После достижения переполнения счетчиком 10 триггер 12 устанавливается в 1, а триггер 13 остается в состоянии О. На входе схемы 27 код 110,- а устройство продолжает оставаться в режиме ввода информации (табл. 4) до момента времени , пока не наступит переполнение счетчика 9 и триггер 13 не установится в 1,,т.е. до тех пор, пока информация в ЗУ 4 полностью не обновится.

В этом случае на интервале времени , t,cчeтчик 10 заблокирован, так как его входе разрешения О (табл. 5),

В режиме ручного запуска устройство работает так же, как и в режиме автоматического запуска,но запуск устройства осуществляется сигналом Вывод, который через переключатель 26 поступает на вход установки триггера 11.

Таким образом, в предлагаемом устройстве расширены функциональные возможности, так как появилась возможность управлять длительностью интервала регистрации путем задания кода вторых адресных входах ПЗУ 21 и 22, возможность фиксации информации в интервале времени., предшествующем запуску, причем предусмотрено задание длительности этого интервала в процентном отношении ко всему интервалу регистрации в виде кода N на третьем адресном входе ПЗУ 22, а также возможность управления количеством одновременно работаюЕцих каналов. Причем благодаря возможности управления количеством одновременно работающих каналов, расширяется частотный диапазон и увеличивается длительность регистрации, которая пропорциональна коду К., при меньшем количестве каяВ

налов,

Формула изобретения

Многоканальное устройство для регистрации сигналов, содержашее последовательно соединенные нормирующее устройство, входы которого подключены к входным шинам, первый коммутатор аналого-цифровой преобразователь, за75 .16

поминающее устройство, блок интерполирующих устройств и многоканальное регистрирующее устройство, а также блок синхронизации, таймер, первый и второй счетчики, первый и- второй тригге ры, элемент И, блок синхронизации запуска, вход которого является входом запуска, и формирователь одиночного импульса, при этом выход тай- мера подключен к входу запуска блока синхронизации, первый, второй и третий выходы которого присоединены к входу запуска аналого-цифрового преобразователя, к входу синхронизации записи запоминающего устройства и к входу синхронизации блока интерполирующих устройств, адресные входы которого объединены с адресными входами первого коммутатора, а четвертьй выход блока синхронизации подключен к счетным входам первого счетчика, выход которого соединен с адресным входом запоминающего устройства, и

второго счетчика, выход переполнения которого соединен с входом установки второго триггера, отличающееся тем, что, с целью расширения функциональных возможностей,в него

дополнительно введены блок включения каналов, узел выбора каналов, второй коммутатор, сумматор, первое, второе и третье постоянные запоминающие устройства, первые адресные входы которых совместно с адресным входом

второго коммутатора объединены и подключены к выходу cyMMaTOpia, а выходы постоянных запоминающих устрой :тв связаны с установочными входами таймера, первого и второго счетчиков соответственно, кроме того, в устройство введены третий триггер, два переключателя, логическая схема и индикатор состояния, входы которого подключены к первому, второму и третье- гу выходам логической схемы, четвертьй и пятый выходы которой, соединены с входами разрешения счета первого и второго счетчиков соответственно, при

этом выход блока включения каналов связан с информационным входом сумматора, входами управления блока интерполирующих устройств и узла выбора каналов, выходы которого подключены

к соответствующим адресным входам первого коммутатора и блока интерполирующих устройств, п ри этом четвертый выход блока синхронизации подключен к первому сигнальному входу второго

коммутатора и к входу синхронизации узла выбора каналов, вход установки которого соединен с выходом второго коммутатора, вторые сигнальные входы которого подключены к младшим разрядам первого счетчика, на вторых адресных входах,.первого постоянного запоминающего устройства, на объедииенных вторых адресных входах второго ю щина Вывод через вторую группу кони третьего постоянных запоминаюпщх устройст в и на третьих адресных входах третьего постоянного запоминающего устройства установлены соответственно коды шага дискретизации, коли чества выборок и процента количества выборок, выход переполнения первого счетчика подключен к входу установки третьего триггера, прямой выход второго триггера соединен с четвертым адресным входом третьего постоянного запоминающего устройства и с первым входом элемента И, второй вход которого соединен с выходом состояния нутактов первого переключателя соедине на с первым входом установки первого триггера, а через второй переключатель, другой вход которого подключен

5 к выходу блока синхронизации запуска - к -второму входу установки перво го триггера, выходы первого, второго и третьего триггеров соединены с вх дами логической схемы, первый и тре20 тий выходы которой подключены к входам управления блока синхронизации, при этом третий выход логической схе ьы подключен также к третьему адресному входу первого постоянного заполя второго счетчика, а выход элемента 25минающего устройства и к входу блоИ подключен к первому входу сбросакировки блока интерполирующих устпервого триггера и через первую груп-ройств. пу контактов первого переключателя.

000 00 1 000

011 100 101 110 1 1 Г 000

второй вхОд которого соединен с шиной Пуск, подключен к входу,формирователя одиночных импульсов, выход которого связан с вторым входом сброса первого триггера, с входами сброса второго и третьего триггеров, с входами установки блока синхронизации запуска, первого и второго счетчиков.

тактов первого переключателя соединена с первым входом установки первого триггера, а через второй переключатель, другой вход которого подключен

к выходу блока синхронизации запуска - к -второму входу установки первого триггера, выходы первого, второго и третьего триггеров соединены с входами логической схемы, первый и третий выходы которой подключены к входам управления блока синхронизации, при этом третий выход логической схе- ьы подключен также к третьему адресному входу первого постоянного запоминающего устройства и к входу блоТаблица 1

о о 1 Включено не более одного канала

01 2 Включено два канала

1О 4 Включено три или

четыре канала

1 1 8 Включено более четырех каналов

1 9

51i10232047

102320474095

204740958191

4095819116383

819 1638316383

1638316383 16383

16382 38316383

Таблица 4

0010010Ввод информации

0110010То же

0011011- 0111011 - 1011010- 1439675

20 Таблица 2

I 1 Вьшод информации 00 Останов

00 Запрещенная комбинация

ТаблицаЗ Содержимое ЗУ 4

XX.,.XI11 Код выборок мгновенных

значений сигнала То же

и.

и.

и.

фиг.2

Фив.

| Устройство для регистрации сигналов | 1986 |

|

SU1323856A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-11-23—Публикация

1987-03-05—Подача