(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ГП -ФАЗНЫМ ТИРИСТОИНЫМ ИНВЕРТОЮМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления процессом электроосаждения | 1989 |

|

SU1654385A1 |

| Многоканальное устройство для управ-лЕНия -фАзНыМ иНВЕРТОРОМ | 1979 |

|

SU813669A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1983 |

|

SU1105996A1 |

| Устройство для управления тиристорным однофазным инвертором | 1978 |

|

SU771850A1 |

| Устройство для управления однофазным статическим преобразователем | 1978 |

|

SU764095A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1983 |

|

SU1156227A2 |

| СПОСОБ ДЛЯ УЛЬТРАЗВУКОВОЙ ОЧИСТКИ С ИСПОЛЬЗОВАНИЕМ УЛЬТРАЗВУКОВЫХ КОЛЕБАНИЙ | 2023 |

|

RU2807622C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ С ЗАДАННОЙ ФУНКЦИОНАЛЬНОЙ ЗАВИСИМОСТЬЮ ОТ ВРЕМЕНИ | 1998 |

|

RU2147785C1 |

| Устройство для управления однофазным тиристорным инвертором | 1982 |

|

SU1089755A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1985 |

|

SU1257792A1 |

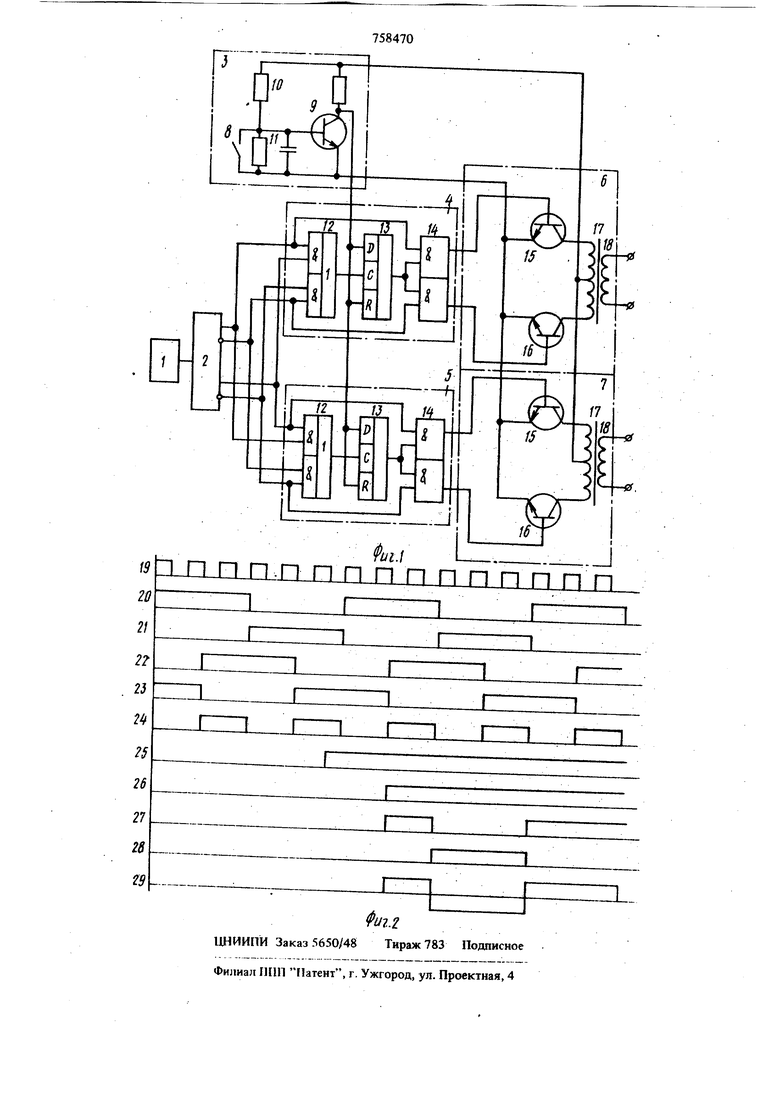

Изобретение относится к электротехнике а более конкретно к системам управления многофазны 0 тиристорными инверторами с трансформаториым выходом. Известно устройство для управления тиристорным инвертором, содержащее цепи подмагничивания силового трансформатора, которое обеспечивает однозначность полярности остаточ иой индукции в трансформаторе вне зависимо ти от того, какой тиристор проводил последним 1. Блок запуска обеспечивает включение каждый раз одного и того же тиристора, поэтому в момент :пуска; исключается насыще ние силового трансформатора и обеспечивается надежный запуск инвертора. Однако это устройство предназначено только для однофазных инверторов, так как Ц(гпн подмагнйчивания выполняются индивидуально для каждого трансформатора, кроме того, уве личиваются масса и габариты инвертора, так как указанное устройство воздействует на силовые цепи и требует сильноточных и энергетических элементов. Известно устройство для управления тирисгорным инвертором, которое при включении инвертора обеспечивает частоту выходных импульсов выще, чем в номинальном режиме, и тем самым представляет насыщение выходного трансформатора и обеспечивает надежный запуск инвертора 2. Оцнако это устройство предназначаю только для однофазных инверторов, кроме того, время выхода инвертора на стационарный режим может быть недопустимо большим. Наиболее близким по технической сущности к предлагаемому является устройство для управления инвертором, содержащее задающий генератор, кольцевой пересчетный блок и выходные каскады 3. Указанное устройство обеспечивает гальваническую развязку цепей Зтравления от силовых и отличается высокой стабильностью угла сдвига фаз. Однако это устройство не обеспечивает надежного запуска тиристорного инвертора, так как до включения инвертора полярность остаточной индукции в магнитопроводе силового тра1кформатора может быть как положитель37ной, так и отрицательной. В момент пуска пер вым может включаться тот тиристор, который вызовет дальнейшее увеличение индукции. А так как длительность управляющих импульсов составляет полпериода выходной частоты, то трансформатор инвертора может насытиться и произойдет срыв комм)лгации, т.е. инвертор выходит из строя. Целью изобретения является повышение надежности инвертора, в работе в момент пуска путем уменьшения длительности первого полупериода управляющих импульсов. Поставленная цель достигается тем, что устройство для управления т-фазным тиристорны инвертором, содержащее задаюший генератор, подключенный ко входу кольцевого пересчетного блока на m триггерах и m выходных кас кадов, снабжено блоком запуска и m логическими блоками задержки, каждый из которых содержит элемент 2-2И-ИЛИ, тактируемый Dтриггер и два двухвходавых блока совпадения выходы которых подключены соответственно к выходным каскадам, одни из входов объеди нены и соединены с выходом тактируемого D-триггера, D- и R-входы которого объединены и подключены к блоку запуска, тактовый вход связан с вь1ходом элемента 2-2И-ИЛИ, одни из входов которого подключены к выхо дам i-Toro триггера кольцевого пересчетного блока и к другим входам блоков совпадения, другие входь - к выходам j-того триггера кольцевого пересчетного блока, при этом j i + На фиг. 1 представлена схема устройства, на фиг. 2 приведены диаграммы, поясняющие его работу. Устройство для управления т-фазным тиристорным инвертором содержит задающий генератор 1, кольцевой пересчетный блок 2, бло запуска 3,- логические блоки задержки 4 и 5 и выходные каскады 6, 7. Блок запуска 3 со стоит из механического выключателя 8, транзистора 9 и делителя на резисторах 10 и П. Каждый блок задержки состоит из элемента 2-2И-ИЛИ 12, тактируемого D-триггера 13 и двух двухвходовых блоков совпадения 14. Выходные каскады 6, 7 представляют собой двухкратные усилители мощности, каждый из которых собран на транзисторах 15, 16 и тран сформаторе 17 с выходной обмоткой 18. Кол цевой пересчетный блок 2 для простоты составлен из двух триггеров ), т.е. изображенное на фиг. 1 устройство предназначено для управления двухфазным инвертором. Устройство jyiH управления т-фазным тири торным инвертором работает следующим обра 1зом. При подаче напряжения питания на выходе задающего генератора 1 формируются импульсы 19, которые поступают на блок 2. На выходе первого триггера кольцевой пересчетной схемы формируются прямой 20 и инверсный 21 сигналы, на выходе второго триггера сигналы 22 и 23. Поскольку логические блоки задержки 4 и 5 выполнены по одной и той же схеме, принцип работы их одинаков, то далее останавливаются на работе логического блока задержки 4. На выходе элемента 2-2И-ИЛИ , 12 формируются сигналы 24, длительность которых равна времени, в течение которого сигналы на выходе триггеров, подключенных к элементу 2-2И-ИЛИ 12, совпадают. В данном случае длительность импульсов 24 равна четверти периода. Эти импульсы поступают на тактовый вход С тактируемого D-триггера 13, но они не могут изменить состояние триггера, так как механический выключатель 8 блока 3 разомкнут, транзистор 9 открыт и с его коллектора на R- и D-выходы триггера поступает сигнал 25, соответствующий уровню логического О, который удерживает триггер в нулевом положении, и на выходе триггера отсутствует разрешающий сигнал 26. Выход триггера подключен к одним из входов блока совпадения 14, поэтому выходные сигналы 27, 28 блока совпадения 14 также равны О, транзисторы 15, 16 выходного каскада 6 закрыты и На обмотке 18 трансформатора 17 нет напряжения. Таким образом, несмотря на то, что задающий генера тор 1 и блок 2 функционируют, устройство в целом находится в режиме ожидания. При замыкании механического выключателя 8 транзистор 9 закроется и на R- и D-выходы тактируемого D-триггера 13 поступит сигнал 25, соответствующий уровню логического 1. Поэтому, как только на входе С сигнал 24 изменит свое состояние с О на 1, триггер 13 переключится в состояние 1, разрешая тем прохождение единичных сигналов с выхода блока 2 на базы транзисторов 15, 16 выходного каскада 6. Первоначально на базу транзистора 15 поступит сигнал 27, длительность которого составляет четверть периода выходной частоты. Затем на базы транзисторов 15, 16 начинают поступать .импульсы 27, 28, длительность которых составляет полпериода выходной частоты, т.е. устройство в целом выходит на стационарный режим. Напряжение на выходной обмотке 18 трансформатора 17, поступающее на управляющие электроды тиристоров, показано на диаграмме 29. Так как включаемый первым тиристор работает всего лишь четверть периода, предотвращается насыщение силовою трансфор.матора и повышается тем самым надежность инвертора в пусковом режиме. При большем числе триггеров в кольцевой пересчетной схеме длительность первого полупериода управляющих импульсов может варьироваться в более широких пределах. Например, в устройстве управления, содержащем кол цевую пересчетную схему из щести триггеров, длительность первого полупериода управляющи . импульсов может составлять 90, 60 и 30 эл.гр дусов. Для этого на другие входы элемента 2-2И-ИЛИ, подключенного одним из входов, например, к выходам первого триггера кольцевой пересчетной схемь, необходимо подавать сигналы соответственно с четвертого, пятого и шестого триггеров кольцевой пересчетной схемы. В обшем случае кольцевая пересчетная схема может состоять из m триггеров. Тогда, для того чтобы получить длительность перво- го полупериода управляющих импульсов меньще или равной четверти периода выходной час тоты, другие входы элемента 2-2И-ИЛИ, подключенного одним из входов к входам i-oro триггера кольцевой пересчетной схемы, должны быть подключены к выходам j-oro триггера кольцевой пересчетной схеме, где j i + - Устройство пригодно для утфавления ннвертора любой фазности, в том числе и однофазными. Время выхода инверторами на стационар ный режим составляет менее полупериода выходной частоты. Формула изобретения Устройство для управления m-фaзньпvl тнристорным инвертором, содержащее задающий генератор, подключенный ко входу кольцевого пересчетаого блока на m триггерах и m выходных каскадах, отличающееся тем, что, с целью повышения надежности в работе инвертора в момент пуска, оно снабжено блоком запуска и m логическими блоками задержки, каждый из которых содержит элемент 2-2И-ИЛИ, тактируемый D-трнггер и два двухвходовых блока совпадения, выходы которых подключены к соответствующему выходному каскаду, одни из входов объединены и соединены с выходом тактируемого D-триггера, О- и R-входы которого объединены и подключены к блоку запуска, тактовый вход связан с выходом элемента 2-2И-ИЛИ, одни из входов которого подключшы к выходам i-oro триггера кольцевого пересчетного блока и к другим входам блоков совпадения, а другие . входы - к выходам j-oro триггера кольцевого пересчетаого блока, при этом j i + - . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР tP 447811, кл. Н 02 Р 13/18, 1968. 2.Авторское свидетельство СССР fP 538471, кл. Н 02 Р 13/18, 1973. 3.Авторское свидетельства СССР W 481114, кл. Н 02 Р 13/18, 1968.

Авторы

Даты

1980-08-23—Публикация

1978-08-15—Подача