Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах (ЗУ), в которых носителями ин формации являются цилиндрические м нитные домена (1VMT) . Известен накопитель для ЗУ, содержащий Ы+р регистров хранения, объединенных информационно каналом связи для записи и считывания НЛДинформации , который содерхсит Н + р элементов передачи доментов и Н+ р динамических ловушек, в которые зап сывается информация о дефектности накопителя 1. Каждый элемент пер дачи содержит первый и несколько вт рых каналов продвижения . Каждый второй канал,начинается и заканчива ется в первом канале и шунтирует по ледний между его началом и концом. Известный накопитель для ЗУ имеет следующие недостатки: сложный по своему выполнению алгоритм замещения дефектного регистра хранения смежным с ним (по каналу связи для записи и считывания) бездефектным накопительным регистром, а также на личие магнитостатического взаимоде ствия домен-домен (взаимодейртвие ГЛД в динамической ловушке с информационным потоком доменов), сущеЪтвенно сужающего область работы чипа, практически не позволяет осуществлять резервирование деЛектных регистров хранения внутри чипа. .Наиболее близким техническим решением к изобретению является накопитель для ЗУ, который содержит магнитоодноосную пленку с НМД, на поверхности которой расположены регистров хранения информации, где Ы и р-соответственно количество работоспособных и дефектных регистров хранения информации, магнитосвязанных с каналами ввода и вывода информации, датчик считывания ЦЧД, выход которого соединен с входом усилителя считывания, генератор НМД, подключенный к каналу ввода информации, и формирователь управляющих сигналов 2. В таком накопителе информация о дефектности записывается в отдельное полупостоянное запоминающее устройство (ППЗУ). Каждый регистр хранения ассоцируется с определенным битом ППЗУ, причем О отмечает бездефектный регистр хранения, а дефектный. Единичные значения сигналов, поступающих из ППЗУ,запрещают формирование соответствующих разрядовинформационной последовательноети НМД, и в последней образуются пропуски / соответствующие дефектным регистрам хранения информации.

Основной недостаток такого способа введения избыточности в ЦМДнакопитель заключается в.необходи 1рсти использования внешнего по отношению к чипу полупостоянного ЗУ. Крометого, для побитного выравнивания считываемых из различных накопителей информационных слов, образующих информационную .страницу, требуется использовайие дополнительных буферных сдвиговых регистров.

Цель изобретения - упрощение накопителя и повьдиение его надежности.

Поставленная цель достигается путем того/ что он содержит узел коррекции дефектов накопителя, выполненный в виде управляемых .элементов задержки, и N+p регистров дефектност один из управляемых элементов задержки расположен в канале ввода информации между генератором ЦМД и регистр ми хранения информации, с другой в канале вывода информации -между регистрами хранения информации и датчиком считывания 1уед,Н+р регистров дефектности подключены к каналу ввода информации между регистрами хранения информации и датчиком считывания ЦМД, а усилителя считывани через формирователь управляющих оигналов подключен к управляемым элементам 3 адержки.

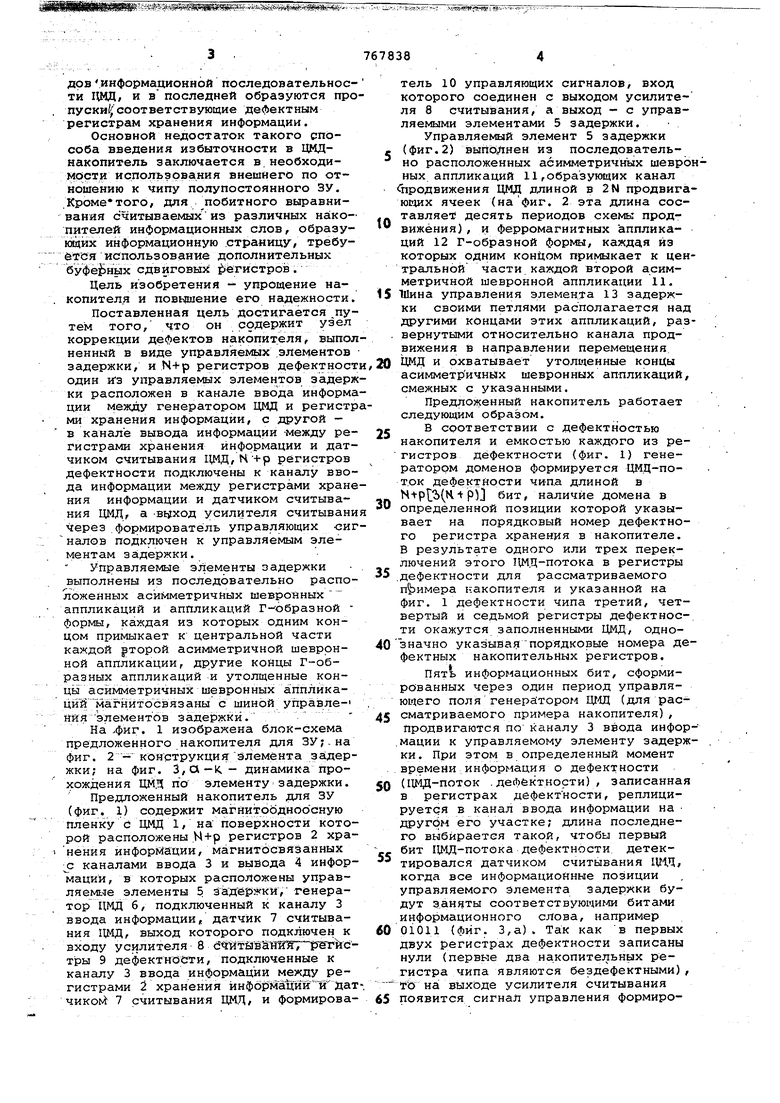

Управляемые элементы задержки выполнены из последовательно расположенных асимметричных шевронных аппликаций и аппликаций Г-образной формы, каждая из которых одним концом примыкает к центральной части каждой рторой асимметричной шевронной аппликации, другие концы Г-образных аппликаций и утолщенные концы асимметричных шевронных аггплйкаций магнйтосвязаны с шиной управленйя элементов за держки. .

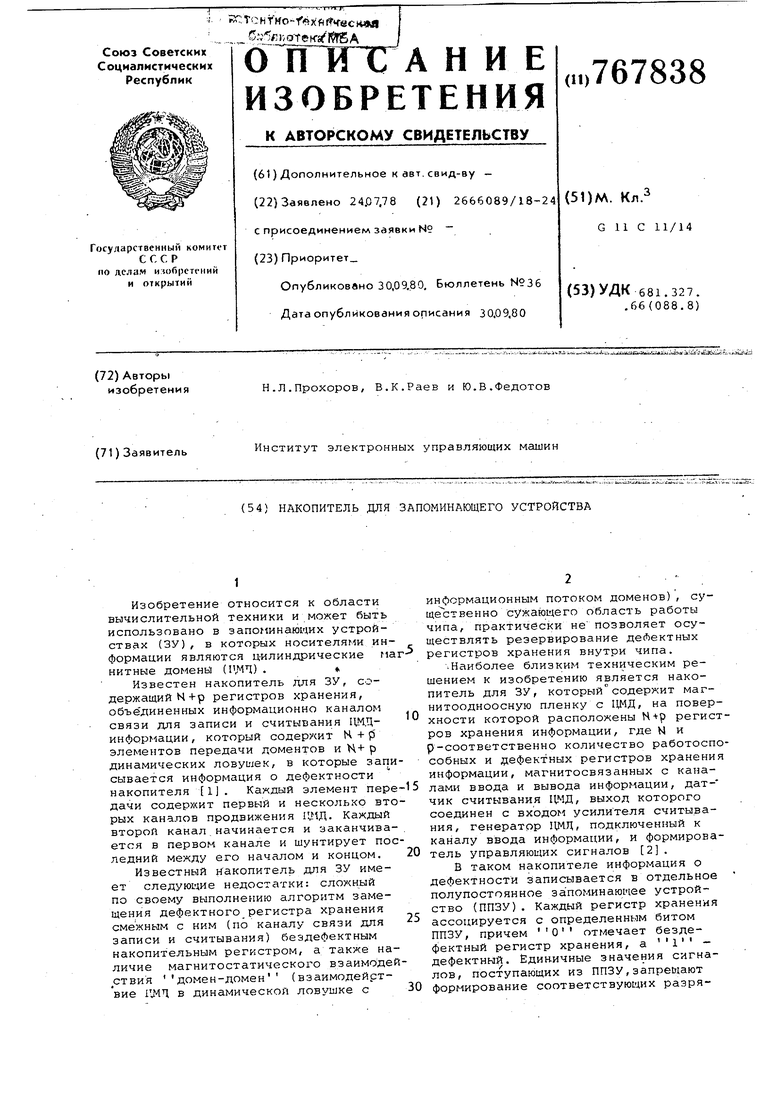

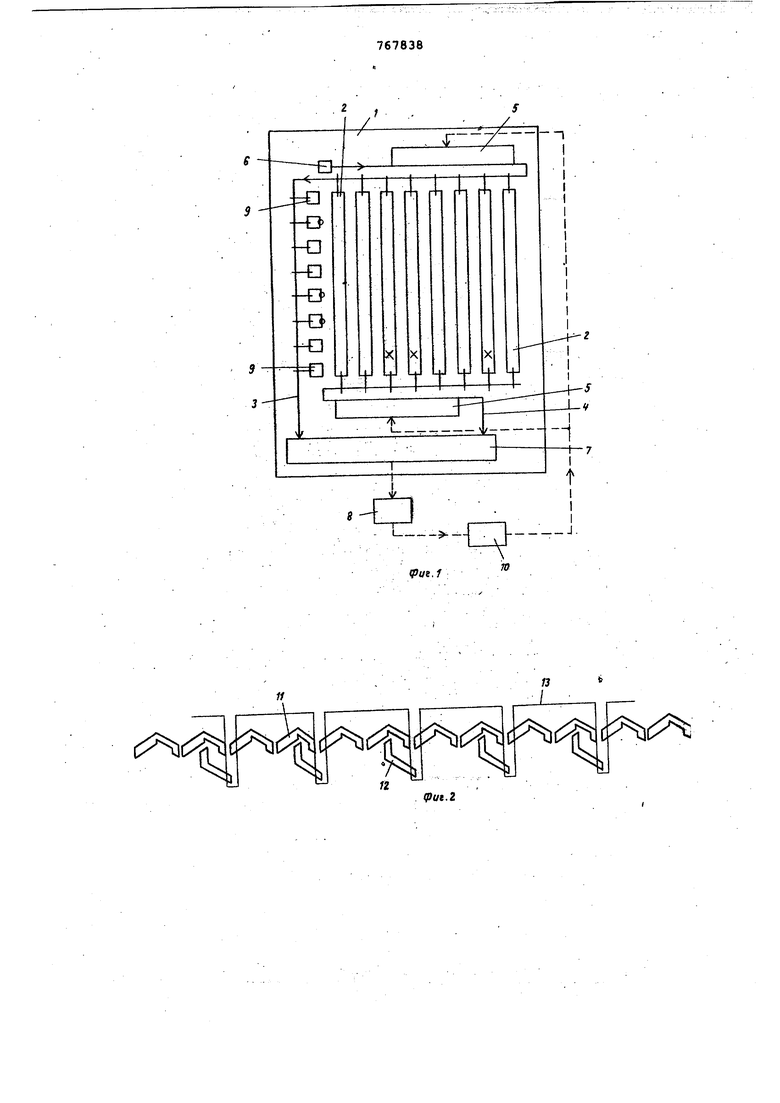

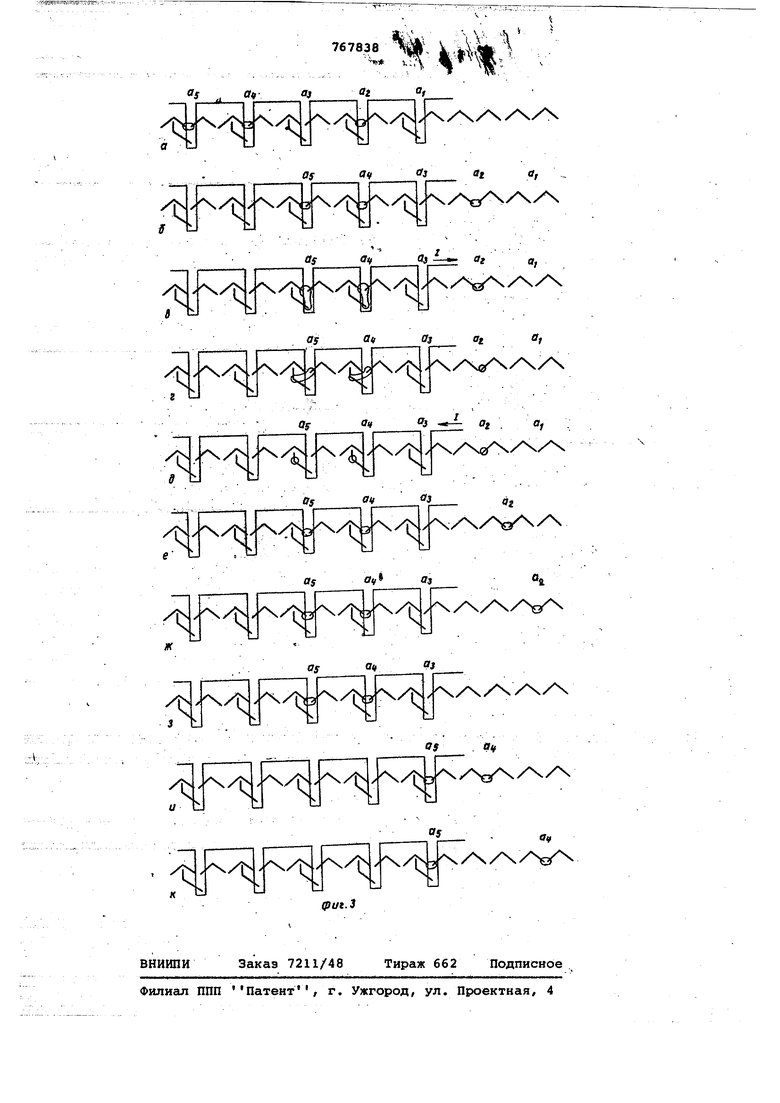

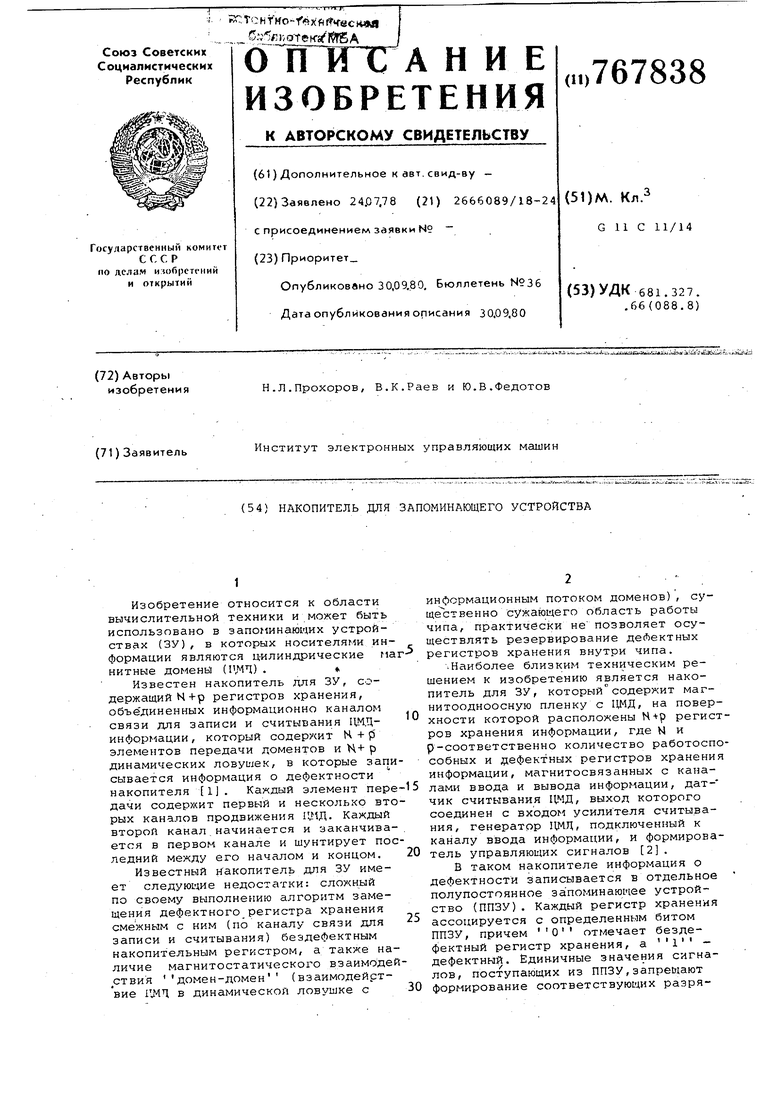

На .фиг. 1 изображена блок-схема предложенного накопителя для ЗУ;- на фиг. 2 - конструкция алемёнта задержки; на фиг. 3,а-Ц- динамика прохождения ЦМД по элементу задержки.

Предложенный накопитель для ЗУ (фиг. 1) содержит магнитоодноосную пленку с ЦМД 1, на поверхности которой расположены .N+p регистров 2 хранения информации, магнитбсвязанных с каналами ввода 3 и вывода 4 инфор мации, в которых расположены управляе№1е элементы 5 задержки, генератор ЦМД б, подключенный к каналу 3 ввода информации, датчик 7 считывания ЦМД, выход которого подключен к входу усилителя 8 с -йтавПШ157 РёТ стры 9 дефектности, подключенные к каналу 3 ввода информации между регистрами 2 хранения йнфб 5мавд1Й 11 Дат чико 7 считывания ЦМД, и формирова767838

тель Ю управляющих сигналов, вход которого соединен с выходом усилителя 8 считывания, а выход - с управляемыми элементами 5 задержки.

Управляемый элемент 5 задержки (фиг. 2) выпо.Днен из последовательно расположенных асимметричных шевроных аппликаций 11,образующих канал

продвижения ЦМД длиной в 2N продвигающих ячеек (нафиг. 2 эта длина составляет десять периодов схемы продвижения) , и ферромагнитных аппликаций 12 Г-образной формы, кажддя из которых одним KOHtiOM примыкает к центральной части каждой второй асимметричной шевронной аппликации 11. Шина управления элемента 13 задержки своими петлями располагается над другими концами этих аппликаций, развернутыми относительно канала продвижения В направлении перемещения ЦМД и охватывает утолщенные концы асимметричных шевронных аппликаций, смежных с указанными.

Предложенный накопитель работает следующим образом.

В соответствии с дефектностью накопителя и емкостью каждого из регистров дефектности (фиг. 1) генератором доменов формируется ЦМ.Д-пот.ок дефектности чипа длиной в (4ip5J бит, наличие домена в определенной позиции которой указывает на порядковый номер дефектного регистра хранения в накопителе. В результате одного или трех переключений этого НМД-потока в регистры

.дефектности для рассматриваемого примера ь:акопителя и указанной на фиг. 1 дефектности чипа третий, четвертый и седьмой регистры дефектноети окажутся заполненными ЦМД, однозначке указываяпорядковые номера дефектных накопительных регистров.

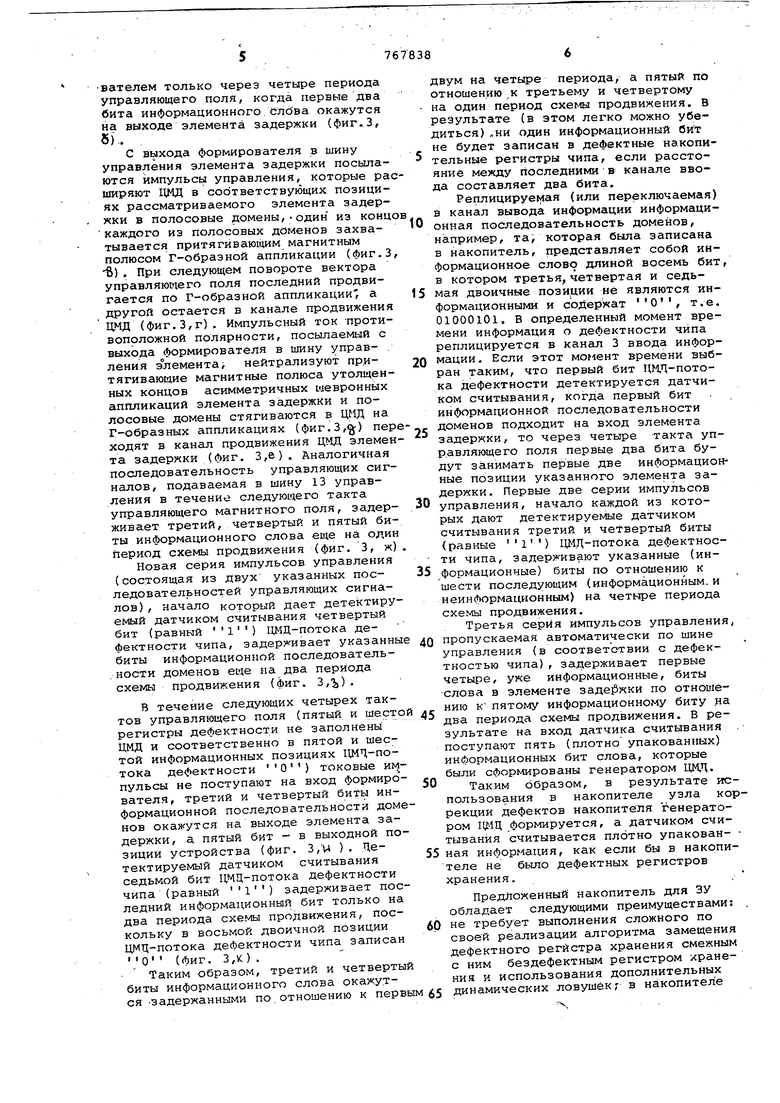

Пять информационных бит, сформированных через один период управляющего поля генератором ЦМД (для рассматриваемого примера накопителя), Продвигаются по каналу 3 ввода ииформации к управляемому элементу задержки . При этом в определенный момент времени информация о дефектности (ЦМД-поток .дефектности), записанная в регистрах дефектности, реплицируется в канал ввода информации на другом его участке; длина последнего выбирается такой, чтобы первый бит НМД-потока дефектности детектировался датчиком считывания НМД, когда все информационные позиции управляемого элемента задержки будут з.аняты соответствующими битами информационного слова, например 01011 (фиг. 3,а). Так как в первых двух регистрах дефектности записаны нули (первые два накопительных регистра чипа являются бездефектными), ТЬ Hai выходе усилителя считывания появится сигнал управления формирователем только через четыре периода управляющего поля, когда первые два бита информационного слбва окажутся на выходе элемента задержки (фиг.З, «) .

С выхода формирователя в шину управления элемента задержки посылаются импульсы управления, которые раширяют 1ЩД в соответствующих позициях рассматриваемого элемента задержки в полосовые домены, один из конц

каждого из полосовых доменов захватывается притягиваюдам магнитным полюсом Г-образной аппликации (фиг.З

6). При следующем повороте вектора управляющего поля последний продвигается по Г-образной аппликации а другой остается в канале продвижения ЦМД (фиг.З,г) . Импульсный ток противоположной полярности, посылаемый с выхода формирователя в шину управ- . ления э°лемента, нейтрализуют притягивающие магнитные полюса утолщенных кондов асимметричных шевронных аппликаций элемента задержки и полосовые домены стягиваются в ЦМД на Г-образных аппликациях (фиг.З,) пер ходят в канал продвижения ЦМД элемента задержки (фиг. 3,е). Аналогичная последовательность управляющих сигналов, подаваемая в шину 13 управления в теченич5 следующего такта управляющего магнитного поля, задерживает третий, четвертый и пятый биты информационного слова еще на один йериод схемы продвижения (фиг. 3, к)

Новая серия импульсов управления (состоящая из двух указанных последовательностей управляющих сигналов) , начало который дает детектируемый датчиком считывания четвертый бит (равный ) ЦМД-потока дефектности чипа, задерживает указанны биты информационной последователь.ности доменов еще на два периода схемы продвижения (фиг. 3,J,).

В течение следующих четырех тактов управляющего поля (пятый и шест;о регистры дефектности не заполнены ЦМД и соответственно в пятой и шестой информационных позициях ЦМД-потока дефектности О) токовые им пульсы не поступают на вход формирователя, третий и четвертый биты информационной последовательности доменов окажутся на выходе элемента задержки , а пятый бит - в выходной позиции устройства (фиг. 3,И ). Детектируемый датчиком считывания седьмой бит ЦМЦ-потока дефектности чипа (равный ) задерживает последний информационный бит только на два периода схемы продвижения, поскольку в восьмой двоичной позиции ЦМД-потока дефектности чипа записан О (фиг. 3,к).

Таким образом, третий и четвертый биты информационного слова окажутся -задержанными по.отношению к первы

двум на четыре периода, а пятый по отношению ,к третьему и четвертому на один период схемы продвижения. В результате (в этом легко можно убедиться) „ни один информационный бит не будет записан в дефектные накопительные регистры чипа, если расстояние между последними в канале ввода составляет два бита.

Реплицируемая (или переключаемая) в канал вывода информации информационная последовательность доменов, например, та, которая была записана в накопитель, представляет собой информационное слово длиной восемь бит в котором третья,четвертая и седьмая двоичные ПОЗИ1ДИИ не являются информационными и содержат О, т.е. 01000101. В определенный момент времени информация о дефектности чипа реплицируется в канал 3 ввода информации. Если этот момент времени выбран таким, что первый бит ЦМД-потока дефектности детектируется датчиком считывания, когда первый бит информационной последовательности доменов подходит на вход элемента задержки, то череэ четыре такта управляющего поля первые два бита будут занимать первые две информационные позиции указанного элемента задержки . Первые две серии импульсов управления, начало каждой из которых дают детектируемые датчиком считывания третий и четвертый биты (равные ) 1ЩД-потока дефектности чипа, задерживают указанные (информационные) биты по отношению к шести последующим (информационным, и неинформационным) на четыре периода схемы продвижения.

Третья серия импульсов управления пропускаемая автоматически по шине управления (в соответствии с дефектностью чипа), задерживает первые четыре, уже информационные, биты слова в элементе задержки по отношению К пятому информационному биту на два периода схемы продвижения. В результате на вход датчика считывания поступают пять (плотно упакованных) информационных бит слова, которые были сформированы генератором ЦМД.

Таким образом, в результате использования в накопителе узла корекции дефектов накопителя генератором Щ-1Д формируется, а датчиком считывания считывается плотно упакованная информация, как если бы в накопителе не бьшо дефектных регистров хранения.

Предложенный накопитель для ЗУ обладает следующими преимуществами: не требует выполнения сложного по своей реализации алгоритма замещения дефектного регистра хранения смежным с ним бездефектным регистром хранения и использования дополнительных динамических ловушек, в накопителе

, отпадает необходимость использовани внешнего по отношению к чипу полупостоянного ЗУ и дополнительных бу ферных сдвиговых регистров и вследствие этого появляется воэможнрсть исправлять ошибки, связанные с дефе тными накопительными регистрами, бл же к месту их возникновения и избежать ошибок, связанных с передачей информационных слов из ППЗУ и буфе ных сдвиговых регистров в ЦМЦ-накопитель и обратно. Идентичность управляемых элемент задержки, используемых в предложенно накопителе, в каналах ввода и вывода информации позволяет построить ЦМД-накопитель с общим для записи и считывания каналом связи и одним эле ментом задержки. Формула изобретения .1. Накопитель для запоминающего устройства, содержащий магнитоодноосную пленку с цилиндрическими магнитными доменами, на поверхности которой расположены N+р регистров хранения информации, где Мир- соответственно количество работоспособных и дефектных регистров хранения информации, Г1агнитосвязанных с каналами ввода и вывода информации, датчик считывания цилиндрйчес.ких маг нйтных Доменов, выход которого сое-дин-ен с вxoдo усилителя считывания ,генератор цилиндрических магнитных доменов, подключенный к каналу ввода информации, и формирователь управ ляющих сигналов, о т л и ч а ю щ и и ся тем, что, с цельй упрощения накопителя и повьпления его надежности, он содержит узел коррекции дефектов накопителя, выполненный в виде управляемых элементов задержки, и регистров дефектности, один из управляемых элементов задержки расположен в канале ввода информации между генератором цилиндрических магнитных доменов и регистрами хранения информации, а другой - в канале вывода информации между регистрами хранения информации и датчиком- считывания цилиндрических магнитных доменов, М+р регистров дефектности подключены к каналу ввода информации между регистрами хранения информации и датчиком считывания цилиндрических доменов, а выход усилителя считывания через формирователь управляющих сигналов подключен к управляемым элементам задержки. 2. Накопитель по п.1, отличающийся тем, что, управляемые элементы задержки выполнены из последовательно расположенных асимметричных шевронных аппликаций и аппликаций Г-образной формы, каждая из которых одним концом примыкает к центральной части каждой второй асимметричной шевронной аппликации, другие концы Г-образных аппликаций и утолщенные концы асимметричных шевронных аппликаций магнитосвязаны с 1шной управления элементов задержки. . Источники информации, принятые во внимание при экспертизе 1. Патент СЧА № 3921156, кл.3401 74, 1976. 2.IEEE Trans. Мадп., V.MAG-12, W 6, 1976 (прототип).

9 3

-S

-Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU678535A1 |

| Накопитель информации для запоминающего устройства на цилиндрических магнитных доменах | 1980 |

|

SU942145A1 |

| Переключатель цилиндрическихМАгНиТНыХ дОМЕНОВ | 1978 |

|

SU803011A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU947909A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU875457A1 |

| Накопитель для запоминающего устройства | 1981 |

|

SU970467A1 |

| Накопитель информации | 1983 |

|

SU1133618A1 |

| Запоминающее устройство | 1979 |

|

SU963092A1 |

| Запоминающий модуль | 1980 |

|

SU920839A1 |

| Делитель-аннигилятор цилиндрических магнитных доменов | 1977 |

|

SU708416A1 |

Авторы

Даты

1980-09-30—Публикация

1978-07-24—Подача