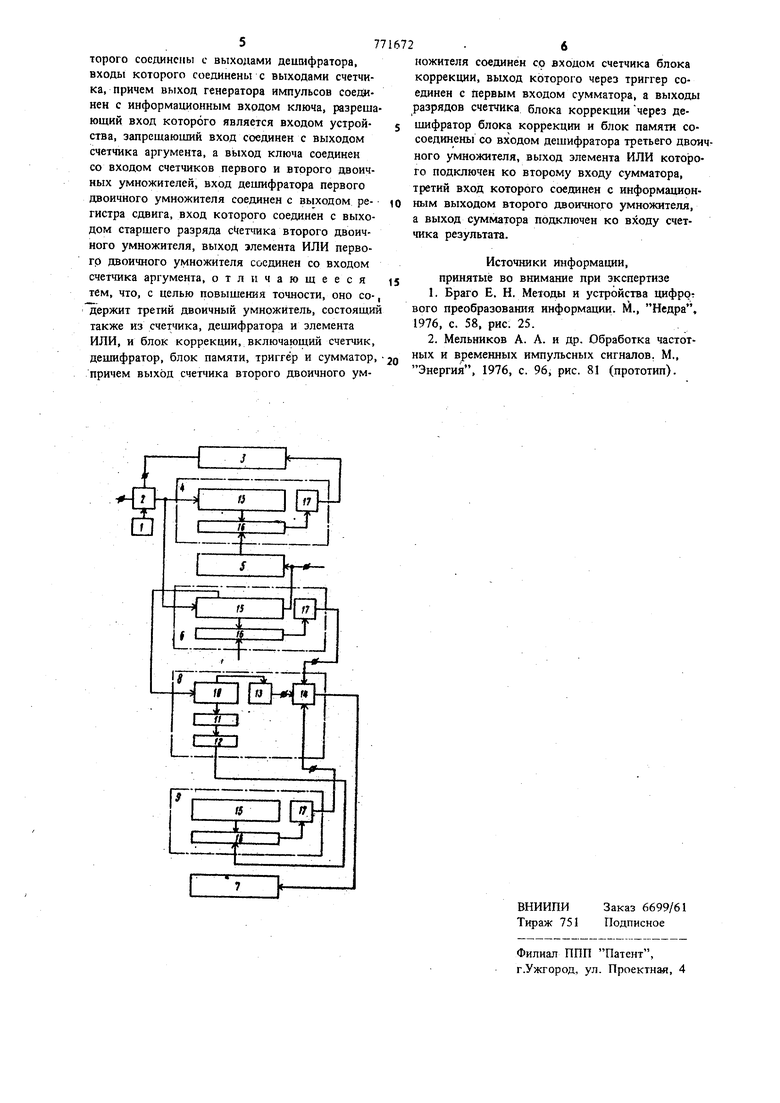

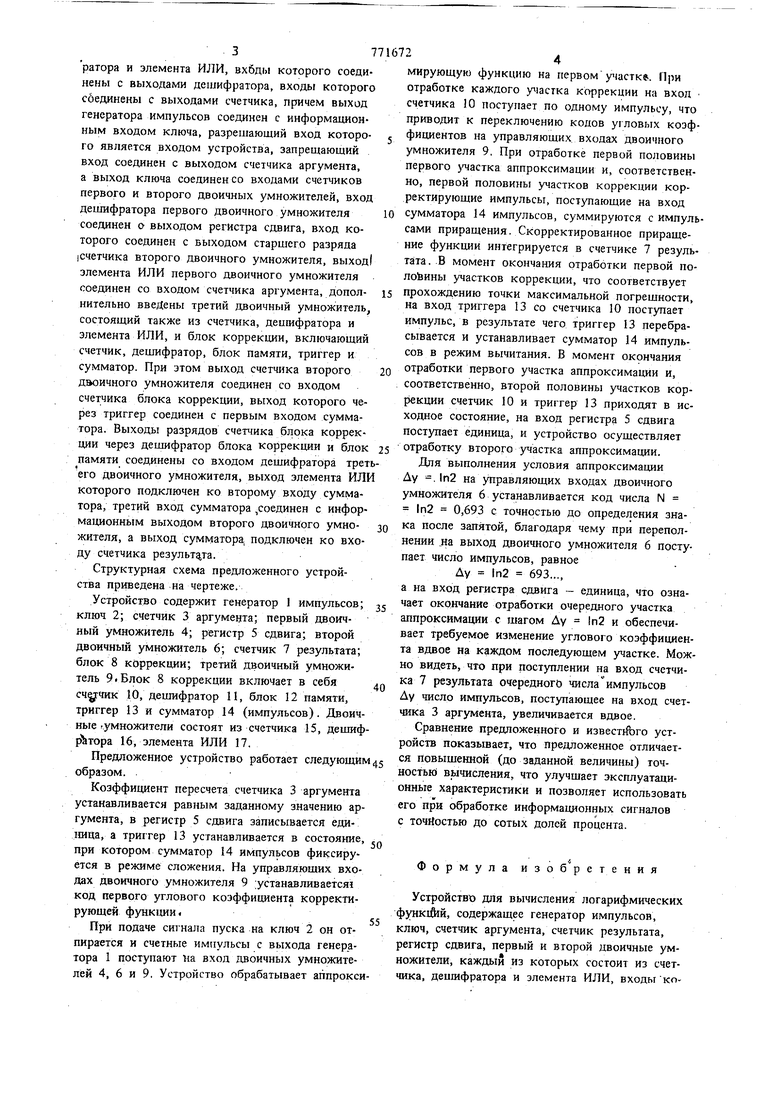

. . , : . 1 , Изобретение относится к вычислительной тех нике, а именно к устройствамдля воспроизведения и вычисления логарифмических функций методом кусочно-линейной аппроксимации. Извес-шы устройства для функционального преобразования информационных сигналов в ви де унитарных кодов Ц, .содержащие управляемый делитель, счетчик участков, блок памяти и схему его управления. Такие устройства хотя и обеспечивают кусочно-линейную аппроксимацию с фиксированным шагом по выходной переменной, однако имеют существенный недостаток - табличное задание функции, что при повышенных требованиях к точности приводит к увеличению приборных затрат и снижению надежности. Наиболее близким по технической сущности к предложенному является устройство для воспроизведения логарифмических функций аппроксимирующей функции 21, содержащее генератор импульсов, ключ, счетчик аргумента, счегчик результата, регистр сдвига, первый и второй двоичные умножители, каждый из которых состоит из счетчика, дешифратора и элемента ИЛИ, входы которого соединены с выходами дешифратора, входы которого соединены с выходами счётчика, причем выход генератора импульсов соединен с информационным входом ключа, разрешающий вход которого является входом устройства, запрещающий вход соединен с выходом счетчика аргумента, а выход ключа соединен со входами счетчиков первого и второго двоичных умножителей. Вход дешифратора первого двоичного умножителя соеданен с выходом регистра сдвига, вход которого соединен с вь1ходом старшего разряда счетчика второго двоичного умножителя, выход элемента ИЛИ первого двоичного умножителя соеданен со входом счетчика аргумента. Недостатком устройства является низкая точность вследствие .того, что аппроксимирующая функция имеет ступенчатую форму. Цель изобретения - повышение точности. Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов, ключ, счетчик аргумента, счетчик результата, регистр сдвига, первый и второй двоичные умножители, каждый из которых состоит из счетчика, деишфратора и элемента ИЛИ, вхбды которого соединены с выходами дешифратора, входы которого соединены с выходами счетчика, причем выход генератора импульсов соединен с информационным входом ключа, разрешающий вход которого является входом устройства, запрещающий вход соединен с выходом счетчика аргумента, а выход ключа соединен со входами счетчиков первого и второго двоичных умножителей, вход дешифратора первого двоичного умножителя соединен о выходом регистра сдвига, вход которого соединен с выходом старшего разряда |счетчика второго двоичного умножителя, выход элемента ИЛИ первого двоичного умножителя соединен со входом счетчика аргумента, дополнительно введены третий двоичный умножитель, состоящий также из счетчика, дешифратора и элемента ИЛИ, и блок коррекции, включающий счетчик, дешифратор, блок памяти, триггер и сумматор. При этом выход счетчика второго даоичного умножителя соединен со входом сче1;чика блока коррекции, выход которого через триггер соединен с первым входом сумматора. Выходы разрядов счетчика блока коррекции через дешифратор блока коррекции и блок памяти соединены со входом дешифратора трет его двоичного умножителя, выход элемента ИЛИ которого подключен ко второму входу сумматора, третий вход сумматора ,соединен с информационным выходом второго двоичного умножителя, а выход сумматора, подключен ко входу счетчика результата. Структурная схема предложенного устройства приведена на чертеже. Устройство содержит генератор 1 импульсов; ключ 2; счетчик 3 аргумента; первый двоичный умножитель 4; регистр 5 сдвига; второй двоичный умножитель 6; счетчик 7 результата; блок 8 коррекции; третий двоичный умножитель 9. Блок 8 коррекции включает в себя 10, дешифратор И, блок 12 памяти, триггер 13 и сумматор 14 (импульсов). Двоичные умножители состоят из счетчика 15, дешнф phTOpa 16, элемента ИЛИ 17. Предложенное устройство работает следующим образом. Коэффициент пересчета счетчика 3 аргумента устанавливается равным заданному значению аргумента, в регистр 5 сдвига записывается единица, а триггер 13 устанавливается в состояние при котором сумматор 14 импульсов фиксируется в режиме сложения. На управляющих входах двоичного умножителя 9 устанавливается код первого углового коэффициента корректирующей функции. При подаче сигнала пуска на ключ 2 он отпирается и счетные импульсы с выхода генератора 1 поступают на вход двоичных умножителей 4, 6 и 9. Устройство обрабатывает аппрокс мирующую функцию на первом участке-. При отработке каждого участка коррекции на вход счетчика 10 поступает по одному импульсу, что приводит к переключению кодов угловых коэффициентов на управляющих входах двоичного умножителя 9, При отработке первой половины первого )частка аппроксимации и, соответственно, первой половины участков коррекции корректирующие импульсы, поступающие на вход сумматора 14 импульсов, суммируются с импульсами приращения. Скорректированное приращение функции интегрируется в счетчике 7 результата. .В момент окончания отработки первой полоЬины участков коррекции, что соответствует прохождению точки максимальной погрешности, на вход триггера 13 со счетчика 10 поступает импульс, в результате чего триггер 13 перебрасывается и устанавливает сумматор 14 импульсов в режим вычитания. В момент окончания отработки первого участка аппроксимации и, соответственно, второй половины участков коррекции счетчик 10 и триггер 13 приходят в исходное состояние, на вход регистра 5 сдвига поступает единица, и устройство осуществляет отработку второго участка аппроксимации. Для выполнения условия аппроксимации Ду . 1п2 на управляющих входах двоичного умножителя 6 устанавливается код числа N 1п2 0,693 с точностью до определения знака после запятой, благодаря чему при переполнении .на выход двоичного умножителя 6 поступает число импульсов, равное Ду 1п2 693..., а на вход регистра сдвига - единица, что означает окончание отработки очередного участка аппроксимации с шагом Ду 1п2 и обеспечивает требуемое изменение углового коэффициента вдвое на каждом последующем участке. Можно видеть, что при поступлении на вход счетчика 7 результата очередного числа импульсов Ду число импульсов, поступающее на вход счетчика 3 аргутиента, увеличивается вдвое. Сравнение предложенного и извест Ьго устройств показывает, что предложенное отличается повышенной (до заданной величины) точностью в ычисления, что улучшает эксплуатационные характеристики и позволяет использовать его при обработке информационных сигналов с точностью до сотых долей процента. Формула изобретения Устройство для вычисления логарифмических функ1Й1Й, содержащее генератор импульсов, ключ, счетчик аргумента, счетчик результата, регистр сдвига, первый и второй двоичные умножители, каждый из которых состоит из счетчика, дешифратора и элемента ИЛИ, входыкоторого соединены с выходами деишфратора, входы которого соединены с выходами счетчика, причем выход генератора импульсов соединен с информационным входом ключа, разрешающий вход которого является входом устройства, запрещающий вход соединен с выходом счетчика аргумента, а выход ключа соединен со входом счетчиков первого и второго двоичных умножителей, вход дещифратора первого Двоичного умножителя соединен с выходом регистра сдвига, вход которого соединен с выходом старшего разряда ctjeTraKa второго двоичного умножителя, выход элемента ИЛИ первого двоичного умножителя соединен со входом счетчика аргумента, отличающееся тем, что, с целью повыщения точности, оно со-, держит третий двоичный умножитель, состоящий также из счетчика, дещифратора и элемента ИЛИ, и блок коррекции, включающий счетчик, дешифратор, блок памяти, триггер и сумматор, причем выход счегшка второго двоичного умножителя соединен со входом счетчика блока коррекции, выход которого через триггер соединен с первым входом сумматора, а выходы разрядов счетчика блока коррекции через дещифратор блока коррекции и блок памяти сосоединены со входом дешифратора третьего двоиного умножителя, выход элемента ИЛИ которого подключен ко второму входу сумматора, третий вход которого соединен с информационным выходом второго двоичного умножителя, а выход сумматора подключен ко входу счетчика результата.

Источники информации, принятые во внимание при экспертизе

1.Браго Б. Н. Методы и устройства цифррвого преобразоваштя информации. М., Недра, 1976, с. 58, рис; 25.

2.Мельников А. А. и др. Обработка частотных и временных импульсных сигналов. М., Энергия, 1976, с. 96, рис. 8 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1008749A1 |

| Устройство для воспроизведения экспоненциальных функций | 1977 |

|

SU618746A1 |

| Устройство для вычисления логарифмических функций | 1980 |

|

SU934469A1 |

| Устройство для воспроизведенияфуНКций | 1979 |

|

SU809200A1 |

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Устройство для извлечения корня | 1985 |

|

SU1273922A1 |

| Устройство для вычисления параболических функций | 1980 |

|

SU943719A1 |

| Устройство для вычисления функций | 1977 |

|

SU736115A1 |

| Устройство для вычисления обратных функций | 1980 |

|

SU942007A1 |

| Устройство для воспроизведения кардиоиды | 1981 |

|

SU1007102A1 |

Авторы

Даты

1980-10-15—Публикация

1978-12-26—Подача