Недостатком устройства является малая устойчивость к временным смещениям между каналами.

Целью изобретения является повышение достоверности восстановления информации и увеличение устойчивости к временным смещениям между каналами.

Цель достигается тем, что в устройство введены дополнительный информационный канал, аналогичный информационным, и блок проверки на четкость и исправления ошибок, при этом в ка;вдый информационный канал введены корректор переходных характеристик, схема выделения выпаданий, бло фазирования сигнала выпаданий, блок выделения маркерного слова, три логических элемента И, счетчик адресо занесения, счетчик адресов считывания и два блока па-мяти, а в опорный канал введены корректор переходных, характеристик, схема выделения выпаданий, блок восстановления синхроимпульсов и блок вьвделения маркера, выход которого подключен к рбнуляю1ЧИМ входам счетчиков адресов считывания каждого информационного канала при этом выход формирователя импульсов опорного канала соединен с первыми входами блока выделения маркера и ,блока восстановления синхр6- импульсов, а выход схемы выделения выпаданий опорного канала подключен ко вторым входам блока восстановления синхроимпульсов и блока вьщеления маркера, приче,м выход блока умно жения частоты подсоединен к третьему входу блока восстановления синхроимпульсов и к одному из входов декодера информационного канала,.при этом выходы корректоров переходных характеристик каждого канала подключены к формирователям иглпульсов и схемам выделениявыпаданий каждого канала, а выходы схем выделения выпаданий информационных каналов через блоки фазирования сигналов выпаданий соединены с третьими входами декодеров, со BTOpbCvm входами блоков выделения маркерного слова и первыми входами первых логических элементов И, причем к первым входам блоков выделения маркерного слова . подключены выходы формирователей импульсов, а выходы декодеров подключены к первым входам вторых и т ретьих логических элементов И, при этом первые выходы блоков выделения маркерных слов соединены со вторыми входами трех логических элементов И, вторые вЬоходы соединены с обнуляющими входами счетчиков адресов занесения а выходы вторых и первых элементов И подключены к первым входам блоков памяти, причем выходы третьих логических элементов Н через счетчики адресов занесения своих каналов

соединены со ьторыми входами памяти тех же каналов, а третьи входы блоков памяти связаны с выходами счетчиков адресов считывания, при этом их входы соединены с выходом блока восстановления синхроимпульсов , а выходы блоков памяти каждого информационного канала подключены к соответствующим входам блока проверки на чет1ость и исправления ошибок.

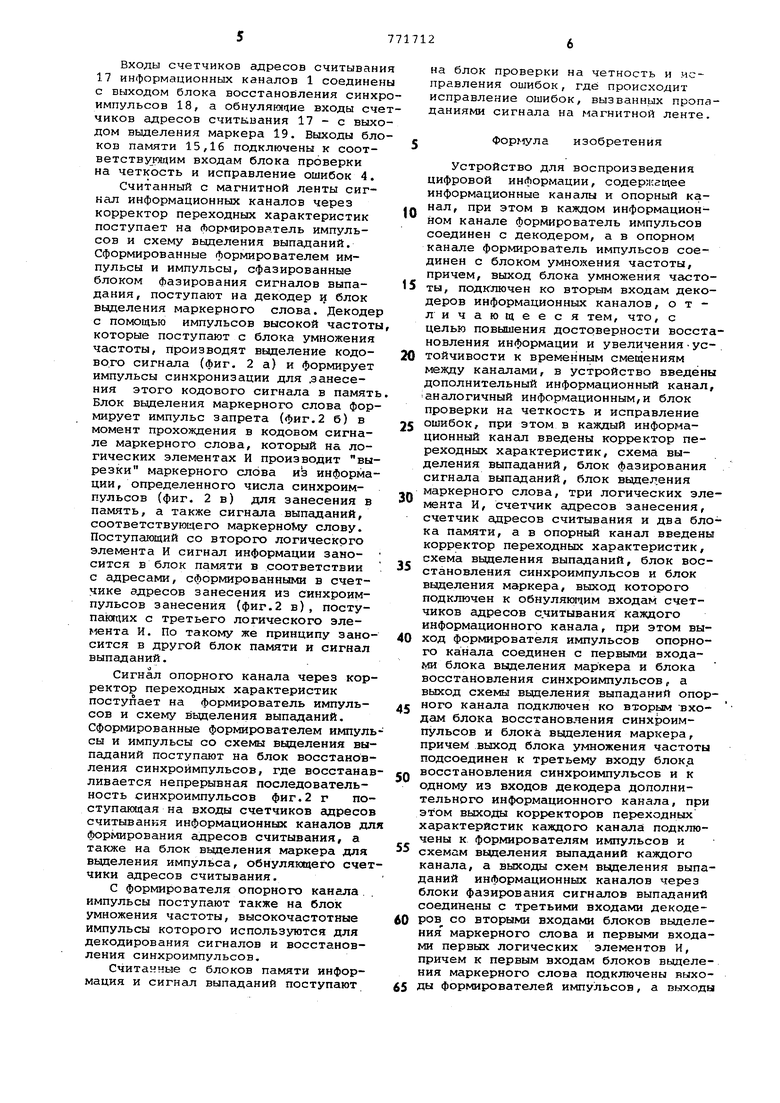

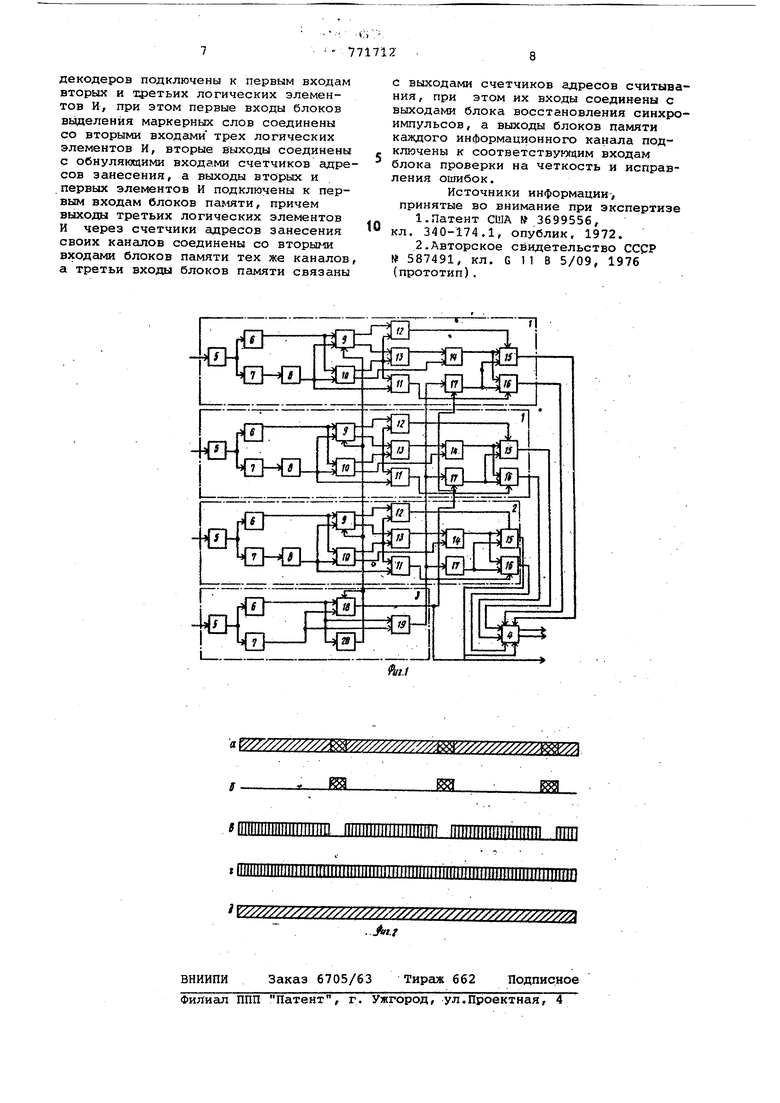

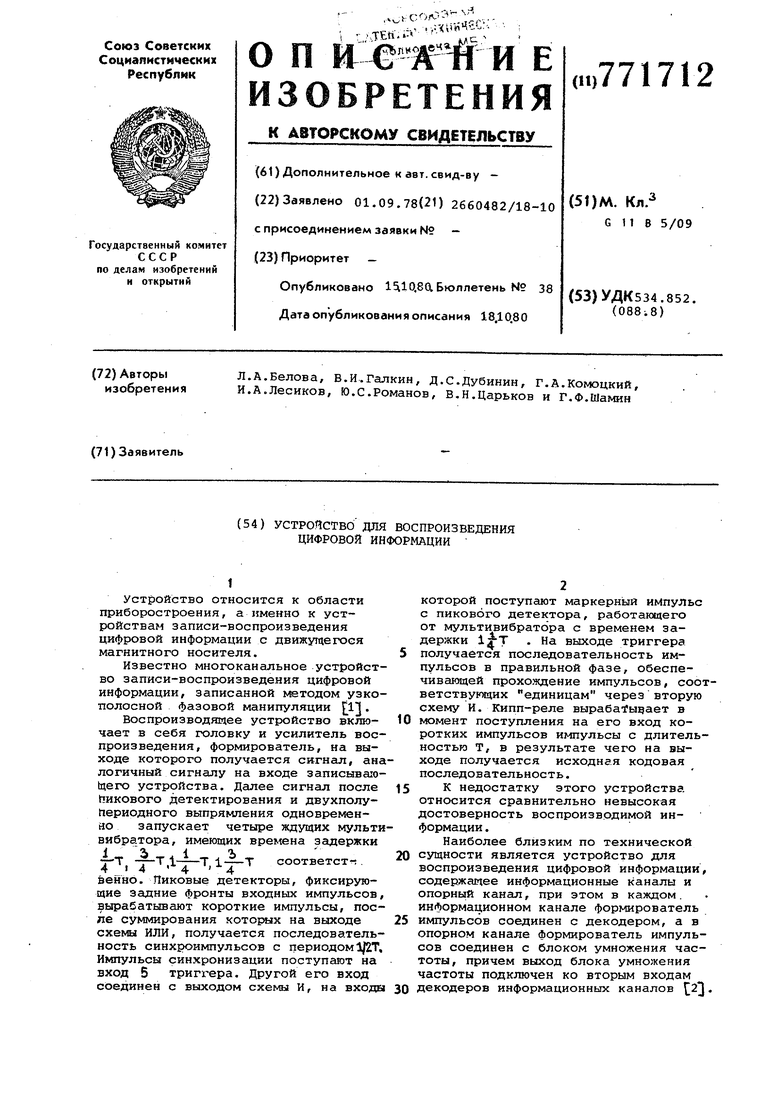

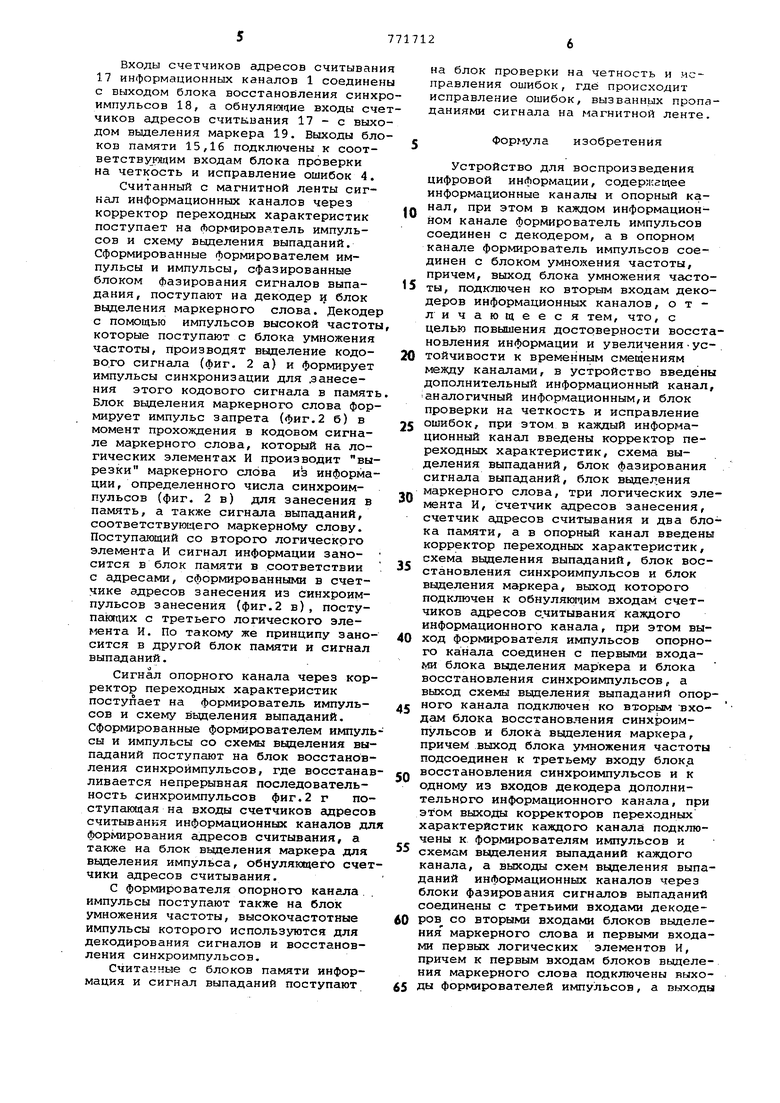

На фиг. 1 изобра кена функциональная схема устройства, на фиг. 2 временные диаграммы устройства.

Устройство содержит информационные каналы 1, дополнительный инфор5 мациоиный канал 2, аналогичный информационному 1, опорный канал 3 и блок проверки на четкость и исправления ошибок 4.

Каждый информационный канал 1,2 состоит из корректора переходных ха.рактеристик 5, выход которого подключен ко входу формирователя импульсов 6 и через схему выделения выпаданий 7 и блок фазирования сигнала выпаданий 8 к третьему входу декодера 9, второму входу блока выделения маркерного слова 10 и первому входу логического элемента И 11. Выход формирователя импульсов 6 соединен с первыгли входами декодера 9 и блока выделения маркерного слова 10, первый выход декодера 9 --с первым входом логического элемента И 12, второй выход декодера 9 - с первым входом логического элемента И 13,первый ВЫХОД блока вьщеления маркерного слова 10 - со вторыми входами логических элементов И 11, 12,13, а второй выход - с обнуляющим входом счетчика адресов занесения 14. Выход логического элемента И 12 подключен к первому входу бЛока памяти 15, выход логического элемента И 11 - к первому входу блока памяти 16, а выход логического элемента И 13 через счетчик адресов занесения 14 - ко вторым входам «локов памяти 15,16. Третьи входы блоков памяти 15,16 подключены к выходу счетчика адресов считывания 17.

Опорный канал 3 содержит корректо переходных характеристик 5, выход которого подключен к входу формирователя импульсов 6 и через схему вьщеления выпаданий 7 - ко вторым входам блока восстановления синхроимпульсов 18 и блока вьаделения маркера 19. Выход формирователя импульсов 6 соединен с первыми входами блока восстановления синхроимпульсов 18, блока выделения маркера 19 и со входом блока умножения частоты 20, выход которого подключен к третьим входам блока восстановления синхроимпульсов 18 и декодерам 9 информационных каналов 1,2.

Входы счетчиков гщресов считывани 17 информационных каналов 1 соединен с выходом блока восстановления синхримпульсов 18, а обнулякхчие входы счечиков адресов считывания 17 - с выходом вьщеления маркера 19. Выходы блоков памяти 15,16 подключены к соответствующим входам блока проверки на четкость и исправление ошибок 4.

Считанный с магнитной ленты сигнгш информационных каналов через корректор переходных характеристик поступает на фop иpoвaтeль импульсов и схему вьщеления выпаданий. Сформированные формирователем импульсы и импульсы, сфазированные блоком фазирования сигналов выпадания, поступают на декодер и блок вьщеления маркерного слова. Декодер с помощью импульсов высокой частоты которые поступают с блока умножения частоты, производят выделение кодового сигнала (фиг. 2 а) и формирует импульсы синхронизации для .занесения этого кодового сигнала в память Блок выделения маркерного слова формирует импульс запрета (фиг.2 б) в момент прохождения в кодовом сигнале маркерного слова, который на логических элементах И производит вырезки маркерного слова из информации, определенного числа синхроимпульсов (фиг. 2 в) для занесения в память, а также сигнала выпаданий, соответствующего маркерноК1у слову. Поступающий со второго логического элемента И сигнал информации заносится в блок памяти в соответствии с адресами, сформированными в счетчике адресов занесения из синхроимпульсов занесения (фиг.2 в), поступакяпих с третьего логического элемента И. По такому же принципу заносится в другой блок памяти и сигнал выпаданий.

Сигнал опорного канала через корректор переходных характеристик поступает на формирователь импульсов и схему выделения выпаданий. Сформированные формирователем импульсы и импульсы со схемы вьвделения выпаданий поступают на блок восстановления синхроимпульсов, где восстанавливается непрерывная последовательность синхроимпульсов фиг.2 г поступающая на входы счетчиков адресов считывания информационных каналов дл формирования адресов считывания, а также на блок выделения маркера для выделения импульса, обнуляюще1О счетчики адресов считывания.

С формирователя опорного канала. . импульсы поступают также на блок умножения частоты, высокочастотные импульсы которого использ5тотся для декодирования сигналов и восстановления синхроимпульсов.

Считанные с блоков памяти информация и сигнал выпаданий поступают

на блок проверки на четность и исправления ошибок, где происходит исправление ошибок, вызванных пропаданиями сигнала на 1aгнитнoй ленте.

Формула изобретения

Устройство для воспроизведения цифровой информации, содержгщее информационные каналы и опорный канал, при этом в каждом информационoном канале формирователь импульсов соединен с декодером, а в опорном канале формирователь импульсов соединен с блоком умножения частоты, причем, выход блока умножения часто5ты, подключен ко вторым входам декодеров информационных каналов, о т личаюгцееся тем, что, с целью повышения достоверности восстановления информации и увеличенияус-.

0 тойчивости к временным смещениям между каналами, в устройство введены дополнительный информационный канал, аналогичный информационным,и блок проверки на четкость и исправление ошибок, при этом в каждый информа5ционный канал введены корректор переходных характеристик, схема выделения выпаданий, блок фазирования сигнала выпаданий, блок вьщеления маркерного слова, три логических эле0мента И, счетчик адресов занесения, счетчик адресов считывания и два блока памяти, а в опорный канал введены корректор переходных характеристик, схема выделения выпаданий, блок вос5становления синхроимпульсов и блок вьщеления маркера, выход которого подключен к обнуляющим входам счетчиков адресов считывания каждого информационного канала, при этом вы0ход формирователя импульсов опорного канала соединен с первыми входами блока вьщеления маркера и блока восстановления синхроимпульсов, а выход схемы вьщеления выпаданий опорного канала подключен ко вторым вхо5дам блока восстановления синхроимпульсов и блока; вьщеления маркера, причем выход блока умножения частоты подсоединен к третьему входу блока восстановления синхроимпульсов и к

0 одному из входов декодера дополнительного информационного какала, при этом выходы корректоров пеЕ еходных характеристик каждого кангша подключены к формирователям импульсов и

5 схемам вьаделения выпгщаний каждого канала, а выходы схем вьщеления выпаданий информационных каналов черюз блоки фазирования сигналов выпаданий соединены с третьими входами декодеров со вторыми входами блоков выделе0ния маркерного слова и первыми входами первых логических элементов И, причем к первым входам блоков выделения маркерного слова подключены выходы формирователей импульсов, а выходы

5

декодеров подключены к первым входам вторых и третьих логических элементов И, при этом первые входы блоков выделения маркерных слов соединены со вторыми входами трех логических элементов И, вторые выходы соединены с обнуляющими входами счетчиков адресов занесения, а выходы вторых и первых элементов И подключены к первым входам блоков , причем выходы третьих логических элементов И через счетчики адресов занесения своих каналов соединены со вторыми входами блоков памяти тех же каналов а третьи входы блоков памяти связаны

с выходами счетчиков адресов считывания , при этом их входы соединены с выходами блока восстановления синхроимпульсов , а выходы блоков памяти каждого информационного канала подключены к соответствующим входам блока проверки на четкость и исправления ошибок.

Источники информации , принятые во внимание при экспертизе

1.Патент США № 3699556, кл. 340-174.1, опублик, 1972.

2.Авторское свидетельство ССРР № 587491, кл. G 11 В 5/09, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство для записи цифровой информации | 1978 |

|

SU765870A1 |

| Способ цифровой магнитной записи и устройство для записи и воспроизведения цифровой информации | 1985 |

|

SU1298797A1 |

| Многоканальное устройство длязАпиСи и ВОСпРОизВЕдЕНияиНфОРМАции | 1979 |

|

SU822251A1 |

| Способ многоканальной магнитной записи сигналов цифровой информации | 1983 |

|

SU1120398A1 |

| Устройство для детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи | 1986 |

|

SU1327172A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Устройство для цифровой магнитной записи | 1984 |

|

SU1195379A1 |

| Устройство для воспроизведения цифровой магнитной записи | 1987 |

|

SU1458885A1 |

aV/7//// //y/ W

Авторы

Даты

1980-10-15—Публикация

1978-09-01—Подача