1

Изобретение относится к импульсной технике и может быть использовано в системах многопоэиционного автоматического регулирования ступенчатого включения и выключения.5

Известен реверсивный счетчик импульсов, содержащий триггерные ячейки, каждая из которых состоит из реле памяти, диодов, резистора ij ,

Недостатком счетчика является низ-10 кая помехоустойчивость.

Известен также двоичный двухвходовый реверсивный счетчик импульсов, содержащий реле, резисторы, диоды, суммирующую и вычИтаюцую шины 23. 15 Недостаткс1ми такого счетчика являются невысокая достоверность функционирования из-за критичности и длительности входных импульсов, а также ограниченная область применения, по- 20 скольку он может работать только от источника постоянного напряжения и не переходит в нулевое состояние при выключении питающего напряжения,

Целью изобретения является повы- 25 шение достоверности функционирования счетчика и расширение области его применения.

Для достижения поставленной цели в двоичный двухвходовый реверсивный 30

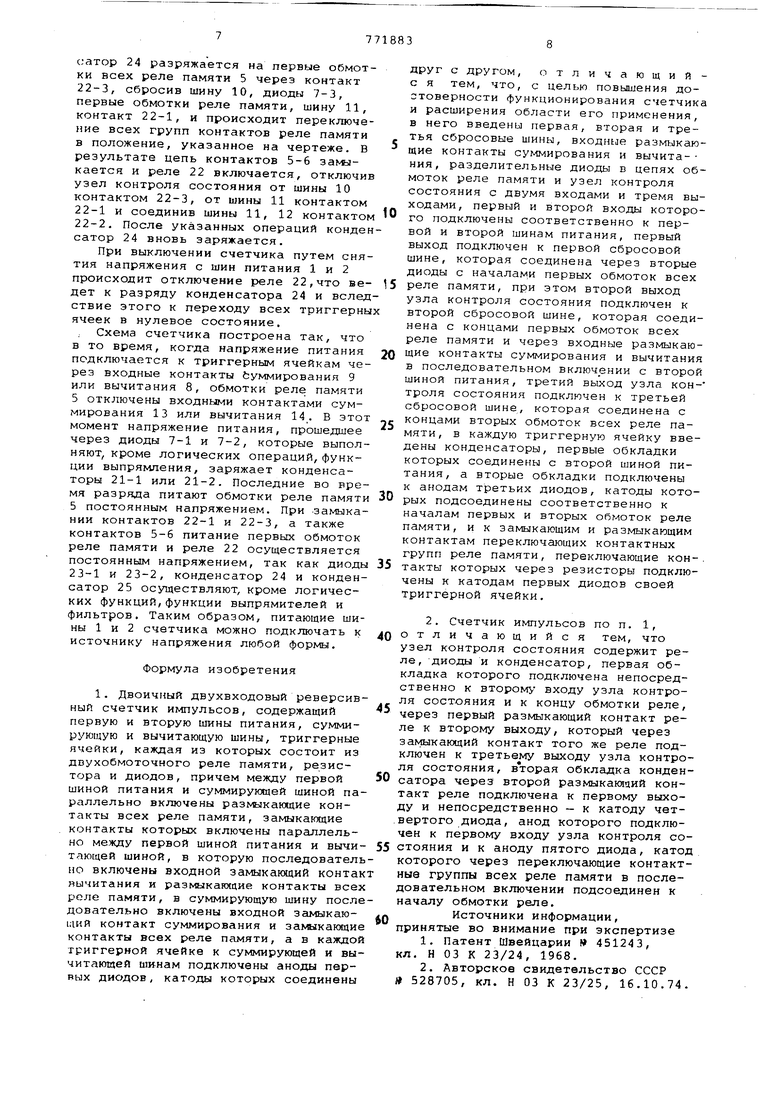

счетчик импульсов, содержащий первую и вторую шины питания, суммирукмаую и вычитающую шины, триггерные ячейки, каждая из которых состоит из двухсбмоточиого реле памяти, резистора и диодов, причем между первой шиной питания и суммирующей шиной параллельно включены размыкающие контакты всех реле памяти, замыкающие контакты которых включены параллельно между первой шиной питания и вычитающей шиной, в которую последовательно включены входной замыкающий контакт вычитания и размыкающие контакты всех реле памяти, в суммирующую шину последовательно включены входной закыкающий контакт суммирования и згоФлкающие контакты всех реле памяти, а в каждой триггерой ячейке к суммирукмцей и вычитающей шинам подключены аноды первых диодов, катоды которых соединены друг с другом, введены первая, вторая и третья сбросовые шины, входные размыкающие контакты суммирования и вычитания, разделительные диоды в цепях обмоток реле памяти и узел контроля состояния с двумя входами и тремя выходами. Первый и второй входы узла контроля состояния подключены соответственно к первой и второй шинам питания, пер вый выход подключен к первой сбросовой шине, которая соединена через вторые диоды с началами первых обмоток всех реле памяти, второй выход узла контроля состояния подключен к второй сбросовой шине, которая соеди нена с концами первых обмоток всех реле памяти и через входные размыкаю щие контакты суммирования и вычитани в последовательном включении с второ шиной питания, третий выход узла кон троля состояния подключен к третьей сбросовой шине, которая соединена с концами вторых обмоток всех реле памяти. При этом в каждую триггерную ячейку введены конденсаторы, первые обкладки которых соединены с второй шиной питания, а вторые обкладки под ключены к анодам третьих диодов, катоды, котсэрых подсоединены соответственно к началам первых и вторых обмо ток реле памяти, и к замыкакадим и размыкающим контактам переключающих контактных групп реле памяти, переключакяцие контакты которых через сво резисторы подключены к катодам первых диодов своей триггерной ячейки. Узел контроля состояния содержит реле, диоды и конденсатор, первая обкладка которого подключена непосре ственно к второму входу узла контрол состояния и к концу обмотки реле, че рез первый разкыканиций контакт, реле к второму выходу, которалй через замы кающий контакт того же реле подключе к третьему выходу узла контроля сост яния, при этом вторая обкладка конденсатора через второй размыкающий контакт реле подключена к первому вы ходу и непосредственно - к катоду че вертого диода, анод которого подключ к первому входу узла контроля состоя ния и к аноду пятого диода, катодом подсоединенного через переключающие контактные группы всех реле памяти в последовательном включении к началу обмотки реле. На чертеже представлена схема дво ичного двухвходового реверсивного счетчика импульсов, содвржгицего шины питания 1 и 2, суммирующую и вычитаю щую шины 3 и 4, триггерные ячейки, каждая из который состоит из двухобмоточного реле памяти 5, резистора 6 и диодов 7-1 и 7-2. Между шиной питания 1 и суммируквдей шиной параллельно включены разныкакяцие контакты 5-1 всех реле памяти 5, замыкающие контакты 5-2 которых включены параллельно между шиной питания 1 и вычитающей шиной. В вычитающую шину последовательно включены входной замыкающий контакт вычитания 8 и размыкающие контакты 5-3 всех реле памяти 5,в суммирующую шину 3 последовательно включены входной заиллк ющий контакт суммирования 9 и залыка кшие контакты 5-4 всех реле памяти, каждой триггерной ячейке к сумг отрующей и вычитающей шинам 3 и 4 подключены аноды диодов 7-1 и 7-2, катоды которых соединены друг с другом. Счетчик импульсов содержит также сбросовые шины 10, 11 и 12, входные размыкающие контакты суммирования и вычитания 13 и 14, разделительные диоды 7-3, 7-4 и 7-5 в цепях обмоток реле памяти 5 и узел контроля состояния 15 с двумя входами 16, 17 и тремя выходами 18, 19 и 20. Входы 16и 17 подключены соответственно к шинам питания 1 и 2, выход 18 подключен к сбросовой шине 10, которая соединена через диоды 7-3 с началами первых обмоток всех реле памяти 5, выход 19 подключен к сбросовой шине 11, которая соединена с концами первых обмоток всех реле памяти и через входные размлкающие контакты суммирования 13 и вычитания 14 в последовательном включении с шиной питания 2, выход 20 подключен к сбросовой шине 12, которая соединена с концами вторых обмоток и всех реле памяти 5. В каждую триггерную ячейку введены конденсаторы 21-1 и 21-2, первые обмотки которых соединены с шиной питания 2, а вторые обкладки подключены к анодам диодов 7-4 и 7-5, катоды которых подсоединены . соответственно к началам первых и вторых обмоток реле пагляти, и к замыкакхцим и размыкающим контактам переключанждих контактных групп 5-5 реле памяти переключающие контакты которых через свои резисторы подключены к катодам диодов 7-1 и 7-2 своей триггерной ячейки. Кроме тогчэ, узел контроля состояния двоичного двухвходового реверсивного счетчика импульсов содержит реле 22, диоды 23-1 и 23-2 и конденсаторы 24, первая обкладка которого подключена непосредственно к входу 17и к концу обмотки реле 22, через размыкающий контакт 22-1 реле 22 к выходу 19, который через замыкающий контакт 22-2 реле 22 подключен к выходу 20. Вторая оезкладка конденсатора 24 через размыкающий контакт 22-3 реле 22 подключена к выходу 18 и непосредственно - к катоду диода 23-1 анод которого подключен к входу 16 и к аноду диода 23-2, катодом подсоединенного через переключающие контактные группы 5-6 всех реле памяти 5 в последовательном включении к началу обмотки реле 2 2. Устройство работает следующим образом. В первоначальном состоянии все реле выключены и находятся в состоянии указанном на чертеже. При подаче напряжения на шины питания 1 и 2 через диод 23-1 заряжается конденсатор 24. В случае, если контакты всех реле памяти 5 наисодятся в одном из крайних полЬжений, через диод 23-2 и

переключающие контактные группы 5-6 всех реле памяти включается реле 22, его контакты 22-1 и 22-3 разг ыкаются а контакт 22-2 заг-влкается. Команда на суммирование и вычитание поступает в виде импульсов замыканием входных контактов суммирования 9 или вычитания 8, при этом один из контактов 13 или 14 размыкается. При поступлении команды на вычитание устройство не меняет своего состояния, так как цепь с шиной питания 1 разомкнута через контакты 5-2 всех реле памяти счетчика.

При заг-икании входного контакта 9 и размыкании входного контакта 13 суммирования заряжается конденсатор 21-2 первой по порядку триггерной ячейки по цепи: шина питания 1, контакты 5-1 всех реле памяти 5, контакт 9, диод 7-1, резистор 6, размыкающий контакт переключающей контактной группы 5-5, конденсатор 21-2, шина питания 2. При этом по обмоткам всех реле памяти ток протекать не может, так как они отключены от шины питания 2 входным размыкакяцим контактом суммирования 13.После снятия команды на суммирование, т. е размыкания входного контакта суммирования 9 и замыкания входного контакта суммирования 13, вследствие разряда конденсатора 21-2 срабатывает вторая обмотка реле памяти 5 первой триггерной ячейки по цепи: первая обкладка конденсатора 21-2, диод 7-5, вторая обмотка реле памяти 5, сбросовая шина 12, контакты 22-2, 13, 14, шина питания 2, вторая обкладка конденсатора 21-2.. При этом затолкаются контакты 5-2 и 5-4 реле памяти первой триггерной ячейки, разуыкаются контакты 5-1 и 5-3 реле памяти первой триггерной ячейки переключаквдая контактная группа 5-5 реле первой триггерной ячейки переключается в цепь конденсатора 21-1. Таким образом, первая триггерная ячейка переходит в единичное состояние.

При замыкании входного контакта вычитания 8 и размыкании входного контакта вычитания 14 заряжается конденсатор 21-1 первой триггерной ячейки, так как образуется цепь: шина питания 1, контакты 5-2 всех реле памяти 5 счетчика, контакт 8, диод 7-2, резистор б,- эамыкакнций контакт переключаквдей контактной группы 5-5 первой триггерной ячейки, конденсатор 21-1, шина питания 2. При этом по обмоткам всех реле паbWiTH ток протекать не может, так как они отключены от шины питания 2 входным раз1квлкс1квдим контактом вычитания 14. После снятия команды на вычитание, т. ё. разгллкання входного контакта вычитания 8 и заквякания входно о j oHTaKTa вьачитания 14, Bca&j ствке разряда конденсатора 21-1 ерабатывает первая обмотка реле памяти 5 первой триггерной ячейки по цепи: первая обкла,цка кокдансатора 21-1, циод 7-4, первая обмотка реле памяти 5, шина 11, контакты 13.- 14,, шина 2, вторая обкладкз кокденсатора 21-1. При этом за№ ткагатся контакты 5-1 и 5-3 первой триггерной ячейки, размыкаются контакты 5-2. и 5-4, переключающая контактная группа 5-5 первой триггерной ячейки переключается в цепь конденсатора 21-2. Таким образом, первая триггерная ячейка переходит в нулевое состоякие.

Если после первой команды на суммирование приходит вторая команда

5 на cyм кpoвaниe, то первая триггерная ячейка переходит в нулевое состояние, но одновременное вторая триггерная ччейка перехолит в единичное состояние, так как контакт 5-4 первой триггерной ячейки замкнут после прохождения первой командьа на суммирование. После прохождения семи команд на суммирование три первые триггерные ячейки находятся в единичном состоянии, а последняя триггерная ячейка

5 находится в нулевом состоянии. Размыкающие контакты 5-3 реле памяти 5 первьдх трех триггерных ячеек разомкчуты, а их замыкающие контакты 5-4 замкнуты. После прохождения пятнад0цатой команды на суммирование все триггерные ячейки переходят в единичное состояние, при этом контакты 5-1 реле памяти 5 всех триггерных ячеек оказываются разомкнутыми, вследствие

5 чего дальнейшее прохождение команд на суммирование невозможно.

В случае, если длительность команды на суммирование или вычитание оказывается меньше заданной, т. е. контакты суммирования 9, 13 и вычитания

0 8, 14 дают помеху, после замыкания контактов 13 и 14 происходит разряд конденсаторов 21-1 и 21-2 на обмотку реле памят-и 5, однако оно своего состояния не изменяет, так как в этом

5 случае конденсаторы 21-1 и 21-2 заряжаются до напряжения меньшего, чем напряжение срабатывания реле памяти. Фильтр помехи настраивается на заданное время заряда конденсатора путем

изменения-сопротивления резисторов 6.

контроля состояния 15 работает следукедим образом.

При переключении контактов реле памяти 5 из одного положейия в другое

5 размыкается иепь переключающих контактов 5-6 реле памяти и реле 22 обесточивается. Однако контакты 22-1, 22-2 и 22-3 реле 22 остаются в прежнем положении, так как реле 22 имеет задержОку на отпускание. В случае, если длительность переключения койтактов реле памяти превышает время задержки отпускания реле 22, происходит замыкание контактов 22-1 и 22-3 и разкикание контакта 22-2. При этом конден$с;атор 24 разряжается на первые обмотки всех реле памяти 5 через контакт 22-3, сбросив шину 10, диоды 7-3, первые обмотки реле памяти, шину 11, контакт 22-1, и происходит переключение всех групп контактов реле памяти в положение, указанное на чертеже. В результате цепь контактов 5-6 замыкается и реле 22 включается, отключив узел контроля состояния от шины 10 контактом 22-3, от шины 11 контактом 22-1 и соединив шины 11, 12 контактом 22-2. После указанных операций конден сатор 24 вновь заряжается. При выключении счетчика путем снятия напряжения с шин питания 1 и 2 происходит отключение реле 22,что ведет к разряду конденсатора 24 и вслед ствие этого к переходу всех триггерны ячеек в нулевое состояние. Схема счетчика построена так, что в то время, когда напряжение питания подключается к триггерным ячейкам через входные контакты йу «п ирования 9 или вычитания 8, обмотки реле памяти 5 отключены входными контактами суммирования 13 или вычитания 14. В этот момент напряжение питания, прошедшее через диоды 7-1 и 7-2, которые выполняют, кроме логических операций, функции выпрямления, заряжает конденсаторы 21-1 или 21-2. Последние во время разряда питают обмотки реле памяти 5 постоянным напряжением. При -замыкании контактов 22-1 и 22-3, а также контактов 5-6 питание первых обмоток реле памяти и реле 22 осуществляется постоянным напряжением, так как диоды 23-1 и 23-2, конденсатор 24 и конденсатор 25 осуществляют, кроме логических функций,функции выпрямителей и фильтров. Таким образом, питающие шины 1 и 2 счетчика можно подключать к источнику напряжения любой формы. изобретения 1. Двоичный двухвходовый реверсивный счетчик импульсов, содержащий первую и вторую шины питания, суммирующую и вычитающую шины, триггерные ячейки, каждая из которых состоит из двухобмоточного реле памяти, резистора и диодов, причем между первой шиной питания и суммирующей шиной параллельно включены размыкающие контакты всех реле памяти, замыкающие контакты которых включены параллельно между первой шиной питания и вьлчитающей шиной, в которую последователь но включены входной замыкающий контак вычитания и размыкающие контакты всех реле памяти, в суммирующую шину после довательно включены входной замыкаю1.ЧИЙ контакт суммирования и замыкающие контакты всех реле памяти, а в каждой триггерной ячейке к суммирующей и вычитающей шинам подключены аноды первых диодов, катоды которых соединены друг с другом, отличающийс я тем, что, с целью повышения достоверности функционирования счетчика и расширения области его применения, в него введены первая, вторая и третья сбросовые шины, входньле размыкающие контакты суммирования и вычита- ния, разделительные диоды в цепях обмоток реле памяти и узел контроля состояния с двумя входами и тремя выходами, первый и второй входы которого подключены соответственно к первой и второй шинам питания, первый выход подключен к первой сбросовой шине, которая соединена через вторые диоды с началам и первых обмоток всех реле памяти, при этом второй выход узла контроля состояния подключен к второй сбросовой шине, которая соединена с концами первых обмоток всех реле памяти и через входные размыкающие контакты суммирования и вычитания в последовательном включении с второй шиной питания, третий выход узла контроля состояния подключен к третьей сбросовой шине, которая соединена с концами вторых обмоток всех реле памяти, в каждую триггерную ячейку введены конденсаторы, первые обкладки которых соединены с второй шиной питания, а вторые обкладки подключены к анодам третьих диодов, катоды которых подсоединены соответственно к началам первых и вторых обмоток реле памяти, и к замыкающим и размыкающим контактам переключающих контактных групп реле памяти, переключающие кон-. такты которых через резисторы подключены к катодам первых диодов своей триггерной ячейки. 2. Счетчик импульсов по п. 1, отличающийся тем, что узел контроля состояния содержит реле, диоды и конденсатор, первая обкладка которого подключена непосредственно к второму входу узла контроля состояния и к концу обмотки реле, через первый размыкающий контакт реле к второму выходу, который через замыкающий контакт того же реле подключен к третьему выходу узла контроля состояния, вторая обкладка конденсатора через второй размыкакиаий контакт реле подключена к первому выходу и непосредственно - к катоду четвертого диода, анод которого подключен к первому входу узла контроля состояния и к аноду пятого диода, катод которого через переключающие контактные группы всех реле памяти в последовательном включении подсоединен к началу обмотки реле. Источники информации, принятые во внимание при экспертизе 1.Патент Швейцарии 451243, кл. Н 03 К 23/24, 1968. 2.Авторское свидетельство СССР а 528705, кл. Н 03 К 23/25, 16.10.74. iS ±/8 Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный двухвходовой реверсивный счетчик импульсов | 1974 |

|

SU528705A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

| Десятичный счетчик | 1986 |

|

SU1338067A1 |

| Реверсивный декадный счетчик с памятью | 1978 |

|

SU771882A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ПАМЯТЬЮ | 2006 |

|

RU2321166C1 |

| Релейный распределитель | 1991 |

|

SU1800638A1 |

| Двоичный счетчик | 1990 |

|

SU1725395A1 |

| Реверсивный счетчик импульсов | 1979 |

|

SU1051733A1 |

| Триггер | 1979 |

|

SU864576A1 |

| Многоканальное устройство для последовательного управления агрегатами | 1982 |

|

SU1121648A1 |

Авторы

Даты

1980-10-15—Публикация

1978-09-13—Подача