Изобретение относится к вычислительной технике и предназначено для перевода уплотненных чисел, записанных в троичном коде, в двоичные числа и может быть использовано для экономии количества связей между циф ровыми блоками вычислительной систем Преобразователь используется на приемной стороне цифровых блоков. Известен преобразователь троичного кода 1, О, 1 в двоичный код, содержащий собирательные схемы сигна лов различной полярности, схемы НЕ к: блок одноразрядных сумматоров 1 Известен также преобразователь троичного кода 1, О, 1 в двоичный ход, содержащий тринадцать троичных логических элементов 2. Однако эти преобразователи имеют слож1 Ую реализацию. Наиболее близким к предлагаемому является преобразователь троичного кода 1, О, 1 в двоичный код, содерж щий троичные элементы, причем перва входная шина преобразователя соединена с входами положительных сигналов , а вторая входная шина - с вхоДс1ми отрицательных сигналов первого второго, третьего и четвертого троичных элементов, выход третьего троичного элемента соединен с первым входом положительного сигнала седьмого троичного элемента t- lОднако известный преобразователь троичного кода имеет сложную реализацию, т.е. содержит девять троичных логических элементов. Цель изобретения - упрощение и повышение быстродействия преобразователя. Указанная цель достигается тем, что преобразователь троичного кода 1, О, is двоичный код, содержащий троичные элементы, причем первая входная шина преобразователя соединена с первыми входами положительных сигналов, а вторая входная шина преобразователя соединена с первыми входами отрицательных сигналов первого, второго, третьего и четвертого троичных элементов, выход третьего троичного элемента соединен с первым входом положительныхсигналов пятого троичного элемента, выходы пятого, шестого и седьмого троичных элементов соединены с выходными шинами преобразователя, первая входная шина преобразователя соединена

со BTOpfcJMH входами положительных сигналов первого и третьего троичных элементов, вторая входная шина преобразователя соединена со вторыми входами отрицательных сигналов второго и четвертого троичных элементов выход первого троичного элемента соединен с первым и вторым входами положительных сигналов шестого троичного элемента, с первым входом отрицательных сигналов седьмого троичного элемента и со вторым входом положительных сигналов пятого троичного элемента, выход второго

троичного элемента соединен с первым и вторым входами положительных сигналов седьмого троичного элемента, выход четвертого троичного элемента соединен с первыми входами отрицательных сигналов пятого и шестого троичных элементов.

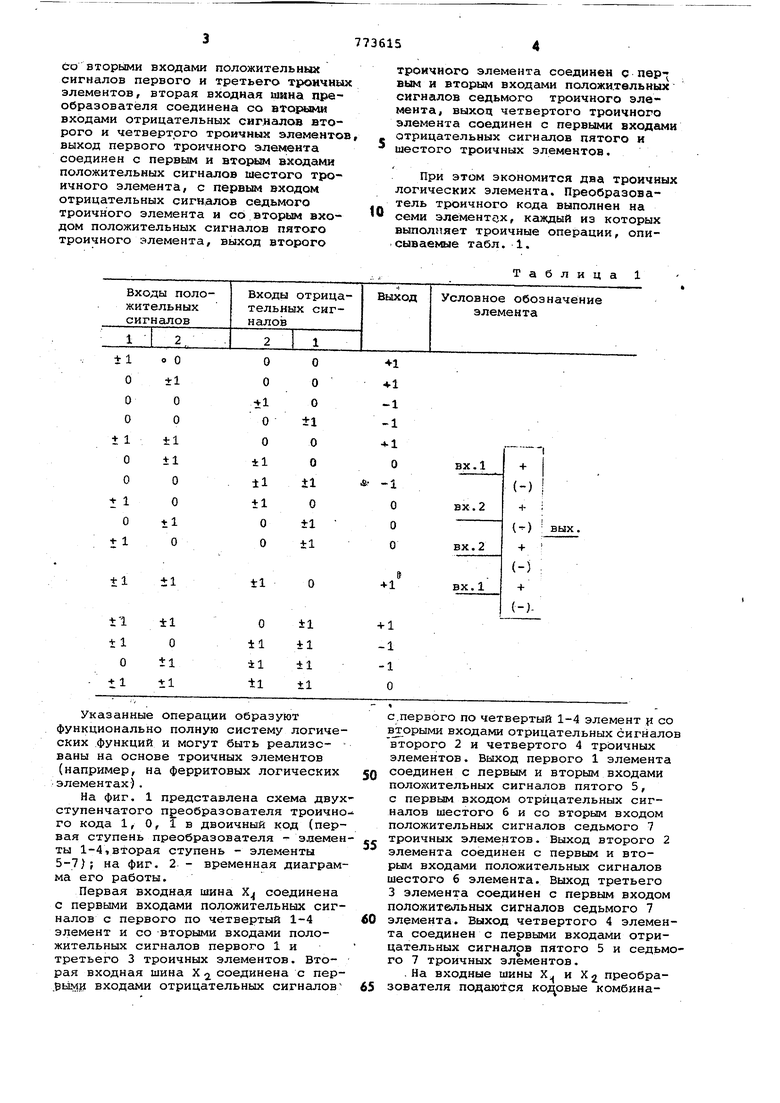

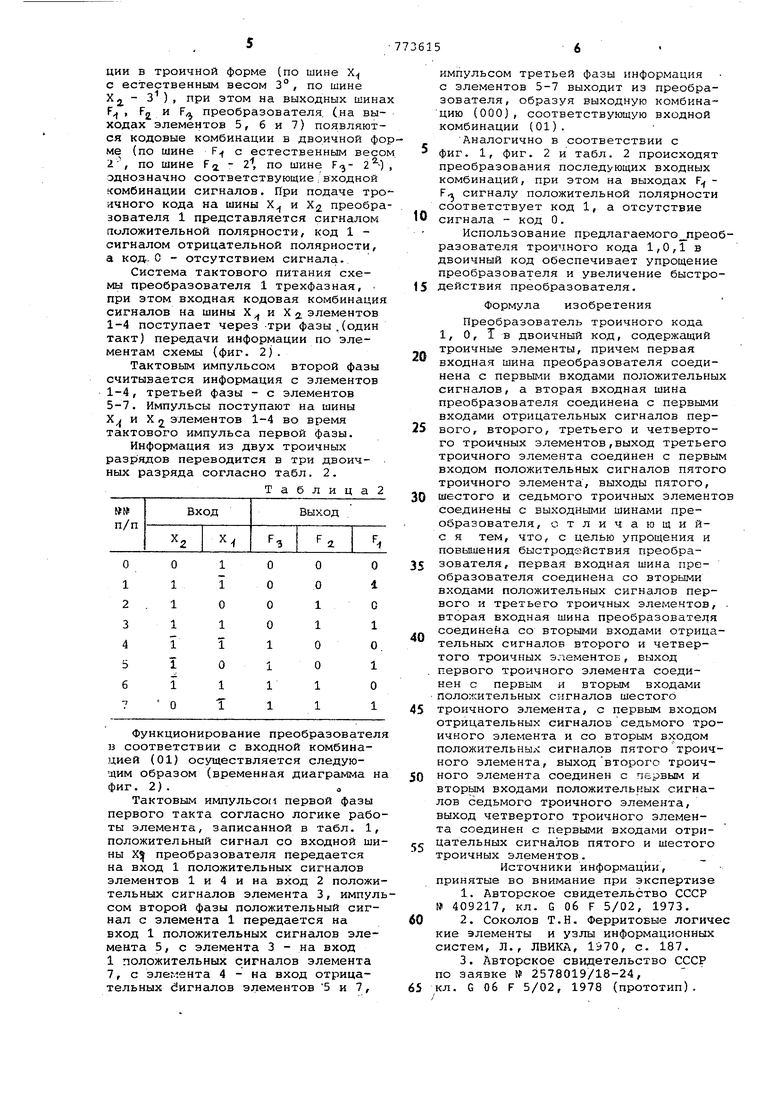

При этом экономится два троичных логических элемента. Преобразователь троичного кода выполнен на семи элементах, каждый из которых выполняет троичные операции, описываемые табл. 1.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Преобразователь двоичного кода в троичный код 1,0,1 | 1978 |

|

SU750477A1 |

| Преобразователь двоично-десятичногоКОдА B КОд ВОСьМиСЕгМЕНТНОгОиНдиКАТОРА | 1979 |

|

SU822172A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1980 |

|

SU898416A1 |

| Преобразователь двоично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1130857A1 |

| Преобразователь двоично-десятичногоКОдА B КОд СЕМиСЕгМЕНТНОгО иНдиКАТОРА | 1978 |

|

SU796836A1 |

| Преобразователь троично-десятичногоКОдА B КОд СЕМиСЕгМЕНТНОгО иНдиКАТОРА | 1979 |

|

SU851393A1 |

| Дешифратор троичного кода 1,0,1 | 1983 |

|

SU1106015A1 |

| Преобразователь троично-десятичного кода в код семисегментного индикатора | 1982 |

|

SU1092488A1 |

| Преобразователь двоичного кодаВ ТРОичНый КОд 1,0,1 | 1979 |

|

SU796838A1 |

Указанные операции образуют функционально полную систему логических функций и могут быть реализс- ваны на основе троичных элементов (например, на ферритовых логических элементах).

На фиг. 1 представлена схема двухступенчатого преобразователя троичного кода 1, О, 1 в двоичный код (первая ступень преобразователя - элементы 1-4,вторая ступень - элементы 5-7); на фиг. 2 - временная диаграмма его работы.

Первая входная шина Х соединена с первыми входами положительных сигналов с первого по четвертый 1-4 элемент и со вторыми входами положительных сигналов первого 1 и третьего 3 троичных элементов. Вторая входная шина X Q соединена с пер.pbLMH входами отрицательных сигналов;

с,первого по четвертый 1-4 элемент и со вт орыми входами отрицательных сигналов второго 2 и четвертого 4 троичных элементов. Выход первого 1 элемента соединен с первым и вторым входами полохсительных сигналов пятого 5, с первым входом отрицательных сигналов шестого 6 и со вторым входом положительных сигналов седьмого 7 троичных элементов. Выход второго 2 элемента соединен с первым и вторым входами положительных сигналов шестого 6 элемента. Выход третьего 3 элемента соединен с первым входом положительных сигналов седьмого 7 элемента. Выход четвертого 4 элемента соединен с первыми входами отрицательных сигналов пятого 5 и седьмого 7 троичных элементов.

.На входные шины Х; и Х2 преобразователя подаются комбинации в троичной форме (по шине Х

с естественным весом 3

по шине

Х2 - 3 ) , при этом на выходных шинах F , F и F преобразователя, (на выходах элементов 5, 6 и 7) появляются кодовые комбинации в двоичной форме {по шине F-f с естественным весом 2 по шине Fa - 2 по шине FKJ- ) , однозначно соответствующие.входной комбинации сигналов. При подаче троичного кода на шины Х и Х2 преобразователя 1 представляется сигналом положительной полярности, код 1 сигналом отрицательной полярности, а код.. С - отсутствием сигнала.

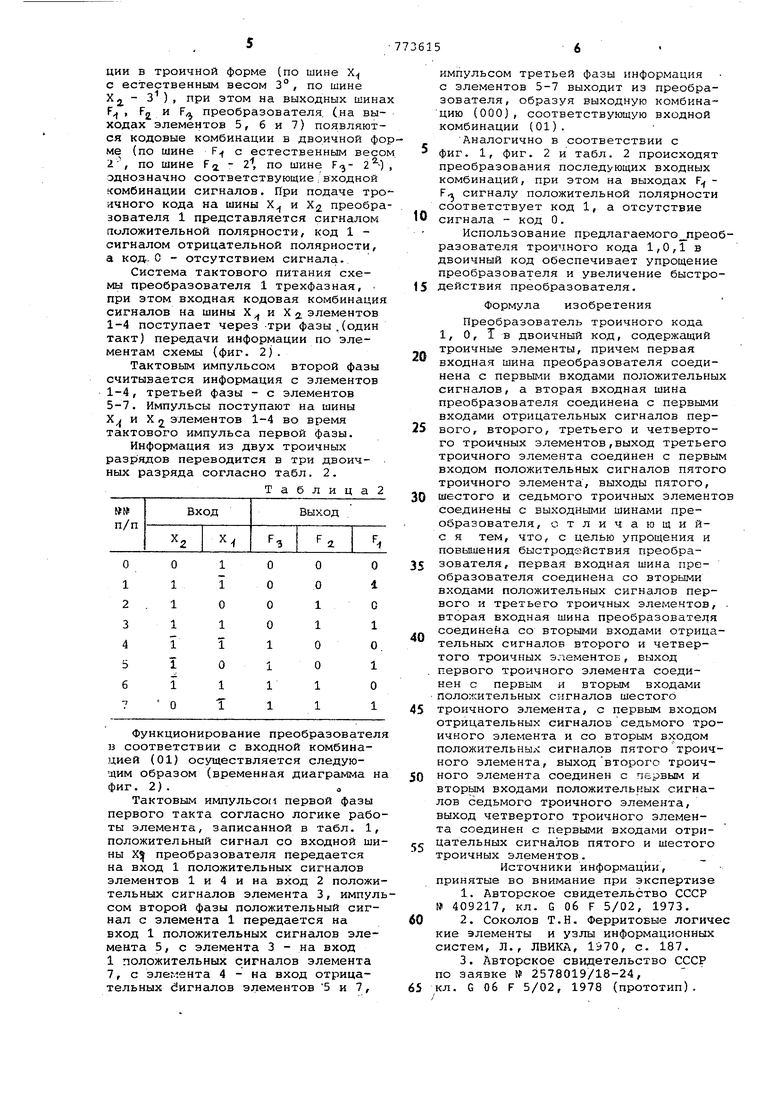

Система тактового питания схемы преобразователя 1 трехфазная, . при этом входная кодовая комбинация сигналов на шины Х и X j. элементов 1-4 поступает через -три фазы Додин такт) передачи информации по элементам схемы (фиг. 2).

Тактовым импульсом второй фазы считывается информация с элементов 1-4, третьей фазы - с элементов 5-7. Импульсы поступают на шины Х и X 2 элементов 1-4 во время тактового импульса первой фазы.

Информация из двух троичных разрядов переводится в три двоичных разряда согласно табл. 2.

Таблица2

Функционирование преобразователя 13 соответствии с входной комбинацией (01) осуществляется следующим образом (временная диагрс1мма на фиг. 2).о

Тактовым импульсоп первой фазы первого такта согласно логике работы элемента, записанной в табл. 1, положительный сигнал со входной шины Х преобразователя передается на вход 1 положительных сигналов элементов 1 и 4 и на вход 2 положительных сигналов элемента 3, импульсом второй фазы положительный сигнал с элемента 1 передается на вход 1 положительных сигналов элемента 5, с элемента 3 - на вход 1 положительных сигналов элемента 7, с элег.ента 4 - на вход отрицательных бигналов элементов 5 и 7,

импульсом третьей фазы информация с элементов 5-7 выходит из преобразователя, образуя выходную комбинацию (000), соответствующую входной комбинации (01).

Аналогично в соответствии с фиг. 1, фиг. 2 и табл. 2 происходят преобразования последующих входных комбинаций, при этом на выходах F F сигналу положительной полярности соответствует код 1, а отсутствие

0 сигнала - код 0.

Использование предлагаемого преобразователя троичного кода 1,0,1 в двоичный код обеспечивает упрощение преобразователя и увеличение быстро5действия преобразователя.

Формула изобретения Преобразователь троичного кода 1, О, Т в двоичный код, содержащий троичные элементы, причем первая

0 входная шина преобразователя соединена с первыми входами положительных сигналов, а вторая входная шина преобразователя соединена с первыми входами отрицательных сигналов пер5вого, второго, третьего и четвертого троичных элементов,выход третьего троичного элемента соединен с первым входом положительных сигналов пятого троичного элемента, выходы пятого,

0 шестого и седьмого троичных элементов соединены с выходными шинами преобразователя, о т л и ч а ю щ и йс я тем, что, с целью упрощения и повышения быстродействия преобразователя, первая входная шина пре5образователя соединена со вторыми входами положительных сигналов первого и третьего троичных элементов, . вторая входная шина преобразователя соединена со вторыми входами отрица0тельных сигналов второго и четвертого троичных элементов, выход первого троичного элемента соединен с первым и вторым входами .положительных сигналов шестого

5 троичного элемента, с первым входом отрицательных сигналов седьмого троичного элемента и со вторым входом положительных сигналов пятоготроичного элемента, выходвторого троичного элемента соединен с первым и

0 вторьом входами положительных сигналов седьмого троичного элемента, выход четвертого троичного элемента соединен с первыми входами отрицательных сигналов пятого и шестого

5 троичных элементов.

Источники информации, принятые во внимание при экспертизе

О

кл. G Об F 5/02, 1978 (прототип).

5

п трея1разногв источние питания

Запись„t1

-- Запись „-f

. С и/п 1вание„0

Считы(лние„ / Считывание,,-1

Авторы

Даты

1980-10-23—Публикация

1979-02-23—Подача