(54) ПРЕОБРАЗОВАТЕЛЬ ДЮИЧНОГО КОДА В ТРОИЧНЫЙ КОД 1,0,1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1979 |

|

SU773615A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

| Преобразователь двоичного кода в троичный код 1,0,1 | 1978 |

|

SU750477A1 |

| Дешифратор двоичного кода | 1983 |

|

SU1125620A1 |

| Преобразователь двоично-десятичногоКОдА B КОд ВОСьМиСЕгМЕНТНОгОиНдиКАТОРА | 1979 |

|

SU822172A1 |

| Преобразователь двоичного кода в троичный код 1,О,1 | 1985 |

|

SU1343552A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1980 |

|

SU898416A1 |

| Преобразователь двоично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1130857A1 |

| Преобразователь двоично-десятичногоКОдА B КОд СЕМиСЕгМЕНТНОгО иНдиКАТОРА | 1978 |

|

SU796836A1 |

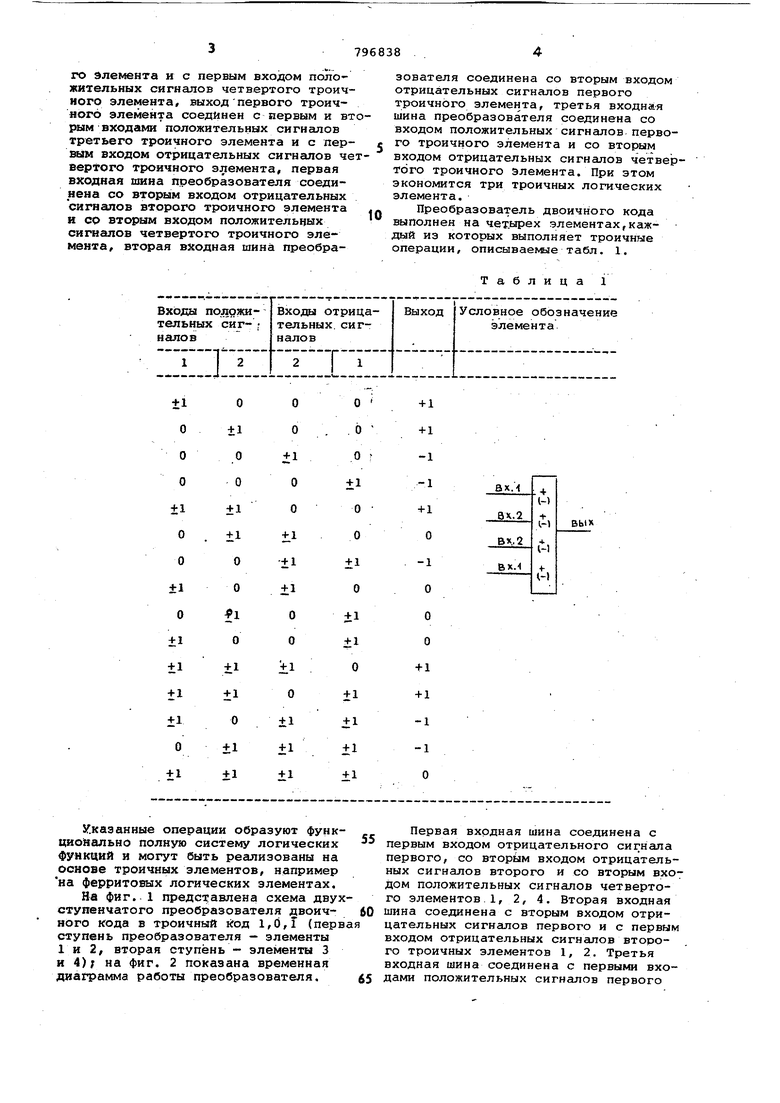

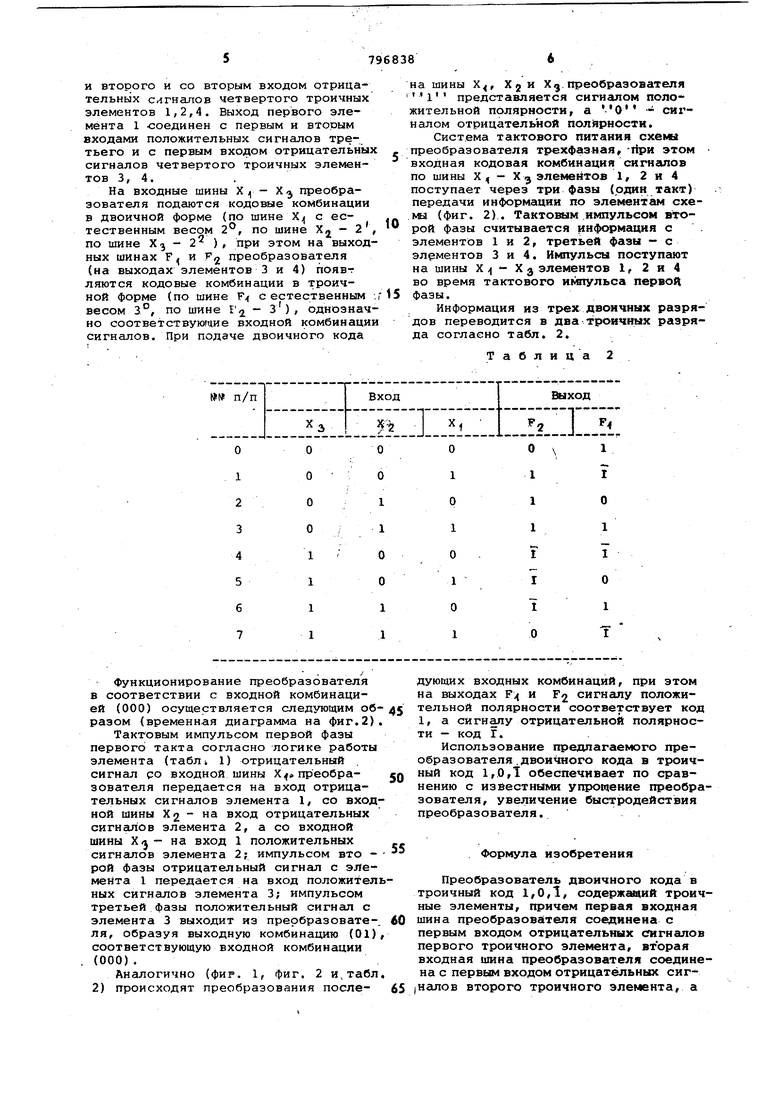

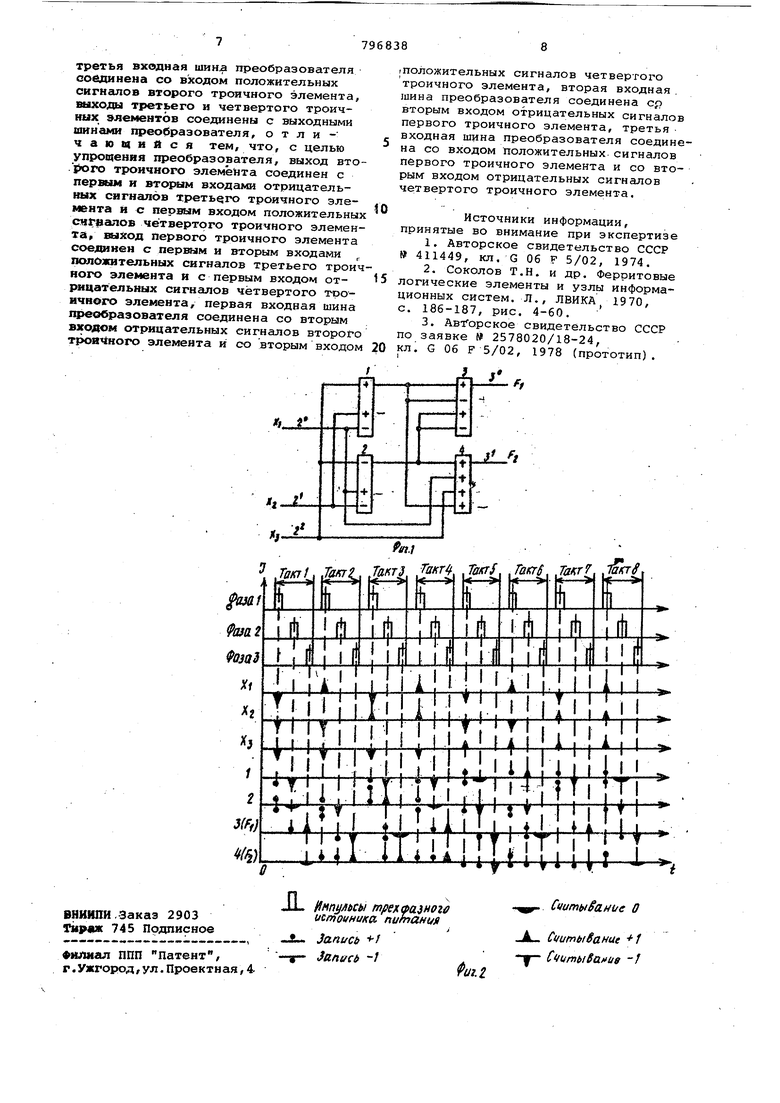

Изобретение относится к вычислительной технике, предназначено для уплотнения информации за счет троичного кодирования чисел и может быть использовано для экономии вхэличества связей между цифровыми блоками вычислительной системы. Преобразователь используется на передающей стороне цифровых блоков. Известен преобразователь двоично го кода в код 1,0, I, содержащий двиочный регистр сдвига с дополнител ным разрядом, дифференцирующую схем и диоды 1J. Однако этот преобразователь имеет низкую надежность и невысокое быстродействие, т.е. преобразование производится последовательно. Известен также преобразователь двоичного кода в троичный код 1,0Д содержгиций десять троичных логическ элементов 2. Однако такой преобразователь име ет сложную реализацию. Наиболее близким к.предлагаемому является преобразователь двоичного кода в троичный код 1,0,1, содержащий троичные элементы, причем перва входная шина преобразователя соединена с первым входом отрицательного сигнала первого троичного элемента, вторая входная шина - с первым входом отрицательного сигнала второго троичного элемента, а третья входная шина - с входом положительного сигнала второго троичного элемента 3. Этот преобразователь имеет сложную реализацию, так как содержит семь троичных логических элементов. Цель изобретения - упрощение преобразователя. Указанная .цель достигается тем, что в преобразователе двоичного кода в троичный код 1,0,Т, содержавши троичные элементы, причем Ьервая входная шина преобразователя соедшнена с первым входом отрицательных.сигналов первого троичного элемента, вторая входная шина преобразователя соединена с первым входом отрицательных сигналов второго троичного элемента, а третья входная шина преобразователя соединена со входом положительных сигналов второго троичного элемента, выходы третьего и четвертого троичных элементов соединены с выходными шинами преобразователя,выход второго троичного элемента соединен с первым и зтотрам входами отри- цательных сигналов третьего троичноГО длемента и с первым входом положительных сигналов четвертого троичного элемента, выход первого троичного элемента соединен с первым и вт рым входами положительных сигналов третьего троичного элемента и с первым входом отрицательных сигналов че вертого троичного элемента, первая входная шина преобразователя соединена со вторым входом отрицательных сигналов второго троичного элемента и со вторым входом положительных сигналов четвертого троичного элемента, вторая входная шина преобра.каэанные операции образуют функционально полную систему логических функций и могут быть реализованы на основе троичных элементов, например на ферритовых логических элементах. На фиг. 1 представлена схема двух ступенчатого преобразователя двоичного кода в троичный кгод 1,0, Г (перв ступень преобразователя - элементы 1 и 2, вторая ступень - элементы 3 и 4); на фиг. 2 показана временная диаграмма работы преобразователя.

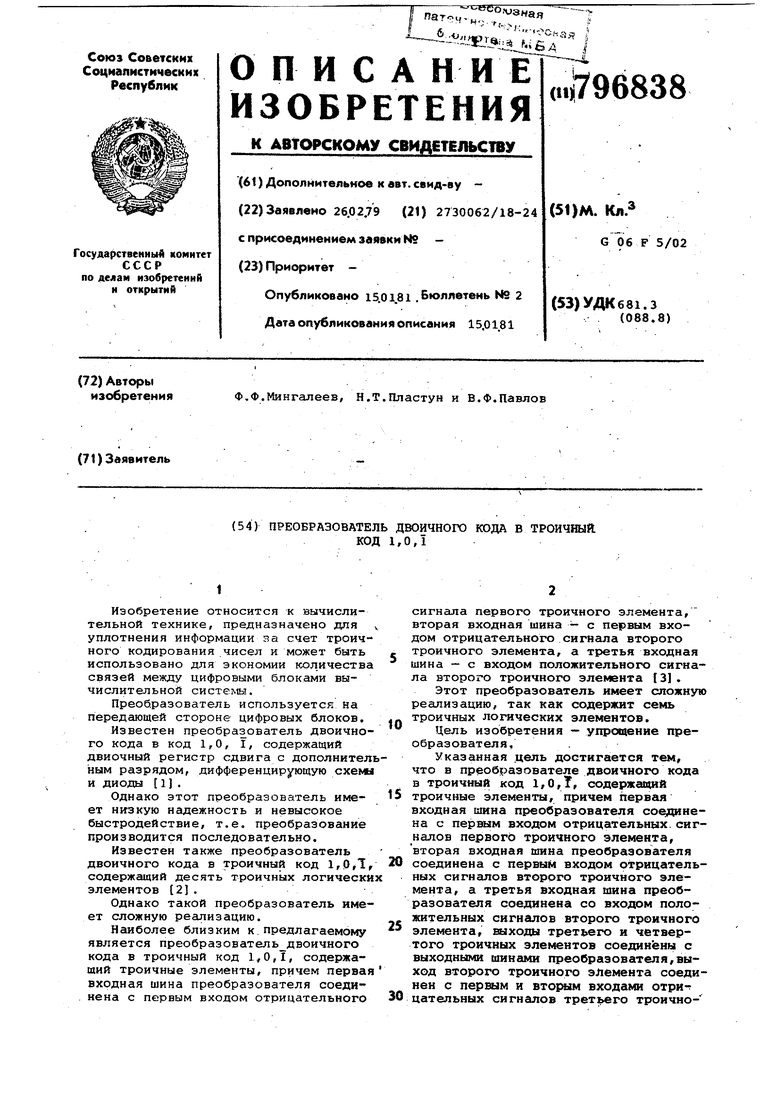

Таблица 1 зователя соединена со вторым входом отрицательных сигнгшов первого троичного элемента, третья входная шина преобразователя соединена со входом положительных сигналов первого троичного элемента и со вторым входом отрицательных сигналов четвертого троичного элемента. При этом экономится три троичных логических элемента. Преобразователь двоичного кода выполнен на четырех элементах,каждый из которых выполняет троичные операции, описываекые табл. 1. Первая входная шина соединена с первым входом отрицательного сигнала первого, со вторым входом отрицательных сигналов второго и со вторым входом положительных сигналов четвертого элементов 1, 2, 4. Вторая входная шина соединена с вторым входом отрицательных сигналов первого и с первым входом отрицательных сигналов второго троичных элементов 1, 2. Третья входная шина соединена с первыми входами положительных сигналов первого

и второго и со вторым входом отрицательных сигналов четвертого троичных элементов 1,2,4. Выход первого элемента 1 соединен с первым и вторым входами положительных сигналов третьего и с первым входом отрицательных сигналов четвертого троичных элементов 3, 4.

На входные шины X ;| - Х преобразователя подаются кодовые комбинации в двоичной форме (по шине Х;| с ес2, по шине Xj, - 2 ,

тественным весом

- 2 ),

по шине X 3 при этом на выходных шинах F и 2 преобразователя

-Р, (на выходах элементов 3 и 4) появт ляются кодовые комбинации в троичной форме (по шине F с естественным . весом 3°, по шине - з) / однозначно соответствующие входной комбинации сигналов. При подаче двоичного кода

О 1 2 3 4 5 б 7

О О О О 1 1 1 1

функционирование преобразователя в соответствии с входной комбинацией (000) осуществляется следующим образом (временная диаграмма на фиг.2).

Тактовым импульсом первой фазы первого такта согласно логике работы элемента (табЛь 1) отрицательный сигнал ро входной шины Х впреобразователя передается на вход отрицательных сигналов элемента 1, со входной шины Х2 - на вход отрицательных сигналов элемента 2, а со входной шины - на вход 1 положительных сигналов элемента 2; импульсом вто - рой фазы отрицательный сигнал с элемента 1 передается на вход положительных сигналов элемента 3; импульсом третьей фазы положительный сигнал с элемента 3 выходит из прербразовате-. ля, образуя выходную комбинацию (01), соответствующую входной комбинации (000) .

Аналогично (фиг. 1, фиг, 2 и,табл. 2) происходят преобразования послена шины Х, Xj и Х. преобразователя 1 представляется сигналом положительной полярности, а - сигналом отрицательной пол 1рности.

Система тактового питания схемы преобразователя т{хехфазная, -йри этом входная кодовая комбинация сигнгшов по шины X., - Х элементов 1, 2 и 4 поступает через три фазы (один такт) передачи информации по элементам схемы (фиг. 2). Тактокам импульсом второй фазы считывается ннформгщня с элементов 1 и 2, третьей фазы - с элементов 3 и 4. Импульсы поступают на шины X ;{ - X 3 элементов 1, 2 и 4 во время тактового нктульса nepBofl фазы.

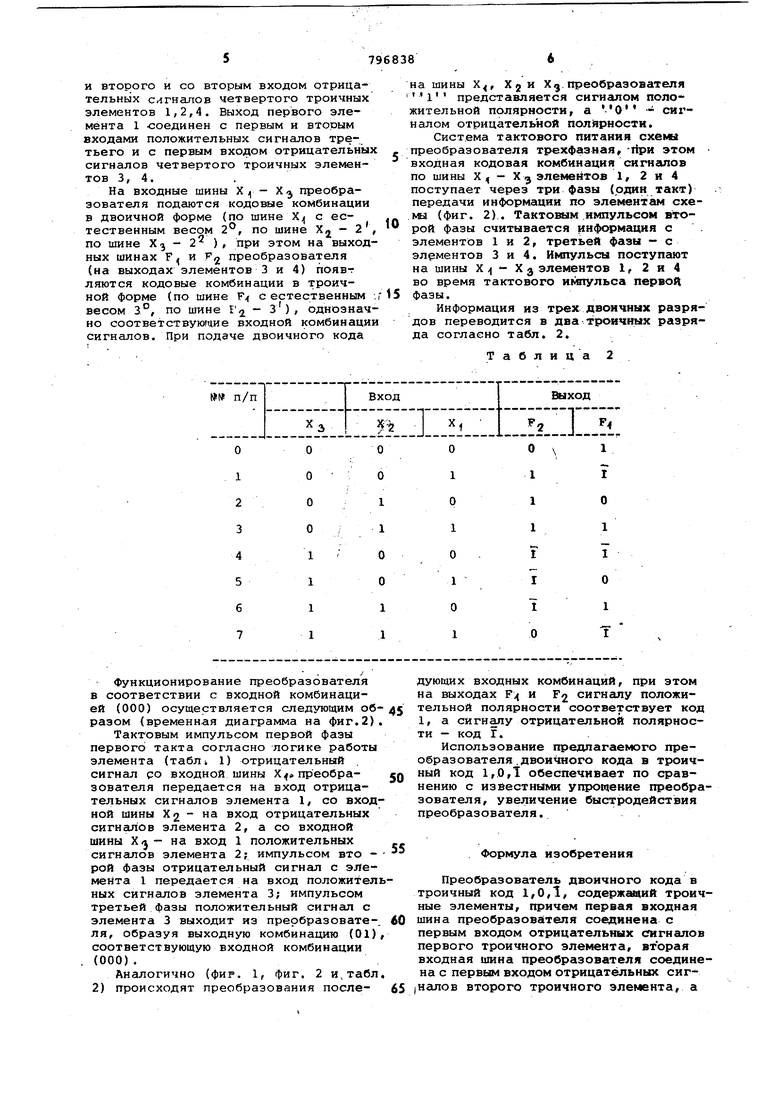

Информация из трех двоичных разрядов переводится в два троичных разряда согласно табл. 2.

Таблица 2

1 1 о 1

о 1 1 1 I 1 о

о 1 о 1 о 1 о 1

о 1

т

дующих входных комбинаций, при этом на выходах Р и F2 сигналу положительной полярности соответствует код 1, а сигнany отрицательной полярности - код Г.

Использование предлагаемого преобразователя .двоичного кода в троичный код 1,0,1 обеспечивает по сравнению с известными упрощение преобразователя, увеличение быстродействия преобразователя.

. Формула изобретения

Преобразователь двоичного кода в троичный код 1,0,1, содержащий троичные элементы, причем первая входная шина преобразователя соединена с первым входом отрицательных сигналов первого троичного элемента, вторая входная шина преобразователя соединена с первым входом отрицательных сиг(Налов второго троичного элемента, а третья входная шинл преобразователя соединена со входом положительных сигналов второго троичного элемента, выходы третьего и четвертого троичных элементов соединены с выходными шинами преобразователя, отличающийся тем, что, с целью упрощения преобразователя, выход вто .рого троичного элемента соединен с первым и BTOcoiM входами отрицательных сигналов третьего троичного элемента и с первым входом положительны сигналов четвертого троичного элемен та, выход Первого троичного элемента соедсинен с первым и вторым входами положительных сигналов третьего трои ного элемента и с первым входом отрицательных сигналов четвертого т роичвого элемента, первая входная шина щ еобразователя соединена со вторым входом отрицательных сигналов второго TpoHtHoro элемента и со вторым входом (Положительных сигналов четвертого троичного элемента, вторая входная . шина преобразователя соединена ср вторым входом отрицательных сигналов первого троичного элемента, третья входная шина преобразователя соединена со входом положительных сигналов первого троичного элемента и со вторым входом отрицательных сигналов четвертого троичного элемента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 411449, кл, G 06 F 5/02, 1974. 2.Соколов Т.Н. и др. Ферритовые логические элементы и узлы информационных систем. Л., ЛВИКА 1970, с. 186-187, рис. 4-60. 3.Авторское свидетельство СССР по заявке № 2578020/18-24, кл. G 06 F 5/02, 1978 (прототип).

Авторы

Даты

1981-01-15—Публикация

1979-02-26—Подача