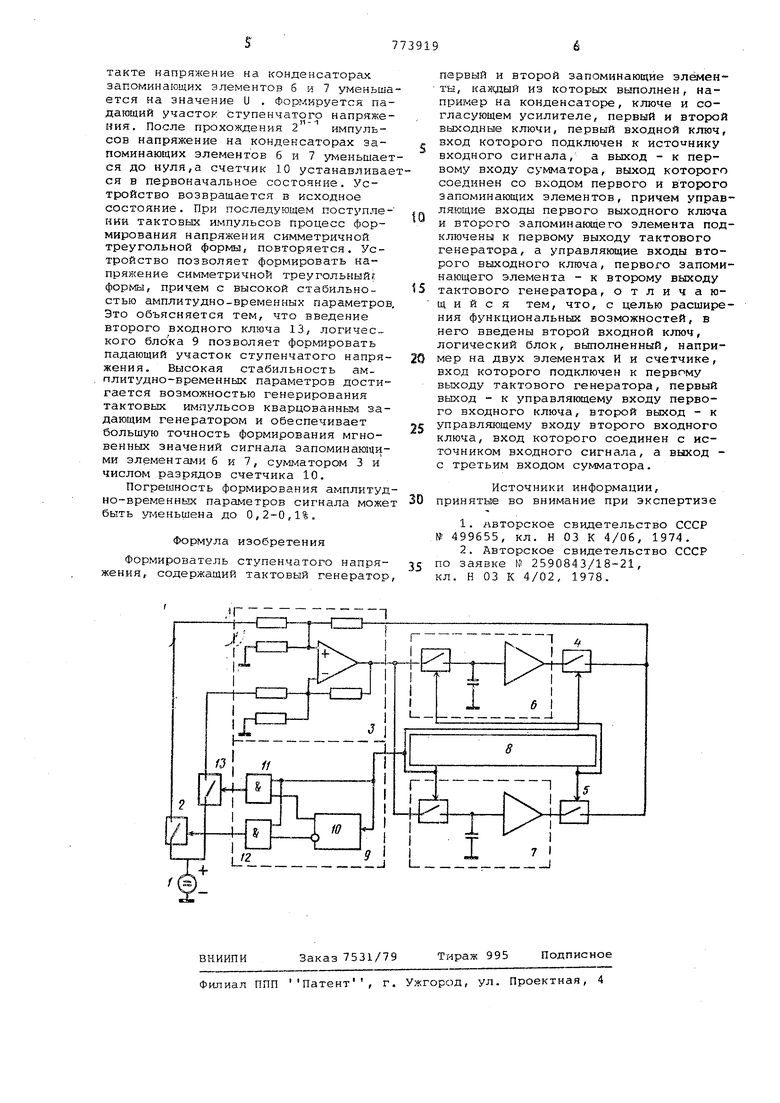

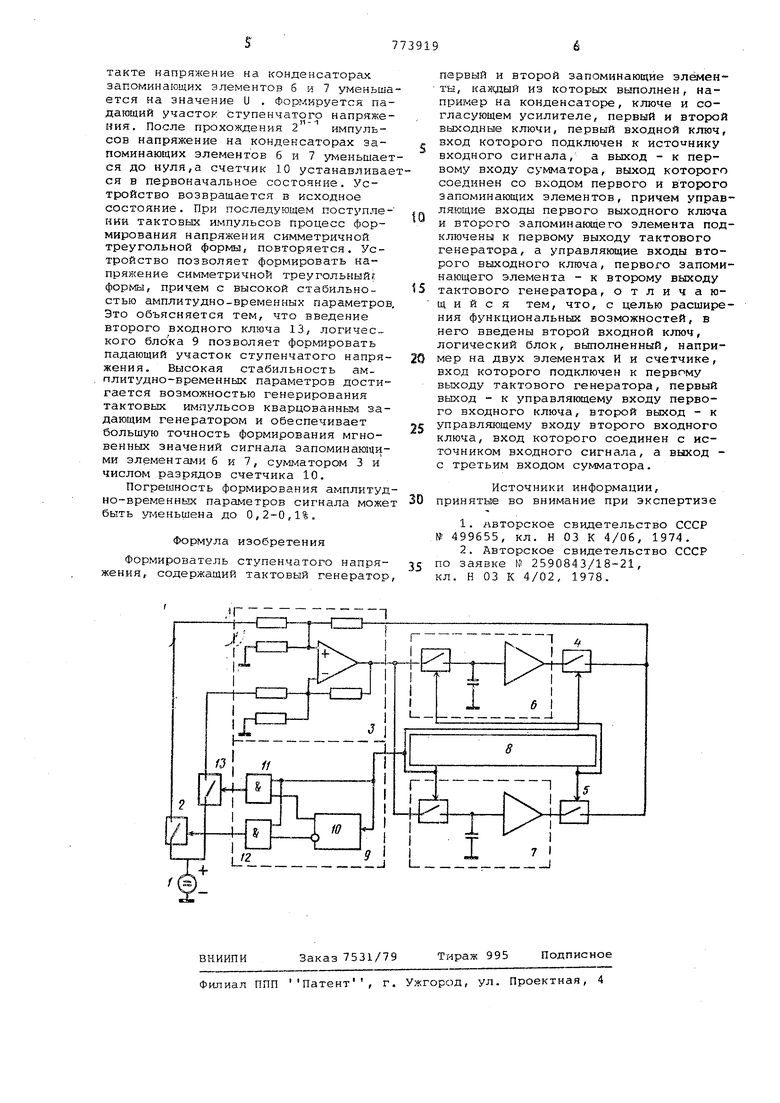

На чертеже изображена структурная схема формирователя ступенчатого на,пряжения. Устройство содержит источник 1 входного сигнала, первый входной ключ 2, сум.штор 3, первый и второй выходные ключи 4 и 5, первый и второй запоминающие элементы 6 и 7,тактовый генератор 8, логический блок 9, состоящий из двоичного счетчика 10, элементов 11 и 12 И, второй входной ключ 13. Вход первого входного ключа 2 подключен к источнику 1 входного сигнала, а его выход - к первому входу сумматора 3, выход которого соединен со входами первого и второго запоминающих элементов б и 7.Упра ляющие входы первого выходного ключа 4 и второго запоминающего элемента 7 подключены к первому выходу тактового генератора 8, а управляющие входы второго выходного ключа 5, первого запоминающего элемента б - ко второму выходу тактового генератора 8. Вход логического блока 9 подключен к первому выходу тактового генератора 8, первый выход - к управляющему входу первого входного ключа 2, второй выход - к управляющему входу вто рого входного ключа 13, вход которого соединен с источником 1 входного сигнала, а выход - с третьим входом сумматора. Логический блок 9- выполнен в виде счетчика 10 и двух элемен тов 11 и 12 И, первые входы которых соединены со входом счетчика 10, а вторые входы - с выходами счетчика 10. Устройство работает следующим образом.. Генератор 8 формирует две последовательности прямоугольных импульсов напряжений, сдвинутых между собой на 180° . Первое напряжение управляет работой первого выходного ключа 4, ключом запоминающего элемен та 7 и логического блока 9, а второе напряжение управляет работой ключа 5 и ключомзапоминающего элемента 6. При логической единице ключи замыкаются, а при логическом нуле - размыкаются. Сумматор 3 по каждому входу .имеет единичные коэффициенты передачи по модулю. Конденсаторы запоминаю щих элементов б и 7 разряжены, счетч 10 обнулен, на одном входе элемента 12 установлена единица с инвертирующего выхода счетчика 10, обеспечиваю щая прохождение тактовых импульсов через элемент 12 И. При поступлении первого управляющего тактового импульса с выхода логического блока 9 замыкаются ключи 2 и 4 и ключ запоми нающего элемента 7. На выходе суьфла тора 3 устанавливается напряжение U, При этом конденсатор запоминающего элемента 7 заряжается через малое выходное сопротивление сумматора 3 до значения напряжения U . Параметры схемы выбраны так, чтобы выполнялись соотношения R. С .. t где R.J - выходное сопротиБление сумматора 3 ; С - емкость каждого конденсатора запоминающих элементов 6 и 7 RO. - входное сопротивление согласующего усилителя (Запоминающих элементов б и 7 длительность управляющего тактового импульса. При выполнении условия первого неравенства 6 течение первого полупериода первого управляющего тактового импульса напряжение на выходе запоминающего элемента 7 остается неизменным и равньлм и . В течение второго полупериода первого управляющего тактового импульса ключ 5 и ключ запоминающего элемента 6 замчкается, а ключи 2 и 4, ключ запоминающего элемента 7 размыкаются. Согласно второг/гу неравенству, напряжение на выходе запоминакЕцего элемента в течение времени второго полупериода первого управляющего тактового импульса будет постоянным и равное U . Через ключ 5 оно поступает на второй вход сум латора 3 и при этом конденсатор запоминающего элемента б заряжается до напряжения и . Далее, после поступления второго управлякйщего тактового импульса, в течение его первого полупериода в замкнутом состоянии находятся ключи 2 и 4, ключ запоминающего элемента 7, а ключ 5, запоминающего элемента б в разомкнутом состоянии. При этом на выходе сумг атора устанавливается напряжение , равное 2 U, так как на первый и второй входы сумматора поступают напряжения равные U. Затем, в течение второго полупериода второго управляющего импульса ключи 2 и 4,ключ запоминающего элемента 7 разомкнуты, а ключ 5, запоминающего элемента б замкнут и при этом на второй вход сумматора, через ключ 5 поступает напряжение 2 и. В результате на выходах запоминащих элементов б и 7 формируются нарастающие ступенчатые напряжения сдвинутые на время 2С. После поступления на вход логического блока 92 импульсов (количество разрядов счетчика 10) на выходе последнего разряда счетчика 10 появляется уровень логической единицы, которым открывается элемент 11 И,.при этом элемент 12 И закрывается. Начиная с этого момента у,правляющие тактовые импульсы поступают на управляющий вход второго входного ключа 13, а на управляющий вход первого входного ключа поступает уровень логического нуля. Выход ключа 13 соединен с инвертирующим третьим входом сумматора 3. Вследствие этого, при каждом

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь треугольного напряжения | 1986 |

|

SU1370740A1 |

| Генератор трапецеидального сигнала | 1987 |

|

SU1432744A1 |

| Формирователь сигналов специальной формы | 1988 |

|

SU1550604A1 |

| Пороговое устройство | 1983 |

|

SU1151922A1 |

| Формирователь ступенчатого напряжения | 1987 |

|

SU1573533A2 |

| Формирователь ступенчатого напряжения | 1982 |

|

SU1075384A2 |

| Формирователь ступенчатого напряжения | 1986 |

|

SU1370738A2 |

| Формирователь ступенчатого напряжения | 1978 |

|

SU705654A1 |

| Формирователь ступенчатого напряжения | 1985 |

|

SU1249694A1 |

| Формирователь ступенчатого напряжения | 1982 |

|

SU1058036A2 |

Авторы

Даты

1980-10-23—Публикация

1979-04-17—Подача