, подключены к соответствующим выходам элементов И, а третий и четвертый выходы логического блока - к соответстиующим выходам элементов ИЛИ.

3. Устройство по п. 1, отличающееся тем, что блок сигнализации выполнен в виде одновибратора, выходом соединенного с базой транзистора, коллектор которого через светоизлучающий элемент подключен к шине пита.ния, а эмиттер - к шине нулевого потенциала, вход одновибратора является входом блока сигнализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор трапецеидального сигнала | 1987 |

|

SU1432744A1 |

| Генератор трапецеидального сигнала | 1986 |

|

SU1324093A1 |

| Формирователь сигналов специальной формы | 1988 |

|

SU1550604A1 |

| Формирователь треугольного напряжения | 1986 |

|

SU1370740A1 |

| Формирователь ступенчатого напряжения | 1982 |

|

SU1058036A2 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Преобразователь напряжения в интервал времени | 1984 |

|

SU1282331A1 |

| Формирователь ступенчатого напряжения | 1987 |

|

SU1573533A2 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

1, ПОРОГОВОЕ УСТРОЙСТВО, содержащее первую и вторую RC-цепи, входы которых подключены к источнику входного напряжения, а к каждому из выходов параллельно подключены соответственно первый и второй дополнительные ключи, входной ключ, основной сумматор, основной запоминающий и дополнительный запоминающий элементы, первый и второй выходные ключи, входы которых соединены соответственно с выходами основного запоминающего и дополнительного запоминающего элементов, выходы подключены к первому входу основного сумматора, второй вход которого через входной ключ соединен с источником входного напряжения, а выход основного сумматора соединен с входами основного запоминающего и дополнительного запоминающего элементов, дополнительный сумматор, первый вход которого соединен с выходом первой RC-цепи, второй вход - с выходом второй RC-цепи, третий вход - с выходом основного запоминающего элемента, четвертый вход - с выходом дополнительного запоминающего эле.мента, а также тактовый генератор, первый выход которого соединен с управляющими входами входного и первого выходного ключей, второй выход - с управляющим входом второго выходного ключа, отличающееся тем, что, с целью расщирения функциона. возможностей устройства путем обеспечения контроля частоты импульсов, в него введены делитель напряжения, блок сигнализации, ограничивающие резисторы, логический блок, компаратор и два ключа, каждый из которых подключен параллельно конденсатору основного запоминающего и дополнительного запоминающего элементов соответственно, управляющие входы этих к.пючей объединены и соединены с управляющим входом тактового генератора и с входной шиной, которая подключена к первому входу логического блока, второй и третий входы которого подключены соответственно к первому и второму выходам тактового генератора, первый выход .логического блока соединен с управляющим входом основного запоминающего элемента, второй выход - i с управляющим входом дополнительного запоминающего элемента, третий выход - с (Л управляющим входом второго дополнительного ключа, четвертый выход - с управляющим входом первого дополнительного ключа, делитель напряжения входом подключен к источнику входного напряжения, а выходом через первый ограничивающий резистор - к первому входу ко.мпаратора, второй вход которого подсоединен через второй сд ограничивающий резистор к выходу дополнительного сумматора, а выход компаратосо ю гчэ ра соединен с входом блока сигнализации. 2. Устройство по п. 1, отличающееся тем, что логический блок выполнен на двух элементах ИЛИ, двух элемнтах И и двух инверторах, входы которых объединены и являются первым входом логического блока, который соединен с первыми входами элементов ИЛИ, вторые входы которых подключены соответственно к первым входам элементов И, вторые входы которых соединены с соответствующими выходами инверторов, причем второй и третий входы логического блока подключены к соответствующим вторым входам элементов ИЛИ, первый и второй выходы логического

Изобретение относится к импульсной технике и может быть использовано для контроля частоты следования электрических импульсов. Известно пороговое устройство, содержащее последовательно соединенные релаксационный RC-генератор и пиковый детектор, к выходу которого подключена обмотка исполнительного реле, а также тиристор, подключенный параллельно входу релаксационного RC-генератора 1. Однако данное устройство имеет большую погрешность при контроле частоты следования импульсов из-за нестабильности параметров схемы, обусловленной временной нестабильностью емкости конденсаторов, входящих в состав генератора и пикового детектора. Наиболее близким по технической сущности к изобретению является пороговое устройство, содержащее входной ключ, вход которого соединен с источником входного напряжения, запоминающий элемент и тактовый генератор, первый и второй выходы которого соединены соответственно с управляющими входами запоминающего элемента и входного ключа, сумматор, дополнительный запоминающий элемент, первый и второй выходные ключи, входы которых соединены соответствено с выходами запоминающего элемента, выходы подключены к первому входу сумматора, второй вход которого соединен с выходом входного ключа, а выход сумматора соединен с входом запоминающего элемента и дополнительного запоминающего элемента, причем управляющие входы первого и второго выходных ключей и дополнительного запоминающего элемента подключены соответственно к третьему, четвертому и пятому выходам тактового генератора, и два дополнительных ключа, допатнительный сумматор, первая и вторая RC-цепи, входы которых подключены к вы.ходу источника входного напряжения, и к каждому из входов параллельно подключены соответственно первый и второй дополнительные ключи, управляющий вход первого из которых соединен с первым выходом тактового генератора, управляющий вход второго дополнительного ключа соединен с пятым выходом тактового генератора, соединен с выходом первой RC-цепи, третий вход - с выходом запоминающего элемента, четвертый вход - с выходом дополнительного запоминающего элемента 2. Однако известное устройство не обеспечивает контроль частоты импульсной последовательности, что ограничивает функциональные возможности и область использования устройства. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения контроля частоты импульсов переменного тока. Поставленная цель достигается тем, что в пороговое устройство, содержащее первую и вторую RC-цепи, входы которых подключены к источнику входного напряжения, а к каждому из выходов параллельно подключены соответственно первый и второй дополнительные ключи, входной ключ, основной сумматор, основной запоминающий и дополнительный запоминающий элементы, первый и второй выходные ключи, входы которых соединены соответственно с выходами основного запоминающего и дополнительного запоминающего элементов, выходы подключены к первому входу основного сумматора, второй вход которого через входной ключ соединен с источником входного напряжения, а выход основного сумматора соединен с входами основного запоминающего и дополнительного запоминающего элементов, дополнительный сумматор, первый вход которого соединен с выходом первой RC-цепи, второй вход - с выходом второй RC-цепи, третий вход - с выходом основного запоминающего элемента, четвертый вход - с выходом дополнительного запоминающего элемента, а также тактовый генератор, первый выход которого соединен с управляющими входами входного и первого выходного ключей, второй выход - с управляющим входом второго выходного ключа, дополнительно введены делитель напряжения, блок сигнализации, ограничивающие резисторы, логический блок, компаратор и

два ключа, каждый из которых подключен параллельно конденсатору основного запоминающего и дополнительного запоминающего элементов соответственно, управляющие входы этих ключей объединены и соединены с управляющим входом тактового генератора и с входной шиной, которая подключена к первому входу логического блока, второй и третий входы которого подключены соответственно к первому и второму выходам тактового генератора, первый выход логического блока соединен с управляющим входом основного запоминающего элемента, второй выход - с управляющим входом дополнительного запоминающего элемента, третий выход - с управляющим входом второго дополнительного ключа, четвертый выход - с управляющим входом первого дополнительного ключа, делитель напряжения входом подключен к источнику входного напряжения, а выходом через первый ограничивающий резистор - к первому входу компаратора, второй вход которого подключен через второй ограничивающий резистор к выходу дополнительного сумматора, а выход компаратора соединен с входом блока сигнализации.

При этом логический блок выполнен на двух элементах ИЛИ, двух элементах И и двух инверторах, входы которых объединены и являются первым входом логического блока, который соединен с первыми входами элементов ИЛИ, вторые входы которых подключены соответственно к первым входам элементов И, вторые входы которых соединены с соответствующими выходами инверторов, причем второй и третий входы логического блока подключены к соответствующим вторым входам элементов ИЛИ, первый и второй выходы логического блока подключены к соответствующим выходам элементов И, третий и четвертый выходы логического блока - к соответствующим выходам элементов ИЛИ.

Причем блок сигнализации выполнен в виде одновибратора, выходом соединенного с базой транзистора, коллектор которого через светоизлучающий элемент подключен к щине питания, а эмиттер - к щине нулевого потенциала, вход одновибратора является входом блока сигнализации.

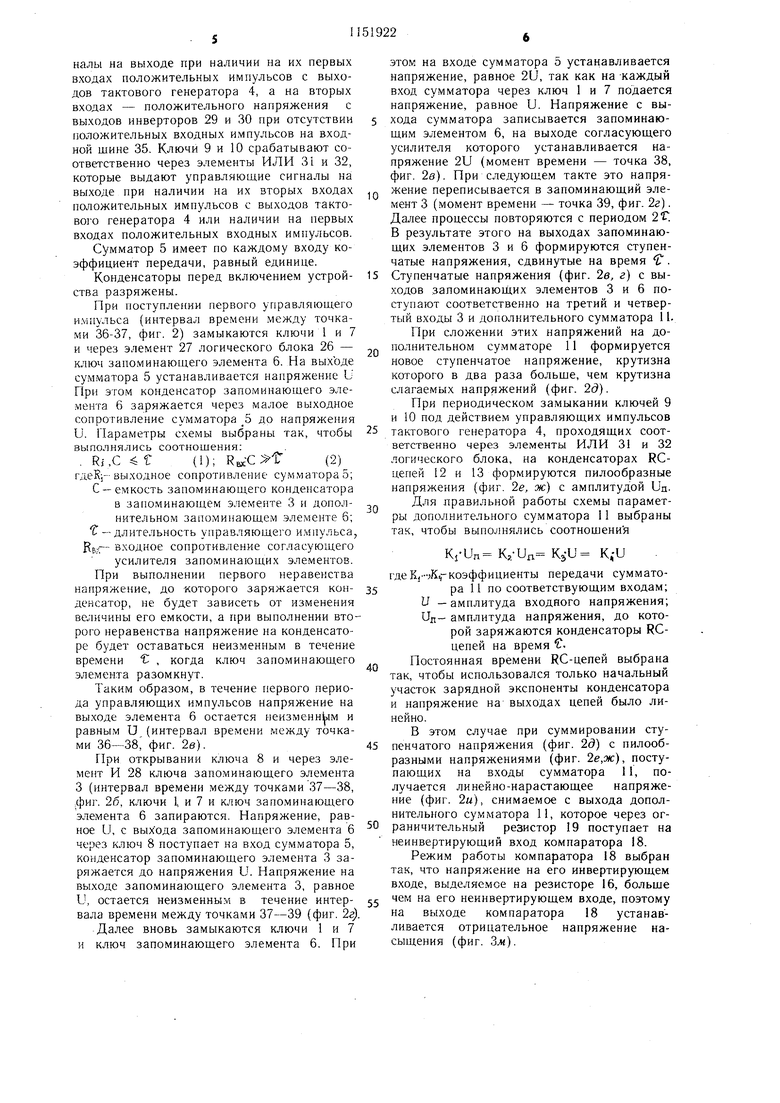

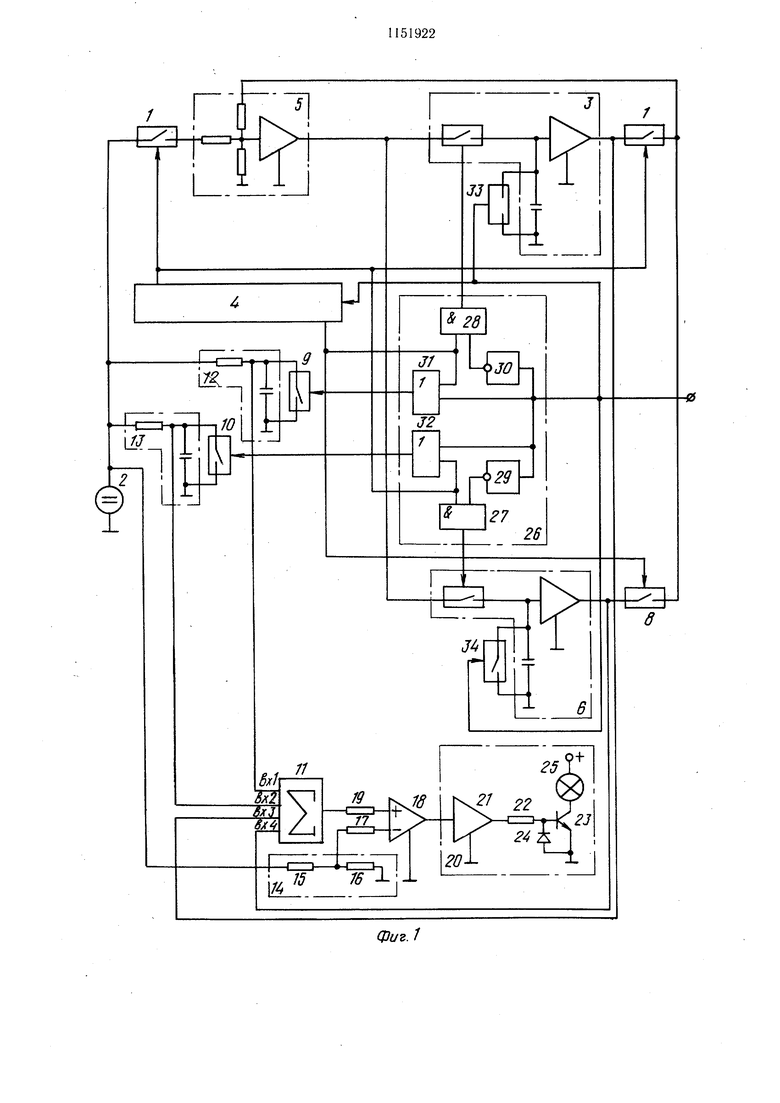

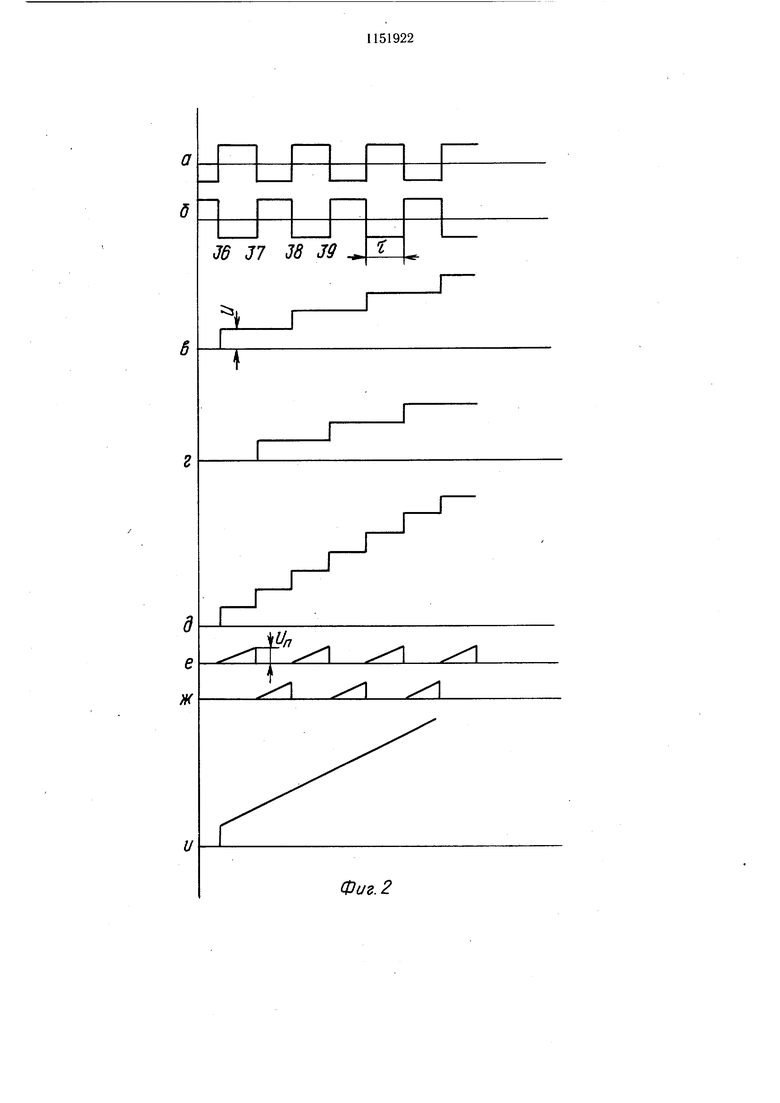

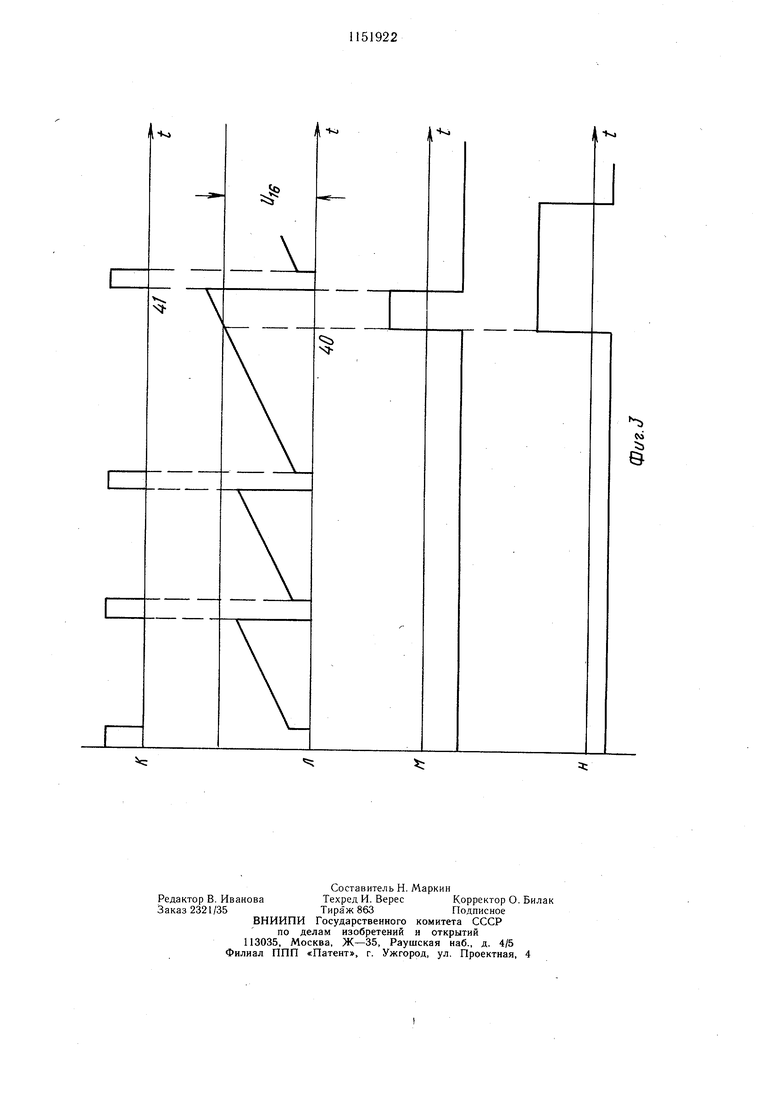

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 и 3 - эпюры, поясняющие его работу.

Пороговое устройство содержит входной ключ 1, вход которого соединен с источником 2 входного напряжения, запоминающий элемент 3 и тактовый генератор 4, первый выход которого соединен с управляющим входом, входного ключа 1, сумматор 5, дополнительный запоминающий элемент 6, первый и второй выходные ключи 7 и 8, входы которых

соединены соответственно с выходами запоминающих элементов 3 и 6, выходы подключены к первому входу сумматора 5, второй вход которого соединен с выходом входного 5 ключа 1, а выход сумматора 5 соединен с входом запоминающего и дополнительного запоминающего элементов 3 и 6, причем управляющие входы первого и второго выходных ключей 7 и 8 подключены соответственно к первому и второму выходам тактового генератора 4, два дополнительных ключа 9 и 10, дополнительный сумматор 11, первую и вторую RC-цепи 12 и 13, входы которых подключены к выходу источника 2 входного напряжения, а к каждому из выходов параллельно подключены соответственно первый и второй дополнительные ключи 9 и 10, делитель 14 напряжения, состоящий из резисторов 15 и 16, входом подключен к источнику 2 входного напряжения, а выходом через ограничивающий резистор 17 - к первому входу компаратора 18, второй вход которого через ограничивающий резистор 19 подключен к выходу дополнительного сумматора 11, блок 20 сигнализации, состоящий из одновибратора 21 (выполненного,

5 например, на базе операционного усилителя) , резистора 22, ключа 23, диода 24 и индикатора 25, входом подключен к выходу компаратора, логический блок 26, состоящий из двух элементов И 27 и 28, двух инверторов 29 и 30 и двух элементов ИЛИ 31 и 32, первым входом подключен к управляющим входам ключей 33 и 34 и к входной шине 35, второй и третий входы логического блока 26 подключены соответственно к первому и второму выходам тактового генератора 4, первый выход логического блока 26 подключен к управляющему входу ключа запоминающего элемента 3, второй выход - к управляющему входу ключа дополнительного эле.мента 6, третий выход - к управляющему входу второго дополнительного ключа

10, четвертый выход - к управляющему входу первого дополнительного ключа 9.

Устройство работает следующим образом.

5 Тактовый генератор 4 формирует два импульсных напряжения, сдвинутых на 180° (фиг. 2а, б).

Первое напряжение управляет работой ключей 1 и 7 и через логический блок 26 ключа дополнительного запоминающего элемента 6 и ключа 10 (фиг. 2а), второе напряжение управляет работой ключа 8 и через логический блок 26 ключа запоминающего элемента 3 и ключа 9 (фиг. 26). При положительном импульсе ключи замыкаются, а

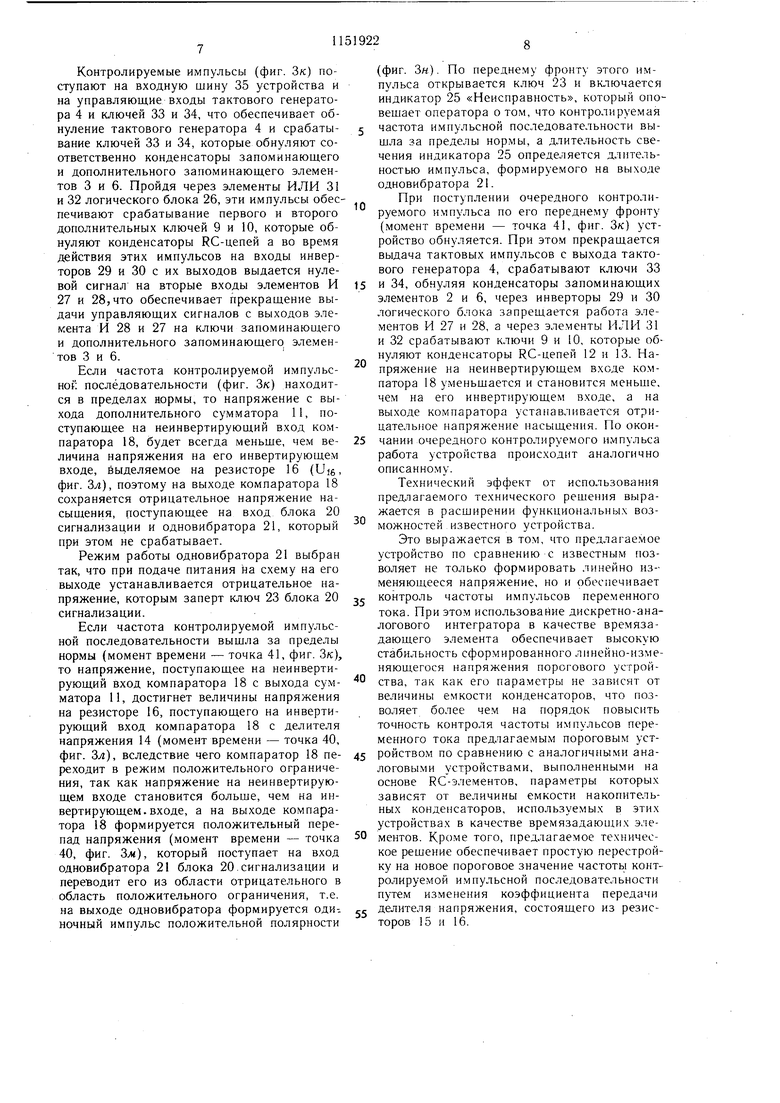

5 при отрицательном размыкаются. При этом ключи запоминающих элементов 6 и 3 срабатывают соответственно через элементы И 27 и 28, которые выдают управляющие сигналы на выходе при наличии на их первых входах положительных импульсов с выходов тактового генератора 4, а на вторых входах - положительного напряжения с выходов инверторов 29 и 30 при отсутствии положительных входных импульсов на входной шине 35. Ключи 9 и 10 срабатывают соответственно через элементы ИЛИ 31 и 32, которые выдают управляющие сигналы на выходе при наличии на их вторых входах положительных импульсов с выходов тактового генератора 4 или наличии на первых входах положительных входных импульсов. Сумматор 5 имеет по каждому входу коэффициент передачи, равный единице. Конденсаторы перед включением устройства разряжены. При поступлении первого управляющего импульса (интервал времени между точками 36-37, фиг. 2) замыкаются ключи 1 и 7 и через элемент 27 логического блока 26 - ключ запоминающего элемента 6. На выходе су.мматора 5 устанавливается напряжение L При этом конденсатор запоминающего элемента 6 заряжается через малое выходное сопротивление сумматора 5 до напряжения и. Параметры схемы выбраны так, чтобы выполнялись соотношения; . Rj,C « f(1); Rbx-Ot(2) гдеК;- выходное сопротивление сумматора 5; С -емкость запоминающего конденсатора 8 запоминающем элементе 3 и дополнительном запоминающем элементе 6; t -длительность управляющего импульса, КкуГ входное сопротивление согласующего усилителя запоминающих элементов. При выполнении первого неравенства напряжение, до которого заряжается конденсатор, не будет зависеть от изменения величины его емкости, а при выполнении второго неравенства напряжение на конденсаторе будет оставаться неизменным в течение времени С , когда ключ запоминающего элемента разомкнут. Таким образом, в течение первого периода управляющих импульсов напряжение на выходе элемента 6 остается неизменном и равным и (интервал времени между точками 36-38 фиг. 20). При открывании ключа 8 и через элемент И 28 ключа запоминающего элемента 3 (интервал времени между точками 37-38, .фиг. 26, ключи 1, и 7 и ключ запоминающего элемента 6 запираются. Напряжение, равное и, с выхода запоминающего элемента 6 через ключ 8 поступает на вход сумматора 5, конденсатор запоминающего элемента 3 заряжается до напряжения U. Напряжение на выходе запоминающего элемента 3, равное и, остается неизменным в течение интервала времени между точками 37-39 (фиг. 2г). Далее вновь замыкаются ключи 1 и 7 и ключ запоминающего элемента 6. При этом на входе сумматора 5 устанавливается напряжение, равное 2U, так как на -каждый вход сумматора через ключ 1 и 7 подается напряжение, равное U. Напряжение с выхода сумматора записывается запоминающим элементом 6, на выходе согласующего усилителя которого устанавливается напряжение 2U (момент времени - точка 38, фиг. 2в). При следующем такте это напряжение переписывается в запоминающий элемент 3 (момент времени - точка 39, фиг. 2г). Далее процессы повторяются с периодом 2 Т. В результате этого на выходах запоминающих элементов 3 и 6 формируются ступенчатые напряжения, сдвинутые на время Г. Ступенчатые напряжения (фиг. 2в, г) с выходов запоминающих элементов 3 и 6 поступают соответственно на третий и четвертый входы 3 и дополнительного сумматора 11. При сложении этих напряжений на дополнительном сумматоре 11 формируется новое ступенчатое напряжение, крутизна которого в два раза больще, чем крутизна слагаемых напряжений (фиг. 2д}. При периодическом замыкании ключей 9 и 10 под действием управляющих импульсов тактового генератора 4, проходящих соответственно через элементы ИЛИ 31 и 32 логического блока, на конденсаторах RCцепей 12 и 13 формируются пилообразные напряжения (фиг. 2е, ж) с амплитудой Уд. Для правильной работы схемы параметры дополнительного сумматора 11 выбраны так, чтобы выполнялись соотнощения Ki-Un Кзи к,-и где Kj-;K,,-коэффициенты передачи сумматора 11 по соответствующим входам; и -амплитуда входного напряжения; Од- амплитуда напряжения, до которой заряжаются конденсаторы RCцепей на время €. Постоянная времени RC-цепей выбрана так, чтобы использовался только начальный участок зарядной экспоненты конденсатора и напряжение на выходах цепей было линейно. В этом случае при суммировании ступенчатого напряжения (фиг. 2д) с пилообразными напряжениями (фиг. 2е,ж), поступающих на входы сумматора 11, получается линейно-нарастающее напряжение (фиг. 2и), снимаемое с выхода дополнительного сумматора 11, которое через ограничительный резистор 19 поступает на неинвертирующий вход компаратора 18. Режим работы компаратора 18 выбран так, что напряжение на его инвертирующем входе, выделяемое на резисторе 16, больще чем на его неинвертирующем входе, поэтому на выходе компаратора 18 устанавливается отрицательное напряжение насыщения (фиг. 3м).

Контролируемые импульсы (фиг. Зк) поступают на входную шину 35 устройства и на управляющие входы тактового генератора 4 и ключей 33 и 34, что обеспечивает обнуление тактового генератора 4 и срабатывание ключей 33 и 34, которые обнуляют соответственно конденсаторы запоминающего и дополнительного запоминающего элементов 3 и 6. Пройдя через элементы ИЛИ 31 и 32 логического блока 26, эти импульсы обеспечивают срабатывание первого и второго дополнительных ключей 9 и 10, которые обнуляют конденсаторы RC-цепей а во время действия этих импульсов на входы инверторов 29 и 30 с их выходов выдается нулевой сигнал на вторые входы элементов И 27 и 28,что обеспечивает прекращение выдачи управляющих сигналов с выходов элемента И 28 и 27 на ключи запоминающего и дополнительного запоминающего элементов 3 и 6.

Если частота контролируемой импульсHof: последовательности (фиг. Зк) находится в пределах нормы, то напряжение с выхода дополнительного сумматора 11, поступающее на неинвертирующий вход компаратора 18, будет всегда меньше, чем величина напряжения на его инвертирующем входе, выделяемое на резисторе 16 (Ujg, фиг. 3л), поэтому на выходе компаратора 18 сохраняется отрицательное напряжение насыщения, поступающее на вход блока 20 сигнализации и одновибратора 21, который при этом не срабатывает.

Режим работы одновибратора 21 выбран так, что при подаче питания йа схему на его выходе устанавливается отрицательное напряжение, которым заперт ключ 23 блока 20 сигнализации.

Если частота контролируемой импульсной последовательности вышла за пределы нормы (момент времени - точка 41, фиг. Зк), то напряжение, поступающее на неинвертирующий вход компаратора 18 с выхода сумматора 11, достигнет величины напряжения на резисторе 16, поступающего на инвертирующий вход компаратора 18 с делителя напряжения 14 (момент времени - точка 40, фиг. 3л), вследствие чего компаратор 18 переходит в режим положительного ограничения, так как напряжение на неинвертирующем входе становится больше, чем на инвертирующем, входе, а на выходе компаратора 18 формируется положительный перепад напряжения (момент времени - точка 40, фиг. 3л), который поступает на вход одновибратора 21 блока 20.сигнализации и переводит его из области отрицательного в область положительного ограничения, т.е. на выходе одновибратора формируется оди-. ночный импульс положительной полярности

(фиг. Зн). По переднему фронту этого импульса открывается ключ 23 и включается индикатор 25 «Неисправность, который оповешает оператора о том, что контролируемая 5 частота импульсной последовательности вышла за пределы нормы, а длительность свечения индикатора 25 определяется длительностью импульса, формируемого на выходе одновибратора 21.

При поступлении очередного контролируемого импульса по его переднему фронту (момент времени - точка 41, фиг. Зк) устройство обнуляется. При этом прекращается выдача тактовых импульсов с выхода тактового генератора 4, срабатывают ключи 33

5 и 34, обнуляя конденсаторы запоминающих элементов 2 и 6, через инверторы 29 и 30 логического блока запрещается работа элементов И 27 и 28, а через элементы ИЛИ 31 и 32 срабатывают ключи 9 и 10, которые обнуляют конденсаторы RC-цепей 12 и 13. Напряжение на неинвертирующем входе компатора 18 уменьшается и становится меньше, чем на его инвертирующем входе, а на выходе компаратора устанавливается отрицательное напряжение насыщения. По окончании очередного контролируемого импульса работа устройства происходит аналогично описанному.

Технический эффект от использования предлагаемого технического решения выражается в расширении функциональных возможностей известного устройства.

Это выражается в том, что предлагаемое устройство по сравнению с известным позволяет не только формировать линейно изменяющееся напряжение, но и обеспечивает

J контроль частоты импульсов переменного тока. При этом использование дискретно-аналогового интегратора в качестве времязадающего элемента обеспечивает высокую стабильность сформированного линейно-изменяющегося напряжения порогового устройства, так как его параметры не зависят от величины емкости конденсаторов, что позволяет более чем на порядок повысить точность контроля частоты импульсов переменного тока предлагаемым пороговым устройством по сравнению с аналогичными аналоговыми устройствами, выполненными на основе RC-элементов, параметры которых зависят от величины емкости накопительных конденсаторов, используемых в этих устройствах в качестве времязадающи.х эле0 ментов. Кроме того, предлагаемое техническое решение обеспечивает простую перестройку на новое пороговое значение частоты контролируемой импульсной последовательности путем изменения коэффициента передачи

5 делителя напряжения, состоящего из резисторов 15 и 16.

J6 J7 38 J9

lJr

П

.x

.1.

Фиг. 2

к

So

s

«

Xh

Cvi

:ь

В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пороговое устройство | 1973 |

|

SU457967A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3492141/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-24—Подача