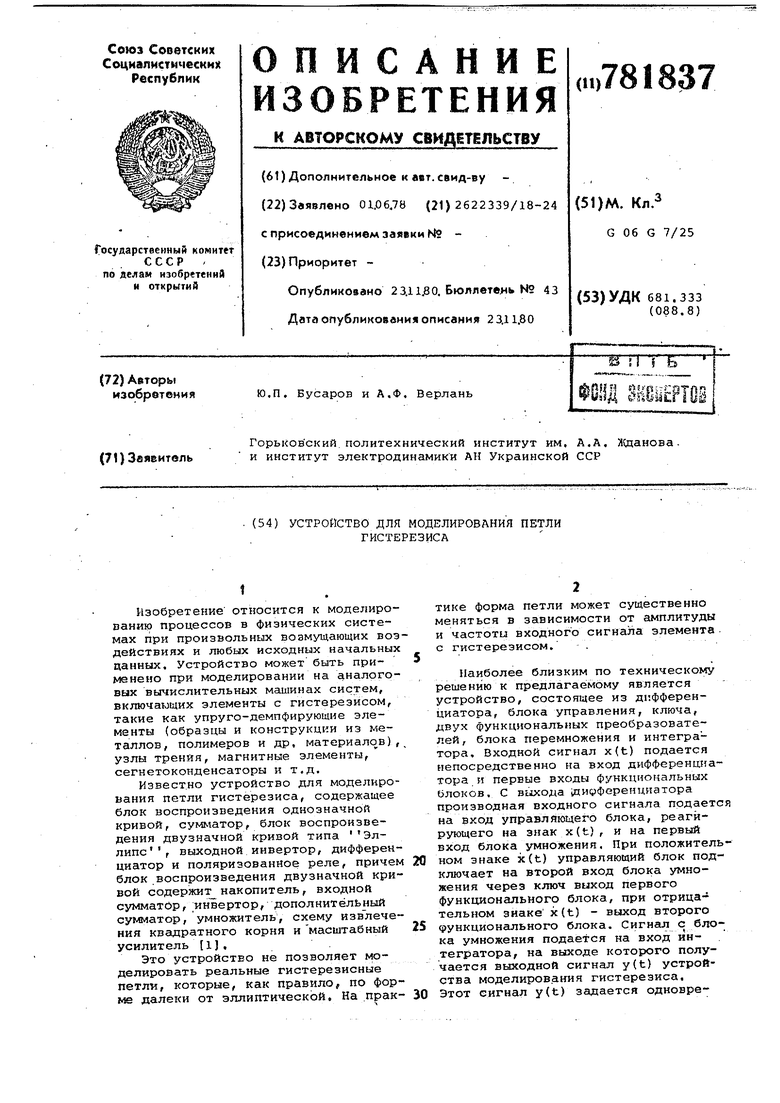

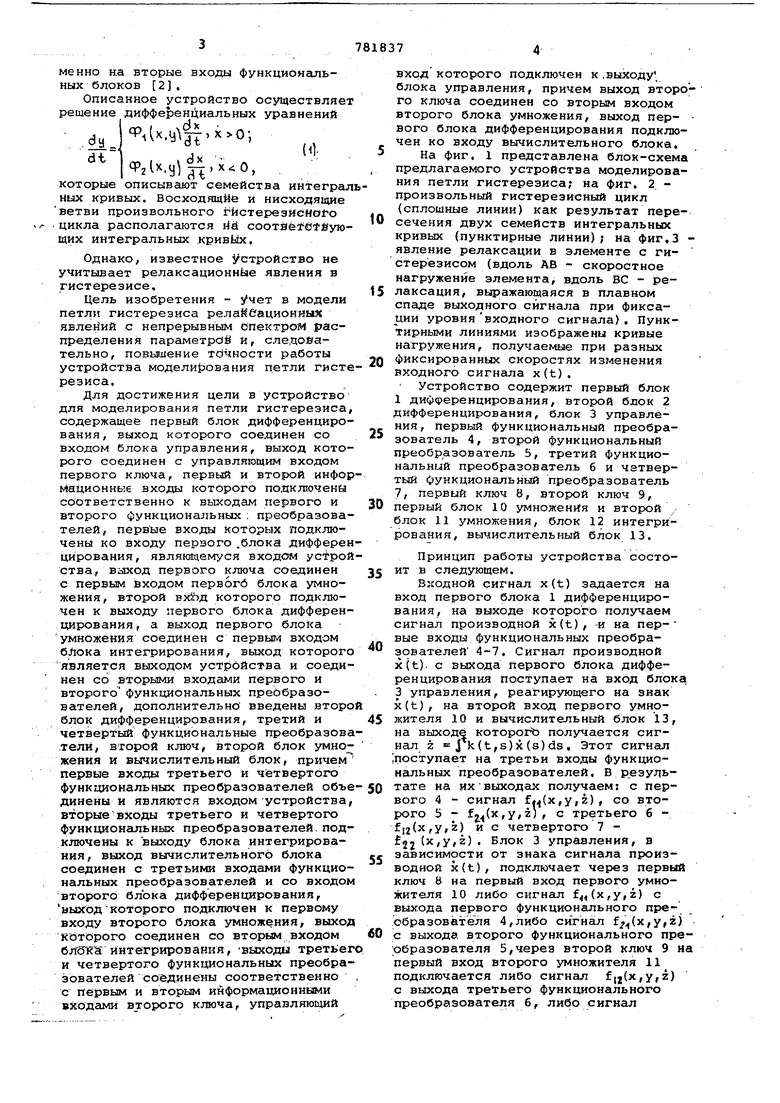

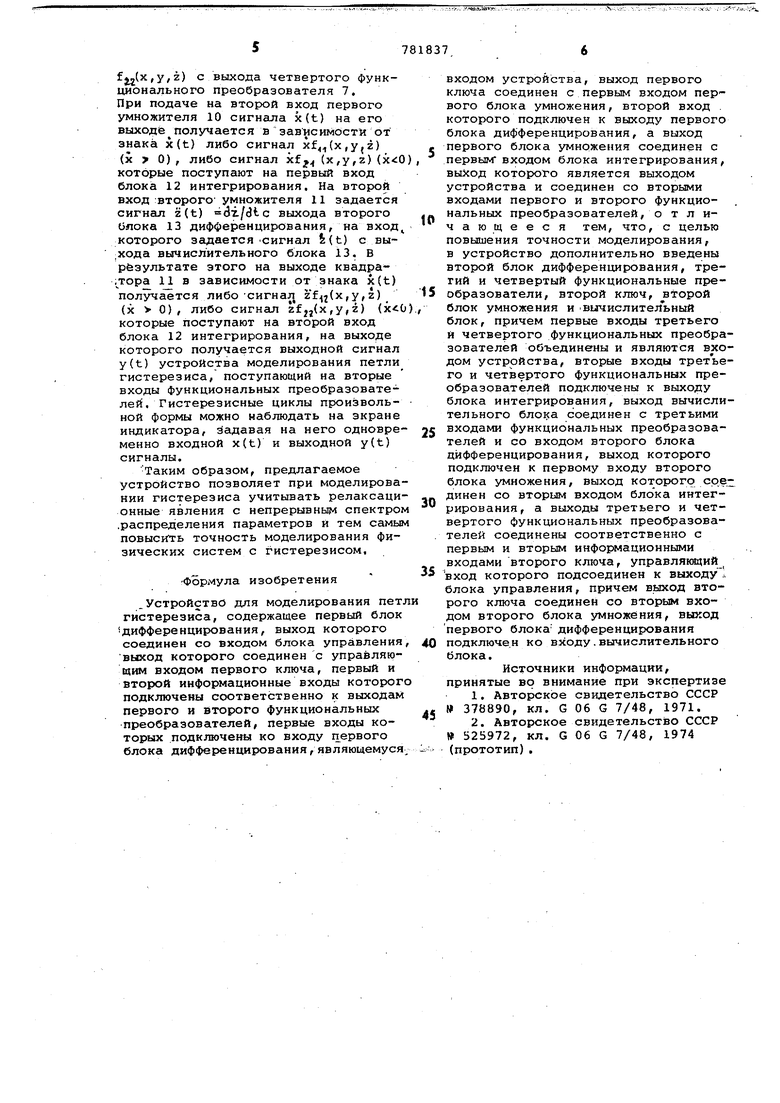

Изобретение относится к моделировани 9 процессов в физических системах при произвольных возмущающих воз действиях и любых исходных начальных цанных. Устройство может быть применено при моделировании на аналоговых вычислительных машинах систем, включающих элементы с гистерезисом, такие как упруго-демпфирующие элементы (образцы и конструкции из металлов, полимеров и др, материалов), узлы тренйя, магнитные элементы, сегнетоконденсаторы и т.д. Известно устройство для моделирования петли гистерезиса, содержащее блок воспроизведения однозначной кривой, сумматор, блок воспроизведения двузначной кривой типа Эллипс , выходной инвертор, дифференциатор и поляризованное реле, причем блок воспроизведения двузначной кривой содержит накопитель, входной сумматор, ;ин1ертор, дополнительный сумматор, умножитель, схему извлечения квадратного корня и масштабный усилитель 1, Это устройство не позволяет моделировать реальные гистерезисные петли, которые, как правило, по форме далеки от эллиптической. На практике форма петли может существенно меняться в зависимости от амплитуды и частоты входного сигнала элемента с гистерезисом, Наиболее близким по техническому решению к предлагаемому является устройство, состоящее из дифференциатора, блока управления, ключа, двух функциональных преобразователей, блока перемножения и интегратора. Входной сигнал x(t) подается непосредственно на вход дифференциатора и первые входы функциональных блоков. С выхода дифференциатора производная входного сигнала подается на вход управляющего блока, реагирующего на знак x(t), и на первый вход блока умножения. При положительном знаке x(t) управляющий блок подключает на второй вход блока умножения через ключ выход первого функционального блока, при отрицательном знаке x(t) - выход второго Функционсшьного блока. Сигнал с блока умножения подается на вход интегратора, на выходе которого получается выходной сигнал y(t) устройства моделирования гистерезиса. Этот сигнал y(t) задается одновременно н.а вторые входы функциональных блоков 2 , Описанное устройство осуществляет решение дифферен1 иальных уравнений dx Ф,и.1)|,, Ф2и,., , которые описывают семейства интеграл ных кривых. Восходящие и нисходящие ветви произвольного гйстереэйсМого цикла располагаются йй соотйё е йующих интегральных .кривУх, Однако, известное Устройство не учитывает релаксационное явления в гистерезисе. Цель изобретения - Учет в модели петли гистерезиса релаМвационных явлений с непрерывным епектром распределения параметров и, следовательно, повышение тс чности работы устройства модели ования петли гисте резиса. Для достижения цели в устройство для моделирования петли гистерезиса содержащее первый блок дифференцирования, выход которого соединен со входом блока управления, выход которого соединен с управляющим входом первого ключа, первый и второй инфор мационные входы которого подключены соответственно к выходгьм первого и второго функциональных ; преобразователей, первые входы которых подключены ко входу первого .блока дифферен цирования, являющемуся входом устрой ства, выход первого ключа соединен с первым входом первогб блока умножения, второй вхйд которого подключен к выходу первого блока дифференцирования, а выход первого блока умножения соединен с первыГ- входом бЛока интегрирования, вьисод которого является выходом устройства и соединен со вторыми входами первого и второго функциональных преЬбразователей, дополнительно введены второ блок дифференцирования, третий и четвертый функциональные преобразова тели, второй ключ, второй блок умножения и вычислительный блок, причем первые входы третьего и четвертого функциональных преобразователей объе динены и являются входом устройства вторыевходы третьего и четвертого функциональных преобразователей, подключены к выходу блока интегрирования, выход вычислительного блока соединен с третьими входами функциональных преобразователей и со входом второго блока дифференцирования, ьыяод Которого подключен к первому входу второго блока умножения, выход которого соединен со вторым входом интегрирования, зихощл третьег и четвертого функциональных преобра зователей соединены соответственно с первым и вторым информационными входами второго ключа, управляющий вход которого подключен к .выходу блока управления, причем выход второго ключа соединен со вторым входом второго блока умножения, выход пер- вого блока дифференцирования подключен ко входу вычислительного блока. На фиг. 1 представлена блок-схема предлагаемого устройства моделирования петли гистерезиса; на фиг. 2. произвольный гистереэисный цикл (сплошные линии) как результат пересечения двух семейств интегральных кривых (пунктирные линии); на фиг,3 явление релаксации в элементе с гистерезисом (вдоль АВ - скоростное нагруженйе элемента, вдоль ВС - релаксация, выражающаяся в плавном спаде выходного сигнала при фиксации уровня входного сигнала). Пунктирными линиями изображены кривые нагружения, получаемые при разных фиксированных скоростях изменения входного сигнала x(t). Устройство содержит первый блок 1 дифференцирования, второй блок 2 дифференцирования, блок 3 управления, первый функциональный преобразователь 4, второй функциональный преобразователь 5, третий функциональный преобразователь б и четвертый функциональный преобразователь 7, первый ключ 8, второй ключ 9, первый блок 10 умножения и второй , блок 11 умножения, блок 12 интегрирования, вычислительный блок 13. Принцип работы устройства состоит в следующем. Входной сигнал x(t) задается на вход первого блока 1 дифференцирования, на выходе которого пол5гчаем сигнал производной x(t), -и на первые входы функциональных преобразователей 4-7. Сигнал производной x(t). с выхода первого блока дифференцирования поступает на вход блока 3 управления, реагирующего на знак x(t), на второй вход первого умножителя 10 и вычислительный блок 13, на выходе которого получается сигнал z j k(t,s)x(s)ds, Этот сигнал поступает на третьи входы функциональных преобразователей. В результате на их выходах получаем: с первого 4 - сигнал fi(x,y,z), со второго 5 - f(x,y,z, с третьего б fil(Xfy,z) к с четвертого 7 fjj tVi Блок 3 управления, в зависимости от знака сигнала производной x(t), подключает через первый ключ В на первый вход первого умножителя 10 либо сигнал (x,у, z) с выхода первого функционального преобразователя 4,либо сигнал (х,у,г} с выхода второго функционального преобразователя 5,через второй ключ 9 на первый вход второго умножителя 11 подключается либо сигнал fjj(x,y,z) с выхода третьего функционального преобразователя б, либо сигнал ) с выхода четвертого функционального преобразователя 7. При подаче на второй вход первого умножителя 10 сигнала x(t) на его выходе получается взависимости от знака x(t) либо сигнал xf(x,yjz) (х 0) , либо сигнал xfj (х,у,z) ( которые поступают на первый вход блока 12 интегрирования. На второй вход :второго умножителя 11 задается сигнал z(t) 6i./dlc выхода второго Олока 13 дифференцирования, на вход которого задается .сигнал fe(t) с вы;хода вычислительного блока 13. В результате этого на выходе квадра;jopa 11 в зависимости от знака x(t) получается либо-сигнал (x,y,z) (х 0) , либо сигнал zfjj(x,y,z) ( которые поступают на второй вход блока 12 интегрирования, на выходе которого получается выходной сигнал y(t) устройства моделирования петли гистерезиса, поступающий на вторые входы функциональных преобразователей. Гистерезисные циклы произвольНОЙ формы можно наблюдать на экране индикатора, Задавая на него одновременно входной x(t) и выходной y(t) сигналы. Таким образом, предлагаемое устройство позволяет при моделирова нии гистерезиса учитывать релаксаци онные явления с непрерывным спектром .распределения параметров и тем самым повысигть точность моделирования физических систем с гистерезисом. Формула изобретения .Устройство для моделирования пет гистерезиса, содержащее первый блок 5дифференцирования, выход которого соединен со входом блока управления выход которого соединен с управляющим входом первого ключа, первый и второй информационные входы которог подключены соответственно к выходам первого и второго функциональнЕлх преобразователей, первые входы которых подключены ко входу iiepBoro блока дифференцирования,являющемуся входом устройства, выход первого ключа соединен с первым входом первого блока умножения, второй вход . которого подключен к выходу первого блока дифференцирования, а выход первого блока умножения соединен с первым входом блока интегрирования, выход которого является выходом устройства и соединен со вторыми входами первого и второго функциональных преобразователей, о т л ичающееся тем, что, с целью повьииения точности моделирования, в устройство дополнительно введены второй блок дифференцирования, третий и четвертый функциональные преобразователи, второй ключ, второй блок умножения и Вычислительный блок, причем первые входы третьего и четвертого функциональных преобразователей объединены и являются входом устройства, вторые входы третьего и четвертого функциональных преобразователей подключены к выходу блока интегрирования, выход вычислительного блока соединен с третьими входами функциональных преобразователей и со входом второго блока дифференцирования, выход которого подключен к первому входу второго блока умножения, выход которого соединен со вторым входом блока интегрирования, а выходы третьего и четвертого функциональных преобразователей соединены соответственно с первым и вторым инфОЕ 1ационными входами второго ключа, управляющий вход которого подсоединен к выходу 1 блока управления, причем вькод второго ключа соединен со вторым входом второго блока умножения, выход первого блока дифференцирования подключе.н ко входу. вычислительного блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 378890, кл. G 06 G 7/48, 1971. 2.Авторское свидетельство СССР W 525972, кл. G 06 G 7/48, 1974 (прототип).

Wf

Z(i)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования петли гистерезиса | 1977 |

|

SU679996A1 |

| Устройство для моделированияпЕТли гиСТЕРЕзиСА | 1979 |

|

SU830423A1 |

| Устройство для моделирования петли гистерезиса | 1976 |

|

SU615497A2 |

| Устройство для моделирования петли гистерезиса | 1976 |

|

SU710050A2 |

| Устройство для моделирования петли гистерезиса | 1975 |

|

SU525972A1 |

| Устройство для моделирования сухого трения | 1983 |

|

SU1103251A1 |

| Устройство для воспроизведения нелинейности типа петли гистерезиса | 1980 |

|

SU968822A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Устройство для моделирования петли гистерезиса | 1975 |

|

SU575660A1 |

| Устройство для моделирования петли гистерезиса | 1988 |

|

SU1550542A1 |

Авторы

Даты

1980-11-23—Публикация

1978-06-01—Подача