(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ДИФФЕРЕНЦИАЛЬЙЫХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714407A1 |

| Устройство для решения систем дифференцильных уравнений | 1977 |

|

SU717778A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU705454A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Устройство для формирования сигнала управления с оптимальными коэффициентами обратной связи | 1984 |

|

SU1242913A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для моделирования дифференциальных уравнений | 1989 |

|

SU1727130A1 |

| Устройство для нахождения оптимального вектора решения системы линейных неравенств | 1985 |

|

SU1315996A1 |

| АДАПТИВНАЯ СИСТЕМА ТЕРМИНАЛЬНОГО УПРАВЛЕНИЯ | 2012 |

|

RU2500009C1 |

1

Изобретение относится к области вычислительной техники и может быть применено для решения с высокой точностью систем обыкновенных нелинейных дифференциальных уравнеНИИ, нап15имер, в системах идентификации и управления динамических объектов. ,

Известны устройства для решения систем обыкновенных нелинейных дифференциальных уравнений 1, содерт Жсоцее блок управления, блок памяти, блоки управляемых ключей, блоки умножения, блоки сумматоров, интеграторов, функциональных преобразователей. Известные устройства позволяют находить решение систем обыкновенных дифференциальных уравнений первого порядка в результате предварительного определения вектора производных искомых неизвестных,, и последующего его интегрирования.

Известно устройство 2 для моделирования систем дифференциальных уравнений, содержащее блок управления, аналого-цифровой и цифроаналоговый преобразователи, блоки умножения, блоки аналоговых сумматоров, интеграторов, гибридных функциональных преобразовате.пей, рёгистр гсЩрё

са, дешифратор адреса, блок памяти, триггер записи, блоки управляемых ключей. Известное устройство позволяет находить решение систем обыкновенных нелинейных дифференциальных уравнений первого порядка, причем операции интегрирования, умножения, суммирования быстройзменяющихся переменных осуществляется в

0 аналоговой части устройства.

Основным недостатком данного устройства является сравнительно невы-сокая точность вычислений. Это обусловлено наличием существенных методи5ческих и инструментальных погрешностей. Так, необходимость квантования по времени всех или части компонент вектора правых частей в случае ана0логового интегрирования приводит к появлению значительной методической погрешности. Уменьшение последней путем повышения частоты квантования, либо применения сложных ана5логовых экстраполяторов приводит либо к увеличению требуемого быстродействия части устройства, определяющей квантованные значения вектора правых Частей, либо к увеличению инструментальной погрешности.

0

Целью настрявдёго изобретения вляется увеличение точности устрой тва для решения систем дифферениальных уравнений. Это достигаетя тем, что устройство для реше- ния систем дифференциальных уравнений, содержащее блок управления, блок умножения, блок памяти, блок сумматоров и две группы элементов , дополнительно содержит блок рекурЕ)ентных вычислений, группу И умноителей, блок сравнения, три блока накапливающих сумматоров и блок сдвига, причем выходы ц умножитеей группы соединены со входами блока суг маторов, выходы которого подключены к первой группе входов блока памяти и к первой группе вхо- .дов блока умножения, вторая группа входов блока умножения подключена к первой группе выходов блокапамяти и группе входов первого блока накапливающих сумматоров соответственно, входы HI умножителей группы подключены ко -второй группе выходов блока памяти, выходы первого блока накапливающих сумматоров подключены к первому входу блока рекуррентных вычислений, первый, второй, третий, четвертый и пятый выходы блока памяти подключены соответственно к второму, третьему, четвертому, пятому и шестому входам блока

рекуррентных вычислений, первый и второй выходы которого подключены к входам элементов И первой группы, выходы ксэторых подключены к первому

§х6ду TpeTbefo. Яблока накапЛйвающих сумматоров и к седьмому входу блока рекуррентных вычислений, второй выход которого подключен к второй группе входов блоха памяти и к перBOMS входу второго блока накаппивающих сумматоров, первый выход кох орого подключен к первому зходу олока сдвига, второй и третий входы которого подключены к шестому выходу блока памяти, второй выход второго блока накапливакяцих сумматоров и вьаход блока сдвига подключены к входам элемен гов И второй группы, первые выходы которых подключены к первой группе входов третьего блока накапливающих сумматоров, выход которого соединен с первым входом блoka сравнения, выход которого подключен ко входу блока управления, выходы элементов И второй группы подключены к второй группе входов третьего, блока накапливающих сум- маторов и к восьмому входу блока рекуррентных вычислений,- выходы блока управления подключены соответственно к первому входу блока памяти, входу первого блока накапливающих сумматоров, второму входу второго блока накапливающих сумматоров, четвертому входу блока сдвига, входам элементов И первой и

второй групп, входу третьей группы накапливающих сумматоров и ко второму входу блока- сравнения, блок рекуррентных вычислений содержит группу элементов ИЛИ, две группы умножителей, группу сумматоров, элементы НЕ, выходы элементов ИЛИ группы подключе.ш к первым входам умножителей первой группы, вторые входы которых подключены к пятому входу блока рекуррентных вычислений выходы умножителей второй группы подключены к первым вхолам сумматоров группы, вторые и третьи входы которых подключены соответственно к выходам умножителей первой группы и трётьей5 вх:оду блока, выходы умножителей третьей группы подключены к второму выходу блока непосредственно и через элементы НЕ к первому выходу блока, шестой, седьмой и Восьмой входы которого соединены с первыми, вторыми и третьими входами элементов ИЛИ группы, первые и вторые входы-умножителей группы подключены соответственно к выходам сумматоров группы и второму Jзxpдy блока, первый и четвертый входы которого соединены с первыми и вторыми входами умножителей второй группы.

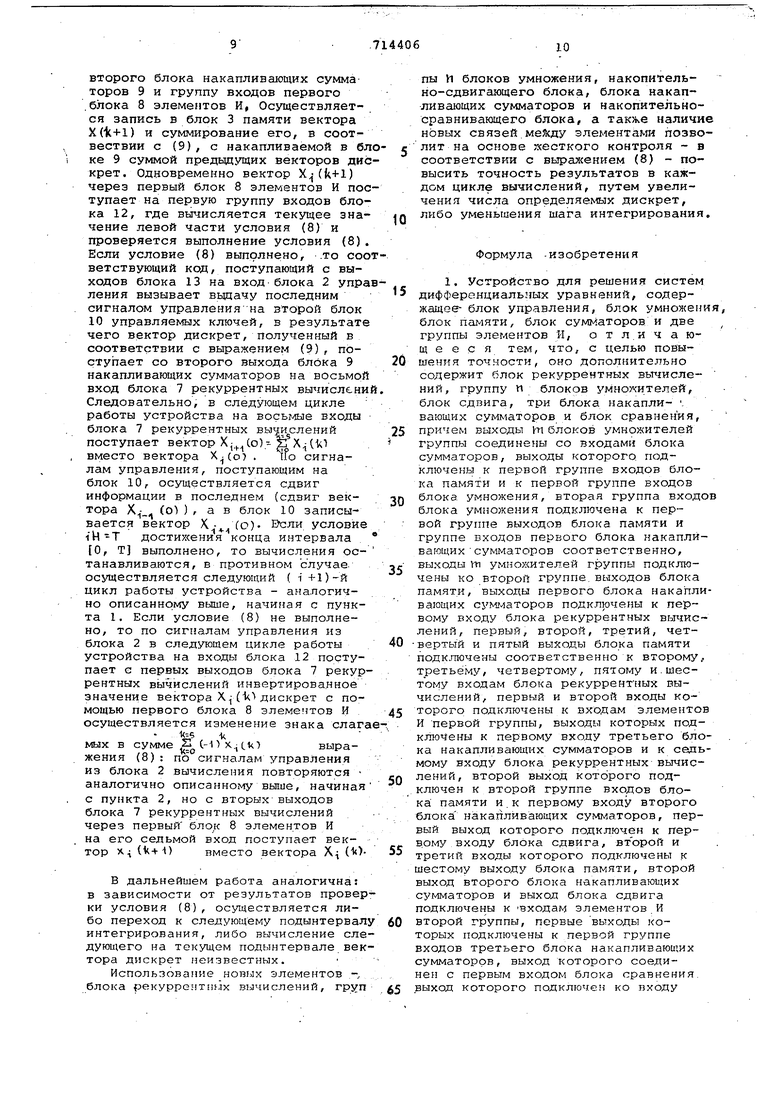

На чертеже представлена блоксхема устройства для решения слстем дифференциальных уравнений.

Устройство содержит группу И умножителей Г, блок 2 управления, блок 3 памяти, блок 4 с/мматоров, блок 5 умножения, блок б накапливающих Сумматоров, блок 7 рекуррентных вычислений, первую группу 8 элемен- тов И, блок 9 накапливающих сумматоров, блок 10 сдвига, вторую группу 11 элементов И,блок 12 накапливающих сумматоров, блок 13 сравнения.

Каждый блок группы П блока 1 уйножсния состоит из m умножителей по размерности вектора обрабатываемых величин, то есть группа и блоков

1умножения образует матрицу умножителей 1 - 1, 2 - 1, ...m-i, 1 - 2,

2- 2, И1- 2, 1 -(П -1), 2 - ( п - 1) , ...,П1-(П- 1), 1 -и, 2 -П,...., ш - И . Блок 4 сумматоров состоит изmсумматоров 4 - 1, 4 - 2, ...,

4- Hi. Блок 5 умножения состоит из П1 умножителей 5-1,5 -2, ...,

5- hi. Аналогичную структуру имеют Все блоки умножения, блоки сумматоров, накапливающих сумматоров, элементов ИЛИ, элементов НЕ входящие .в Состав блока рекуррентных вычислений, запоминающих регистров.

Работу предлагаемого устройства можно пояснить на примере решения систем дифференциальных уравнений вида:, . , ,,,: .

,.(,х( - (1) где X(t) jx.(t) J - вектор неизвест5 ных. ,,о , B boq-i матрицы пос.тоянных коэффициентов,(i) fj,(tU-вектор правых частей (t)(t -нелинейная вектор-фукнция, t-время, х(о) - значение Шпри i-причем Ш допускает разложение в ряд Тейлора в окрестности некоторой точки Х , т. е. )-s(y.g.+4(Xg)xU) „ r.(t)-x-. (р) . Схад-Хр.д V-рг ( (. (2). Здесь bpfxC-t) - остаточный член ряда. ГЛис/оЛ) ) Л Для решения с помощью предлага мого устройства система дифференциальных уравнений (1) должна быт представлена на основе правил и формул .преобразований Тейлора . (Т-преобразований), определяющих связи между оригиналом ХШи его ;T и9oбpa xeниeм Х()в соответствии с соотношениями 4 L--W &)«.. где - символ перехода отХ()к Х и, наоборот, хШ , W постоянный коэффициент, имеющий ра мерность i , 1 - аргумент, прини мающий целочисленные значения О, 1 ...,оо, в виде соответствующие этр системе дифференциальных уравнений Т-изображений. Для общего случая, кбгда радиус сходимости ряда (3) может быть меньше интервала О, Т интегрирования системы (1), послед прежде чем перейти к ее Т-изображе ниям, должна быть предварительно представлена, путем подразделения тервала О, т на N равных подинтервалов Н T/N , в которых ряд (3) заведомо сходится, в виде системы локальных уравнений; +Ах(гг))-(С), x.(obx.(iH где г(-с)(1Н+г), 4(t;)--.(x.,:u,)x.(-D)-xJ Г(х -,V .fciHl il .-) j-« ч-... P r., OitiH,i O,A,.. ,N-1 Систему (4) получают из исходной системы дифференциальных уравнений (1) в результате последовательного переноса начала координат из точки to О в точку , причем Т имеет с№дсл локального времени, изменяющегося от до ТьН, а связи между 1-ми ( 1+1)-м локальными системами уравнений определяют из, условия непрерывности x(i) - ( соответствии с (3), система Т-уравнений, изображающих - без учета остаточных членов ряда (2) систему локальных дифференциальных уравнений (4), принимает вид; , ,,.., (5) X(VM.Ha,x..(i;)....(V)... X.{o)--NCiH),cv 1,2,...,m,; где YV- ( - 1 H дискрета 5-6 функции, изображающей с|,ю компоненту вектора -i х (г:), дискрета функции,, изображающей к компоненту ) вектора (е) -rof«J K дискрета функции, изображающей q/ ю компоненту (т) вектора f (Ь номер последнего из учитываемых членов ряда (2) , причем; .U (.O x(i(.ai ),V,H --: x,uvx.(4|;;: . E - v - girt4 - -V l -Тггизображениб; степени оригинала x -q. (tri - x g f Z -q,. Предлагаемое устройство работает следующим образом. .В соответствии с (5) для кг сдого 1-го подынтервала интервала О, Т интегрирования устройства вычисляет о совокупность векторов дискрет -„ (| на основе соотношений: Р:С .(Х )-x )(1c)-... -V m -V11 - .m )(o)x(,1,...,m, / то есть определяет вёктьШ дискрет л(o),X(),...,X - (5J, где s-H-M -мак симальное число учитываемых на. подынтервале интегрировании дискре Число фактически учитываемых на л подынтервале дискрет и величина шага Н интегрирования кбнтролируются в УстройстеГ аГбснрйеебоТ шенйяурпрёделяёмЬгь свойствами npeoegiaidiaHrilfi (3) : .|Vl).(M-X..(o)E; гДе ё - заданная величина, харак-. теризующая требуемую точность вычис лений. Если число совпадающих цифр (разрядов) в правой и левой частях выражения (8) недостаточно, то вычисления повторяются с целью определения большего числа дискрет Х (1 (либр при уменьшенном шаге Н ). Если условие (8) выполняется удовлетворительной точностью, то устройство вычисляет вектор первых дискрет ( 1+1)- го подынтервала интегрирования в соответствии с выражением-.-чч.-,,,. :- ...... .. , .... .. ... ,.H°(, получа1е№м на основе свойств соотношений (3), (4), (5), после чего определяются векторы дискрет (+-1 ) i4i (2),..., Х( S ) Вычисления повторяются аналогично до достижения конца интервала О, Т интегрирования системы (1). Работа устройства начинается с ввдачй управляющих сигналов из блока; 2 уйЩШёнНя на -первый вход блока 3 памяти и накопйтелетрсраВнИв ающего блока 9. При Пбступлении этих сигналов п 6исходйт счйтывание из блока 3 памяти и запись 9 ycjiOBi ft. бдно-, временно из блока 3 памяти на шестой в:х:од блока 7 рекуррентных вычис лений поступает вектор ХоСо). 1. По сигналам из блока 2 управления осуществляется установка в блоков накапливающих сумматоров . Припоступлений на первый вход блока .3 памят соответству ющиксйгнгшо из блока ; управления происходит считывание из блока 3 на первые входы первого блока 1 умножения (1-1, 2-1, ..., И1-1) группы VI блоков 1 ТййоТ«ёййй--1гёТ тО)а коэффициентов i (Хоч) , а на вторые входы блока - считывание кода единицы. При поступлении лов из блока 2 на первый вход блока 3 1ЙШяЖШ п8ш1ёДйёгд на вторШ входы 5 умнржен11я считывается код единицы . ШЩгаа5ШгШ:ШвйШййГ1 блока 2 на вход блока 6 направляющих сумматоров осуществляется суммирование первоначально установленного в нем кода нуля с величиной вектора y: CXg-i ) поступающего с выходов блока 5 умножения. 2. Из блока 3 памяти считывается .Haif первые входы первого блока 1 умножения (1-1, .2-1, ..., «-) значение вектора Z (1{) для текущего значения k , на вторые входы код единицы. На вторые входы блока 5 умножения из блока 3 памяти считывается значение вектора (Xg-). По сигналам управления-из блока 2 в блоке б накапливающих сумматоров осуществляется суммирование значения вектора v (X g.- ) и вектора (хg-.,-), Zi М поступающего с выходов блока 5 умноженин, т. е. вычисляется сумма первых двух слагаемых ). 3. Из блрка пдмяти на первые входы группы h блоков умножения считываются значения векторов (f.}, на вторые входы - значения векторов Z -CI -Of-k s р причем для первого блока О, для второго (.- 1 и т. д. Таким образом на выходах блока 4 сумматоров формируется зн ачение вектора Zj t в соответствии с выражениями (6). По сигналам управ- . ления из блока 2 управления полученное текущее значение (k) записываетс я в блок 3 . На вто- . рыёвхЬд1Й блока 5 умножения считываете я соотёШтствутащёёзначение vfCi HP и полученное. Значение очередного слагаемого (x.jZCK)/P -с выхода блока 5 умножения поступает на входы блока б накапливающих сумматоров, где суммируется с пре ауйшми значениями (1) .Описан ные операции повторяются, начиная Гспункта-3, m раз, т. е. вычисляется текущее значение Y.,- (() По сигналам управления из ,2 инвёртйрованный вектор . (о) дискрет с выхода блока 10 через блок 11 элементов И поступает на группу входов третьего 5лока 12 накапливающих сумматоров, По сигналам управления, поступающим из бло- . ка 2 на вход блока 12, осуществляется суммирование занесенного первоначально в него .кода нуля и значения вектора t 1 (о) дискрет. Из блока 3 памяти на второй третий, четвертый и пятый входы блока 7 рекуррентных вычJHcлeний считьаваются, соответственно, значения H/(),F,-Ck),t-B),C-A), т. е. реализуются соотношения (7) вычисляется текущее значениевектора А . (kH) дискрет, которые со второго выхода блока 7 рекуррентных ; вычислений поступает на вторую группу входов блока 3 памяти, первый вход второго блока накапливающих сумматоров 9 и группу входов первого .блока 8 элементов И, Осуществляется запись в блок 3 памяти вектора Xdt+l) и суммирование его, в соотвествии с (9), с накапливаемой в бл ке 9 суммой предьвдущих векторов ди крет. Одновременно вектор X -Ck+l) через первый блок 8 элементов И по тупает на первую группу входов бло ка 12, где вычисляется текущее значение левой части условия (8) и проверяется выполнение условия (8) Если условие (8) выполнено, .то соо ветствующий код, поступающий с выходов блока 13 на вход-блока 2 упра ления вызывает ввдачу последним сигналом управления на второй блок 10 управляемых ключей, в результате чего вектор дискрет, полученный в соответствии с выражением (9), поступает со второго выхода блока 9 накапливающих сумматоров на восьмой вход блока 7 рекуррентных вычислени Следовательно, в следующем цикле работы устройства на восьг ые входы блока 7 рекуррентных вычислений поступает вектор Х.,.(о).C-Rl вместо вектора Х(о7 . тГо сигналам управления, поступающим на блок 10, осуществляется сдвиг информации в последнем (сдвиг вектора Х.,- (о) ) , а в блок 10 записывается вектор X- (о). условие iM-T достижени я конца интервала , О, Т выполнено, то вычисления останавливаются, в противном случае. осуществляется следующий { -i +1)-й цикл работы устройства - ана.погично описанному выше, начиная с пункта 1. Если условие (8) не выполнено, то по сигналам управления из блока 2 в следующем цикле работы устройства на входы блока 12 поступает с первых выходов блока 7 рекур рентных вычислений инвертированное значение вектора X|(k дискрет с помощью первого блока 8 элементов И осуществляется изменение знака слаг -k мых в сумме -С-1)х(. жения (8): по сигналам управления из блока 2 вычисления повторяются аналогично описанному выше, начиная с пункта 2, но с вторых выходов блока 7 рекуррентных вычислений через первый блок 8 элементов И на его седьмой вход поступает вектор (k+l) вместо вектора (I)В дальнейшем работа аналогична: в зависимости от результатов провер ки условия (8), осуществляется либо переход к следующему подынтервал интегрирования, либо вычисление сле дующего на текущем подынтервале век тора дискрет неизвестных. Использование новых элементов .-, блока рекуррентных вычислений, груп пы И блоков умножения, накопительно-сдвигающего блока, блока накапливающих сумматоров и накопительносравнивающего блока, а также наличие новых связей.мейсду элементами позволит на основе jxecTKoro контроля - в соответствии с выражением (8) - повысить точность результатов в каждом цикле вычислений, путем увеличения числа oпpeдeляe ыx дискрет, либо уменьшения шага интегрирования. Формула -изобретения 1, Устройство для решения систем дифференциальных уравнений, содержащее- блок управления, блок умножения, блок памяти, блок сумматоров и две группы элементов И, о т л.и ч а ющ е е с я тем, что, с целью повышения точности, оно дополнительно содержит блок рекуррентных вычислеНИИ, группу и блоков умножителей, блок сдвига, три блока накапли- вающих сумматоров и блок сравнения, причем выходы И1 блоков умножителей группы соединены со входами блока сумматоров, выходы которого, подключены к первой группе входов блока памяти и к первой группе входов блока умножения, вторая группа входов блока умножения подключена к первой группе выходов блока памяти и группе входов перво.го блока накапливающих сумматоров соответственно, выходы г умножителей группы подключены ко второй группе,выходов блока памяти, выходы первого блока накапливающих сум.маторов подключены к первому входу блока рекуррентных вычислений, первый, второй, третий, четвертый и пятый выходы блока памяти подключены соответственно к второму. Третьему, четвертому, пятому и.шестому входам блока рекуррент 1ых вычислений, первый и второй входы которого подключены к входам элементов И первой группы, выходы которых подк.тж1Чены к первому входу третьего блока накапливающих сумматоров и к седьмому входу блока рекуррентных вычислений, второй выход которого подключен к второй группе входов блока памяти и.к первому входу второго блока накапливающих сумматоров, первый выход которого подключен к первому входу блока сдвига, второй и третий входы которого подключены к шестому выходу блока памяти, второй выход второго блока накапливающих сумматоров и выход блока сдвига подключены к входам элементов И второй группы, первые выходы которых подключены к первой группе входов третьего блока накапливающих сумматоров, выход которого соединен с первым входом блока сравнения, выход которого подключен ко входу

Авторы

Даты

1980-02-05—Публикация

1977-10-24—Подача