(54) АДАПТИВНЫЙ ЦИФРОВОЙ ФАЗОМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой фазометр | 1984 |

|

SU1401399A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Цифровой частотомер-фазометр | 1976 |

|

SU658496A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Преобразователь кода во временной интервал | 1986 |

|

SU1410279A2 |

| Цифровой фазометр-частотомер | 1983 |

|

SU1173342A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ФАЗОМЕТР | 1973 |

|

SU361447A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Преобразователь "фаза-код | 1980 |

|

SU938194A1 |

Изобретение относится к измеритель ной технике.и может быть использовано для измерения с повышенной точностью и быстродействием фазового сдвига между двумя периодическими сигналами при наличии аддитивной случайной помехи. Известно устройство, в котором из мерение сдвига фаз производится многократно (в каждом из нескольких периодов входных сигналов) с последующим определением среднего арифметического результатов замеров, содержащее два формирователя, выходы кото рых соединены со входами триггера, подключенного нулевым входом к управ ляющему входу ключа, импульсный вход которого соединен с выходом генерато ра -импульсов, а выход - со входом счетчика l. Недостатком его является недостаточная точность измерения. Известен также цифровой фазометр, содержащий счетчик и преобразователь фазового сдвига между двумя входными сигналами, выход которого соединен со входом схемы выделения заданного фронта сигнала и с первым входом эле мента И, второй и третий входы кото.рого соединены соответственно с выходом генератора высокой частоты и с выходом триггера. Фазометр автоматически производит заранее заданное число замеров фазового сдвига (в течение заданного числа периодов входных сигналов), выполняя одновременно деление результата каждого замера на их число и накапливая .сумму частных 2 Недостатки устройства состоят в невысоких точности и быстродействии, что обусловлено сильной зависимостью относительной погрешности измерения от измеряемой величины, причем эта погрешность резко возрастает с уменьшением измеряемого сдвига фаз. Цель изобретения - повышение точности и быстродействия. Поставленная цель достигается тем, что в устройство, содержащее счетчик, преобразователь фазового сдвига в длительность импульсов, выход которого соединен со входом блока выделения заднего фронта и с первым входом первого элемента И, второй и третий входы которого соединены соответственно с выходом генератора и с первым выходом первого триггера, введены второй триггер, второй и третий элементы И, ключ, элемент задержки, цифревой компаратор, логический узел, реверсивный счетчик и регистр, выходы которого являются,выходами устройства, причем выход первого элемента И соединен со счетным входом счетчика, выход генератора подключен к первому входу второго .элемента И, второй вход которого объединен с первым входом третьего элемента И и подсоединен к выходу второго триггера, а третий вход объединен с первым входом ключа и соединен со вторым выходом первого триггера, при этом его выход соединен с вьгчитаю1дим входом реверсивного счетчика, суммирующий вход которого подключен к выходу блока выделения заднего фронта, подключенного через элемент задержки ко второму входу третьего элемента И, а выходы - к входам логического узла, первый выход которого соединен с третьим входом третьего элемента И, подключенного выходом ко второму входу первого триггера и к первому входу регистра, второй выход соединен со вторым входом ключа, подключенного выходом ко второму входу регистра, а третий выход логического узла соединен с первым входом второго триггера и сбросовым входом счетчика, выходы которого соединены с разрядными входами регистра и входами цифрового компаратора, соединенного лыходом со Бторым входом второго т; иггора.

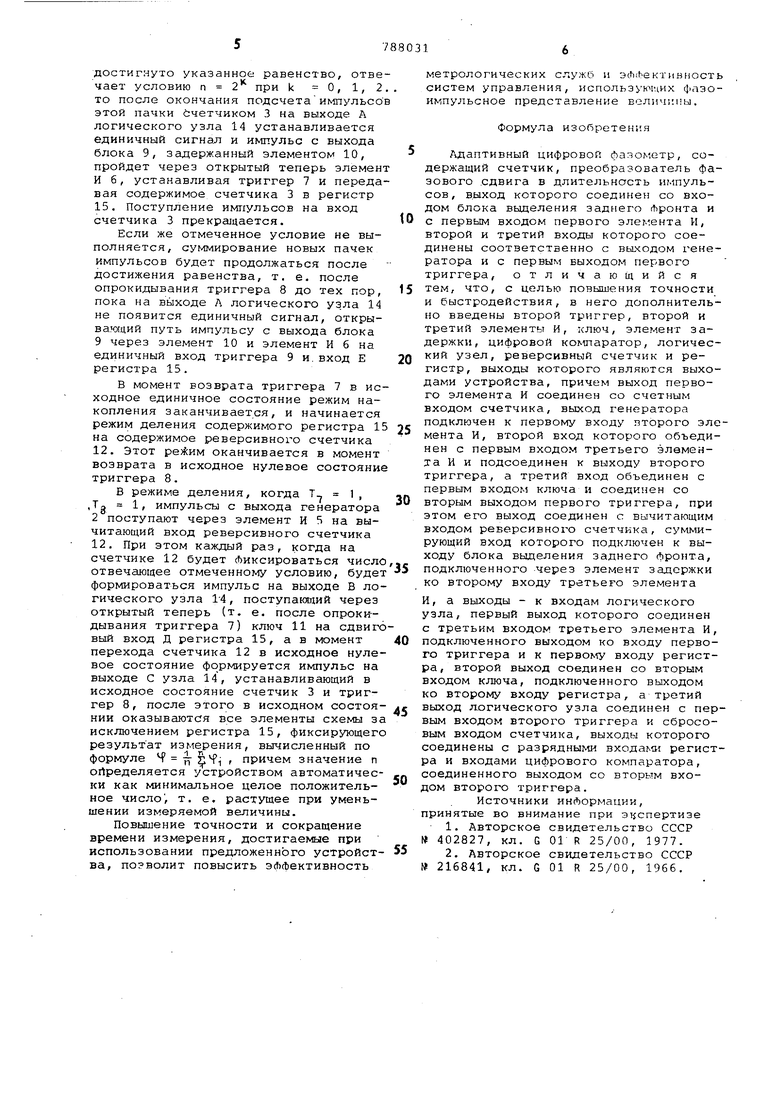

На чертеже приведена блок-схема устройства.

Устройство содержит преобразователь фазового сдвига в длительность импульсов 1, генератор квантующих импульсов 2,. счетчик 3«, первый, второй и третий элементы И 4, 5 , б , первый и второй триггеры 7, 8, блок 9 выделения заднего фронта, элемент задержки 10, ключ 11, реверсивный счетчик 12, цифровой компаратор 13, логический узел 14 (буквами А, В, С обозначены ее первый, второй и третий выходы соответственно) и регистр 15 (буквами Е и Д обозначены его первый и второй входы соответственно).

Фазометр работает следующим образом,

В исходном состоянии триггер 7 установлен в единицу, а триггер 8 - в нуль, при этбм на первых входах элементов И 5 и И 6 -и на третьем входе элемента И 4 единичный сигнаш отсутствует; счетчик 3 и реверсивный счетчик 12 установлены в нуль; цифровой компаратор 13 настроен на срабатывание (выработку выходного импульса) при выбранном числе N .

Принцип работы устройства состоит в том, что пачки импульсов стабильной частоты, формируемые на выходе элемента И 4 в интервалах времени, соответствующих сдвигу фаз в каждом из периодов входных сигналов (т. е.

во время выходных прямоугольных И7

пульсов преобразователя 1), поступают на счетчик 3 до тех пор, пока не выполнятся два условия: неравенство N i-N (1) (т, е , суммарное число импульсов пачек не меньше заранее заданного числа), число просуммированных пачек импульсов (иначе число отдельных замеров разности Фаз или число периодов входных сигналов, в течение которых ведется измерение) представляет собой целую степень числа 2. Фазометр может находиться в одном из трех режимов, второй из которых имеет два .подрежима. Режим работы определяется состояниями триггеров 7 и 8. Обозначим эти состояния через Т 5 и Те соответственно.

Исходное состояние Т 1

0. .

8

0.

0 т,

8

Режимы работы схемы сменяют друг друга в указанной последовательности, .после режима деления схема переходит в исходное состояние.

Пуск схемы осуществляется подачей импульса на первый (нулевой) вход триггера. После опрокидывания этого триггер1а импульсы с выхода генератора квантующих импульсов 2 начинают проходить, на счетный вход счетчика 3 в интервалах времени, когда на выходе преобразователя 1 поддерживается высокий потенциал, в конце каждого такого интервала (в г- оменты снятия высокого потенциала с выхода преобразователя 1) возникает импульс на выходе блока 9. Эти импульсы суммируются реверсивным счетчиком 12, через элемент И б они не проходят, пока отсутствует единичный сигнал хотя бы на одном из остальных его входов. Таким образом, счетчик 3 накапливает сумму i; , а реверсивный счетчик 12 фиксирует соответствующую величину п .

В момент, когда достигается равенство N N, возникает импульс на выходе цифрового компаратора 13, опрокидывающий триггер 8. Отметим, что номер пачки импульсов, при обработке которой это произойдет, будет обратно пропорционален измеряемому сдвигу фаз и прямо пропорционален величине N. Таким образом, точность измерений растет с ростом N, эта величина может быть выбрана так, чтобы при любом значении измеряемой величины относительная погрешность измерения-не превышала допустимрй. При конкретном выборе числа Ы следует учитывать, зависимость абсолютной ошибки от измеряемой величины.

Если оказывается, что номер пачки, при подсчете импульсов которой было

достигнуто указанное равенство, отвечает условию п 2 при k 0, 1, 2 то после окончания подсчетаимпульсов этой пачки йчетчиком 3 на выходе А логического узла 14 устанавливается единичный сигнал и импульс с выхода блока 9, задержанный элементом 10, пройдет через открытый теперь элемент И 6, устанавливая триггер 7 и передавая содержимое счетчика 3 в регистр 15, Поступление импульсов на вход счетчика 3 прекращается.

Если же отмеченное условие не выполняется, суммирование новых пачек импульсов будет продолжаться после достижения равенства, т. е. после опрокидывания триггера 8 до тех пор, пока на выходе Л логического узла 14 не появится единичный сигнал, открывааддий путь импульсу с выхода блока 9 через элемент 10 и элемент И б на единичный вход триггера 9 и,вход Е регистра 15.

В момент возврата триггера 7 в исходное единичное состояние режим накопления заканчивается, и начинается режим деления содержимого регистра 15 на содержимое реверсивного счетчика 12. Этот оканчивается в момент возврата в исходное нулевое состояние триггера 8.

В режиме деления, когда Т 1, Дд 1, импульсы с выхода генератора 2 поступают через элемент И 5 на вычитающий вход реверсивного счетчика 12, При этом каждый раз, когда на счетчике 12 будет Ликсироваться число отвечающее отмеченному условию, будет формироваться импульс на выходе В логического узла 14, поступакядий через открытый теперь (т. е, после опрокидывания триггера 7) ключ 11 на сдвиговый вход Д регистра 15, а в момент перехода счетчика 12 в исходное нулевое состояние формируется импульс на выходе с узла 14, устанавливающий в исходное состояние счетчик 3 и триггер 8, после этого в исходном состоянии оказываются все элементы схемы за исключением регистра 15, фиксирующего результат измерения, вычисленный по формуле Ч pj- sMi г причем значение п оЛределяется устройством автоматически как минимальное целое положительное число , т, е. растущее при уменьшении измеряемой величины.

Повышение точности и сокращение времени измерения, достигаемые при использовании предложенного устройства, позволит повысить эффективность

метрологических служб и Э(1 ективмость систем управления, использующих с1)азоимпульсное представление величины.

Формула изобретения

Адаптивный цифровой фазометр, содержащий счетчик, преобразователь фазового .сдвига в длительность импульсов, выход которого соединен со входом блока выделения заднего гпронта и

0 с первым входом первого элег.внта И, второй и третий входы которого соединены соответственно с ВЕЛХОДОМ генератора и с первым выходом первого триггера, отличающийся

5 тем, что, с целью повышения точности и быстродействия, в него дополнительно введены второй триггер, второй и третий элементы И, ключ, элемент задержки, цифровой компаратор, логический узел, реверсивный счетчик и ре0гистр, выходы которого являются выходами устройства, причем выход первого элемента И соединен со счетным входом счетчика, выход генератора подключен к первому входу второго эле5мента И, второй вход которого объединен с первым входом третьего элемента И и подсоединен к выходу второго триггера, а третий вход объединен с первым входом ключа и соединен со

0 вторым выходом первого триггера, при этом его выход соединен с вычитающим входом реверсивного счетчика, суммирующий вход которого подключен к выходу блока выделения заднего фронта,

5 подключенного через элемент задержки ко второму входу третьего элемента

И, а выходы - к входам логического узла, первый выход которого соединен с третьим входом третьего элемента И,

0 подключенного выходом ко входу первого триггера и к первоь у входу регистра, второй выход соединен со вторым входом ключа, подключенного выходом ко второму входу регистра, а третий выход логического узла соединен с пер5вым входом второго триггера и сбросовым входом счетчика, выходы которого соединены с разрядными входами регистра и входами цифрового компаратора, соединенного выходом со вторым вхо0дом второго триггера.

Источники инЛормации, принятые во внимание при Э1$спертизе

5

У, В У од

Х,hT43

Bhtxoff

-

75

/J

/2

10

Авторы

Даты

1980-12-15—Публикация

1978-12-15—Подача