(54) АНАЛОГОВАЯ МОДЕЛЬ ТРАНЗИСТОРА

лителей, вторые входы которых подключены к соответствующим граничным узлам первой группы CG-сетки и к выходам соответствующих управляемых источников тока группы. Первый вход управляемого источника тока соединен с общим выводом граничных узлов второй группы СО-сетки, второй вход с выходом экспоненциального усилителя, первый вход которого является коллекторным выводом модели и соединен с первой обкладкой накопительного конденсатора. Второй вход экспоненциального усилителя соединен с общим выводом граничных узлов второй группы / -сетки, со второй обкладкой конденсатора и с третьим входом управляемого источника тока. Вывод базы модели подключен к одному из внутренних узлов / -сетки.

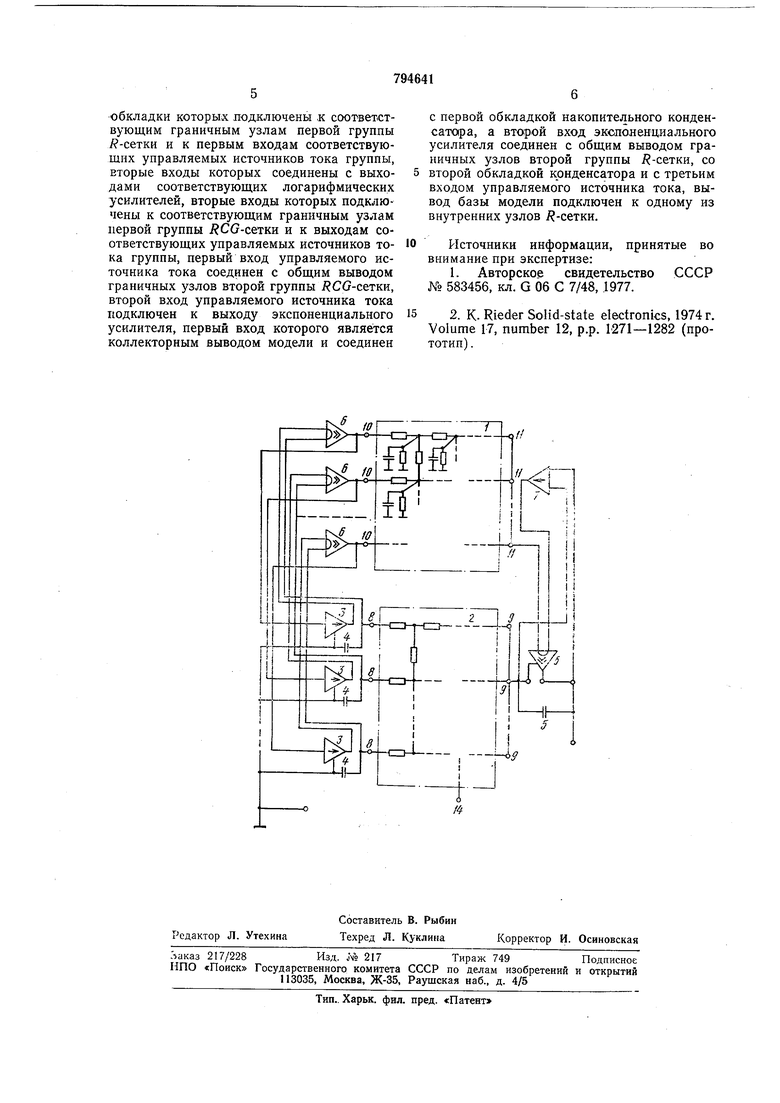

На чертеже дана принципиальная схема предложенной модели.

Модель содержит RCG-сетку I, / -сетку 2, логарифмические усилители 3, группу накопительных конденсаторов 4, накопительный конденсатор 5, управляемые источники тока 6, экспоненциальный усилитель 7, узлы 8 эмиттерной границы J -сетки, выводы 9 коллекторной границы -сетки 10, узлы эмиттерной границы CG-сетки и вывод // коллекторной границы / СО-сетки.

Модель работает следующим образом.

Логарифм ический усидитель, экспоненциальный усилитель и управляемые источники тока образуют совместно с RCG и Rсеткой электрическую цепь, процессы в которой подобны процессам в БТ, работающем в режиме больщого сигнала. В модели перенос неосновных носителей в базе транзистора моделируется С(5-сеткой. Избыточная концентрация неосновных носителей Р и их ток /р связаны с потенциалом i/p и током 1р сетки масщтабным соотнощением:

Цр

т - -,

К, RP

где , K.I - масщтабы концентрации и тока.

Перенос основных носителей в базе моделируется jR-сеткой.

Потенциал базы ф и ток неосновных носителей In связаны с потенциалом ф и током / сетки масщтабными соотношениями:

I м

Л1

Т

п

In-Ф

к..

К,

где /Со - масщтаб потенциала.

Ау удобно принимать равным 1. Переходные процессы в модели по сравнению с моделируемым транзистором замедлены к K.t раз.

При заданных /(р, W/, К-с и K,t сопротивления RP емкость С и проводимость G элементов У СО-сетки и сопротивление Rn

элементов / -сетки рассчитываются по формулам:

KtK/q xfi y

С Л/ .

Кр

K,

K,

« /СрДу

гдеq - заряд дырки;

Dp - коэффициент диффузии неосновных носителей: а - удельная проводимость материала базы транзистора; Ал:, Дг/ - щаг сетки по осям х к у.

Граничные условия для CG-ceтки задаются управляемыми источниками тока 6 и экспоненциальным усилителем 7, для Rсетки - логарифмическими усилителями 3, конденсаторами 4, управляемым источником тока 6 и эквивалентным генератором электрической цепи, в которой используется предлагаемое устройство.

Указанное включение управляемых источников тока и ЭДС обеспечивает организацию автоматического итерационного процесса, заключающегося в вычислении граничных условий для сеток по заданным параметрам эквивалентных генераторов электрической цепи, в которой используется предлагаемое устройство.

Время одной итерации определяется временем задержки сигнала в операционных усилителях и может составлять единицы микросекунд, поэтому масщтаб Kt выбирается таким образом, чтобы длительность переходных процессов в устройстве составляла 100 МКС и более.

Предлагаемая модель позволяет рассчитывать параметры .транзистора в режиме большого сигнала. Кроме того, модель отражает особенности реальной геометрии транзистора, что повыщает точность воспроизведения характеристик в 2-5 раз и более в зависимости от физико-тсиполопических параметров и режима работы транзистора.

Формула изобретения

Аналоговая модель транзистора, -оодержащая RCG- и У -сетки, группу накопительных конденсаторов, накопительный конденсатор и экспоненциальный усилитель, о тл и ч а ю щ а я с я тем, что, с целью повышения точности воспроизведения характеристик транзистора, в модель введены группа управляемых источников тока, управляемый источник тока и логарифмические усилители, причем эмиттерный вывод модели соединен с первыми входами логарифмических усилителей первыми обкладками накопительных конденсаторов группы, вторые

обкладки которых лодключены к ссютвет.ствующим граничным узлам первой группы / -сетки н к первым входам соответствующих управляемых нсточников тока группы, вторые входы которых соединены с выходами соответствующих логарифмических усилителей, вторые входы которых подключены к соответствующим граничным узлам первой группы RCG-сетки и к выходам соответствующих управляемых источников тока группы, первый вход управляемого источника тока соединен с общим выводом граничных узлов второй группы RCG-сеткк, второй вход управляемого источника тока подключен к выходу экспоненциального усилителя, первый вход которого является коллекторным выводом модели и соединен

с первой обкладкой накопительного конденсатора, а второй вход экспоненциального усилителя соединен с общим выводом граничных узлов второй группы -сетки, со второй обкладкой конденсатора и с третьим входом управляемого источника тока, вывод базы модели подключен к одному из внутренних узлов / -сетки.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 583456, кл. G 06 С 7/48, 1977.

2. К. Rieder Solid-state electronics, 1974г. Volume 17, number 12, p.p. 1271-1282 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования транзистора | 1986 |

|

SU1388911A1 |

| Аналоговая модель транзистора | 1980 |

|

SU900297A1 |

| Устройство для моделирования транзистора | 1984 |

|

SU1170472A1 |

| Устройство для моделирования диода | 1984 |

|

SU1228124A1 |

| Устройство для моделирования тиристора | 1984 |

|

SU1164765A1 |

| Модель транзистора | 1980 |

|

SU928377A1 |

| Устройство для моделирования транзистора | 1979 |

|

SU868787A1 |

| Сеточная модель | 1978 |

|

SU746586A1 |

| Узловой элемент сеточной модели для решения задач тепломассопереноса | 1988 |

|

SU1522246A1 |

| Устройство для задания граничных условий | 1978 |

|

SU694872A1 |

/4

Авторы

Даты

1981-01-07—Публикация

1979-01-17—Подача