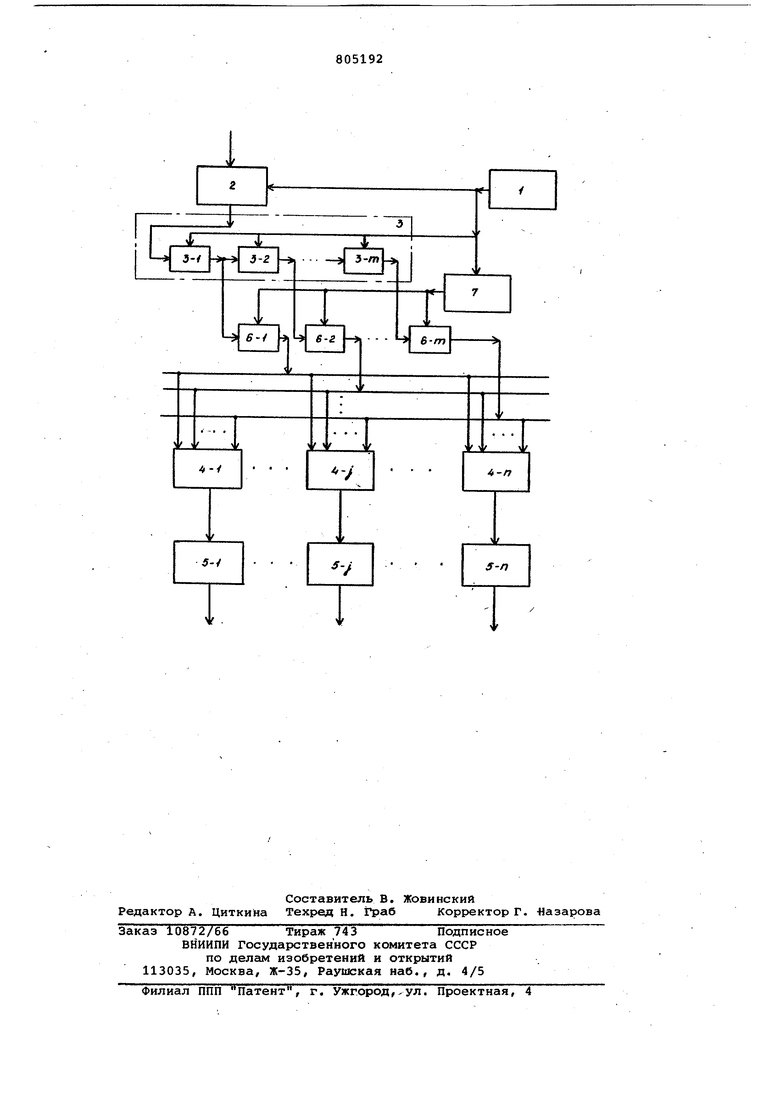

(54) ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СПЕКТРАЛЬНЫЙ АНАЛИЗАТОР ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ ральной огибающей, вход каждого из которых соединен с выходом соответствующего блока взвешенного суммирования ГдЗ. . Если обозначить через Z(t) (j«l,2..,п).сигнал на выходе J -го блрка взвешенного суммирования, чере i-и весовой параметр, соответст ующий i-му входу j-ro блока, то функция, реализуемая данным j-ым блоком взвешенного суммирования, вы раженная в аналитической форме, может быть записана в следующем виде: Л 1 Лt ...(i) .-.m; .a...n, ., V i - / гдеу{) сигнал, поступающий на i-и 8ХОД j-ro блока взвешенного суммирования с выхода i-ro блока задержки Следовательно, для формирования одного значения выходного сигнала Z(t) j-му (,2.,.n) блоку взвешенного суммирования в соответствии с формулой (i) необходимо выполнить rt операций сложения и m операций умножения. Время, затрачиваемое для формирования одного значения .выходного сигнала в блоке взвешенногосуммирования, обозначим через ТГ , Элементы блока задержки совместно с блоками взвешенного суммирования образуют набор из полосовых цифровых фильтров, причем выход j-ro блока взвешенного суммирования соответствует выходу j-ro полосового фильтра Специальные блоки - блоки выделения спектральной огибающей,реализуют функцию выделения с заданной точностью спектральных огибающих, которая сводится к детектированию и сглаживанию с определенной постоянной времени сигналов, поступающих на их входы с выходов соответствующих блоков взвешенного суммирования 2} Недостаток известного устройства относительно низкое быстродействие при цифровой обработке сигнала вслед ствие того, что быстродействие известного устройства определяется самыми Медленными блоками, входящими в его конструкцию. Такими медленными блоками в известной конструкции являются блоки взвешенного суммирования, так как ими реализуется относительно сложная функция, включающая в себя умножение всех входны сигналов, поступающих с выходов бло ка задержки на соответствующие весо вые параметры, и последукядее суммирование даннЁлх произведений. Поэтом быстродействие известного устройства определяется предельной частотой входного сигнала через время взве- шенного суммирования T/gj. Цель изобретения - увеличение быстродействия устройства при обработке сигналов. V Поставленная цель достигается те что в цифровой многоканальный спект ральный анализатор; содержаидий аналого-цифровой преобразователь, информационный вход которого является входом устройства, а управляющий вход подключен к выходу генератора импульсов, выход аналого-цифрового преобразователя соединен со входом блока задержкиу управляющий вход которого подключен к выходу генератора импульсов, и в каждом канале блок взвешенного суммирования, выход которого подключен ко входу соответствующего блока выделения спектральной огибающей введены блок деления частоты и в каждый канал - регистр памяти, информационный вход каждого регистра соединен с соответствующим выходом блока задержки, управляющие входы регистров подключены к выходу блока деления частоты, вход которого соединен с выходом генератора импульсов, выходы регистров памяти соединены с соответствующими входами блоков взвешенного суммирования. Такое техническое решение конструкции цифрового параллельного спектрального анализатора основывается на следующих двух известных из теории свойствах спектральных преобразователей . Максимальная частота изменения спектральной огибанмцей по выходу полосового фильтра не превышает половины его полосы пропускания. Спектр аналогового сигнала после преобразования его в цифровую форму повторяется периодически в виде нижнего и верхнего боковых спектров около частот, кратных частоте преобразования сигнала в цифровую форму. Из этих свойств следует, что частоту преобразования в цифровую форму спектральной огибающей а следовательно, и частоту следования отсчетов сигнала по выходу полосового фильтра можно брать, исходя из требований к точности выделения самой спектральной огибающей, а выделять ее по первому нижнему боковому спектру около частоты следования отсчета .по выходу полосового фильтра. Следовательно, в цифровом многоканальном (параллельном) спектральном анализаторе, состоящем из набора полосовых фильтров, полосы пропускания которых одинаковы и равны uf и равномерно перекрывают частотный рабочий диапазон Q-fp,отсчеты сигналов по вы-, ходам полосовых фильтров могут следовать без потери информации с частотой, равной по порядку значению величины полосы пропускания полосового фильтра. А так как- f значительно меньше . верхней границы fp рабочего частотного диапазона 0-fp , то на операции формирования одного отсчета выходного сигнала в блоках взвешенного суммирования, при прочих условиях. можно выделить значительно больше времени, если фиксировать на это вре мя выходные сигналы с GJIOKOB задержек . В описываемом устройстве фиксация выходных сигналов с блоков задержек производится в регистрах памяти. Час тота перезаписи значений сигналов, хранящихся в регистрах памяти, определяется частотой следования импульсов записи, поступающих на управляющие входы данных регистров памяти из блока деления частоты. Частота следования импульсов записи в соответст вии с вышеизложенным может быть взята равной по порядку . значению Вели- чиныл. Следовательно, время, которое может быть отведено блоком взвешенного суммирования для формирования одного отсчета выходных сигналов определяется из следующего соотно7 шения: где некоторая константа, зависящая от конструкции блоков .вьоделения спектральной огибающей. На практике значение С может находиться в пределах от единищл до пяти, т.е. .liCjS В описываемом устройстве, как и в известном устройстве, Ы быстродействие определяется самыми медленными блоками. Такими медленными блоками являются блоки взвешенного суммирования. Операция же перезаписи сигналов из блоков задержек в регист ры памяти представляет собой операцию типа регистр-регистр, котораяобычно является одной из самых быстрых операций в цифровых вычислительных устройствах. Оценим быстродействие описываемого устройства. Как и для известного устройства под быстродействием понимается значе ние наибольшей частоты f в спектре сигнала, при которой данный сигнал может быть обработан предлагаемым устройством без внесения- частотных искажений. Можно показать, что наибольшая допустимая частота f, которая может содержаться в спектре сигнала и кото рая может быть обработана описываемым устройством без внесения частотных искажений, равна: io - г- где f ec n - число каналов, Из этого соотношения; следует, что при обработке сигналов известным {2 и предлагаемым устройствами, быстродействие предлагаемого устройства в . раз выше, чем быстродействие известного-. Этот выигрьош особенно вели при больших значениях n , т.е. при большом количестве- параллельных выходов . На чертеже приведена структурная схема, описываемого спектрального анализатора сигналов. Устройство имеет один вход и n выходов и содержит генератор 1, имеющий один выход, аналого-цифровой преобразователь 2, имеющий информационный вход, управляющий вход и выход, блок 3 задержки с m ячейками, каждая из которых имеет информационный вход, управляющий вход и выход, блоков 4 взвешенного суммирования, каждый из которых имеет m входов и один выход, n блоков 5-1,..., 5-j,...5-n выделения спектральной огибающей, каждый из которых имеет один вход и один выход, m регистров 6 памяти, каждый из которых имеет информационный вход, управляющий вход и выход, блок 7 деления частоты, имеющий вход и выход. , Информационный вход блока 2 подсоединен ко входу устройства, а выход - к информационному входу блока 3-1. Выход i-ro блока задержки подсоединен к информационному входу i+1-го блока задержки. Информационный вход i-ro регистра памяти подсоединен к выходу -го блока задержки, а выход - к i-му входу всех блоков 4 взвешенного суммирования. Выход j-ro блока 4-J взвешенного суммирования подсоединен ко входу j-ro блока 5-J выделения- спектральной огибающей, выход которого является j-ым выходом устройства. Выход генератора 1 подсоединен к управляющим входам блока 2 и блока 3. Вход блока 7 подсоеди«ен к выходу блока 1, а выход - к управляющим входам блоков б, Описываемое устройство является цифровым многоканальным (параллельным) спектргипьным анализатором, предназначенным для параллельного спектрального анализа электрических сигналов (выделения спектральных огибающих) в рабочем частотном диапазоне 0-fp, собранным на базе блоков задержки и блоков 4 взвешенного суммирования и имеющим один вход и n выходов. Устройство работает следующим образом. Аналоговый сигнал поступает на информационный вход блока 2, где осуществляется преобразование его в цифровую форму.- С выхода блока 2 цифровой сигнал в виде отсчётов в дискретные моменты времени, поступает на информационный вход блока 3 задержки. При этом частота следования отсчетов выходного сигнала блока 2 должна быть не меньше удвоенной величины fp (чтобы не было частотных искажений). Блок 3 задержек совместно с блоками 4 взвешенного суммирования, регистрами 6 памяти и блоком 7 деления частоты образуют набор изп полосовых цифровых фильтров с равными полосами пропускания af, равномерно перекрывающими частотный рабочий диапазон 0-fp. Причем выход j-ro блока взвешенного суммирования соответствует.,выходу j-ro полосового фильтра.

Следовательно, на вход такой системы из п полосовых фильтров (информационный вход блока 3) подается сигнал с выхода блока 2.

По выходу каждого такого полосового фильтра .{выходу соответствующего блока 4) выдаются отсчеты преобразованного фильтровой системой из п полосовых фильтров сигнала,

Поскольку частота изменения спектральной огиба ющей по выходу каждого полосового фильтра не превышает величины -//iAf , то частота следования отсчетов преобразованного сигнала по выходам блоков 4 выбрана исходя из точности выделения блоками спектральных огибакяцих, т.е. не меньшей, чем af, и равна частоте следования импульсов записи из блоков 7. По выходам блоков выдаются спектральные огибающие исходного сигнала в виде отсчетов в дискретные моменты времени, определяемые частотой следования сигналов на выходах блоков 4.

Таким образом, предлагаелвлй цифровой параллельный спектральный анализатор имеет широкий частотный и динами ческие диапазоны, при относительно несложных по конструкции блоках взвешенного суммирования. При числе выходов п, равном 100, и С-1 описанный цифровой параллельный спектральный анализатор имеет более чем на два порядка большее быстродействие по обработке сигналов, чем известный цифровой параллельный анализатор. Сложность же предлагаемой конструк ции увеличилась незначительно по сравнению с известной, поскольку один дополнительный регистр памяти значительно проще даже одного (не самого

сложного) блока в известном устройстве, а.именно блока задержек.

Формула изобретения

. Цифровой многоканальный спектральный анализатор злектрических сигналов , содержащий аналого-цифровой преобразователь, информационный вход которого является входом устройства, а управляющий вход подключен к выходу генератора импульсов, выход аналого-цифрового преобразователя соединен со входом блока задержки, управляющий вход которого подключен к выходу генератора импульсов, и в каждом канале блок взвешенного суммирования, выход которого подключен ко входу соответствующего блока выделения спектральной огибающей, отличающийся тем, что, с целью увеличения йастродействйя, в устройство введены блок деления частоты и в каждый канал-регистр памяти, информационный вход каждого регистра соединен с соответствующим выходом блока задержки, управляющие входы регистров подключены к выходу блока деления частоты, вход которого соединен с выходом генератора импульсов, выходы регистров памяти соединены с соответствующими входами блоков вз-вешенного суммирования.

Источники информации, принятые во вниман1;1е при зкспертизе

1.Архангельский С.В. Применение и синтез блоков взвешенного суммирования. Сб. тезисов Всесоюзного совещания по техническим средствам аналоговой и аналого-цифровой вычислительной техники. Кишинев Штиинца 1976, с. 36-39.

2.Рабинер Л.,Гоулд Б. Теория и применение цифровой обработки сигналов. М., Мир 1978, с. 598-599 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1979 |

|

SU822193A1 |

| Цифровой анализатор спектра | 1982 |

|

SU1149274A1 |

| Рекурсивный цифровой фильтр | 1990 |

|

SU1732433A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Цифровое устройство для сдвигаСпЕКТРА элЕКТРичЕСКиХ СигНАлОВ | 1979 |

|

SU842620A1 |

| Аналоговое устройство для определенияСпЕКТРАльНОй плОТНОСТи и ABTOKOP-РЕляциОННОй фуНКции СлучАйНОгОпРОцЕССА | 1979 |

|

SU813459A1 |

| Устройство для первичной обработки сейсмической информации | 1981 |

|

SU1057958A1 |

| Анализатор спектра Фурье | 1981 |

|

SU940170A1 |

| Устройство для анализа результата воспроизведения с носителя магнитной записи | 1990 |

|

SU1735905A1 |

Авторы

Даты

1981-02-15—Публикация

1978-08-08—Подача