(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧЕТЧИКА

тельноеть импульсных сигналов, в которой временной интервал между двумя соседними импульсами меняется в процессе поступления их на вход устройства. В этом случае устройство осуществляет контроль выхода счётной схемы только на время задержки входного сигнала элементом задержки, не контролируя при этом выход счетной схемы с момента ее срабатывания до. появления следующего входного импульса. Этот не контролируемый интервал времени может изменяться в значительных пределах. Следовательно предлагаемое устройство не обнаруживает ложные сигналы на выходе контролируемой счетной схемы на всем интервале времени между двумя соседними импульсами не1 авномерной входной последовательности сигналов.

Цель изобретения - повышение .разрешающей способности контроля счетных схем с прризвольНЕзМ законом поступления сигналов пересчета.

Поставленная цель достигается тем что в устройство содержащее первый и второй триггер, первый и второй элементы задержки, первый, второй и третий элементы И, первый инвертор и элемент ИЛИ, причем вход контролируемой схемы соединен со входом устройства, а выход - с первым входом первого элемента И, входами первого элемента задержки и первого инвертора, выход которого соединен с первым входом второго элемента И, второ вход которого соединен со вторым входом первого элемента И и выходом второго элемента задержки, выход которого соединен с нулевым входом первого триггера, единичный вход которого соединен с выходом элемента ИЛИ, входы которого соединены соответственно с выходами второго и третьего элементов И, первый и второй входы третьего элемента И соединены соответственно с выходами первого элемента задержки и второго триггера, выход первого триггера является выходом устройства, в которое введены второй инвертор и Третий элемент задержки, причем вход третьего элемента задержки соединен с нулевым входом второго триггера и входом устройства, а чыход - с входом второго элемента задержки и единичным входом второго триггера, вход второго инвертора соединен с выходом первого элемента И, а выход - с третьим входом третьего элемента И.

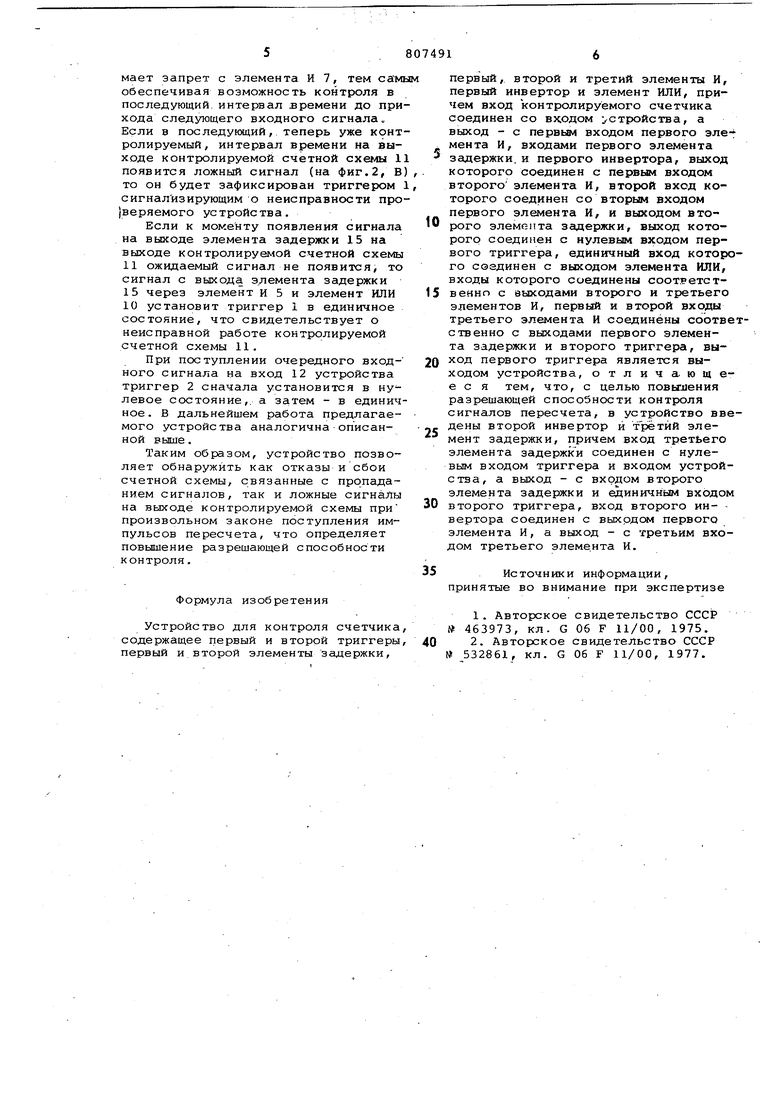

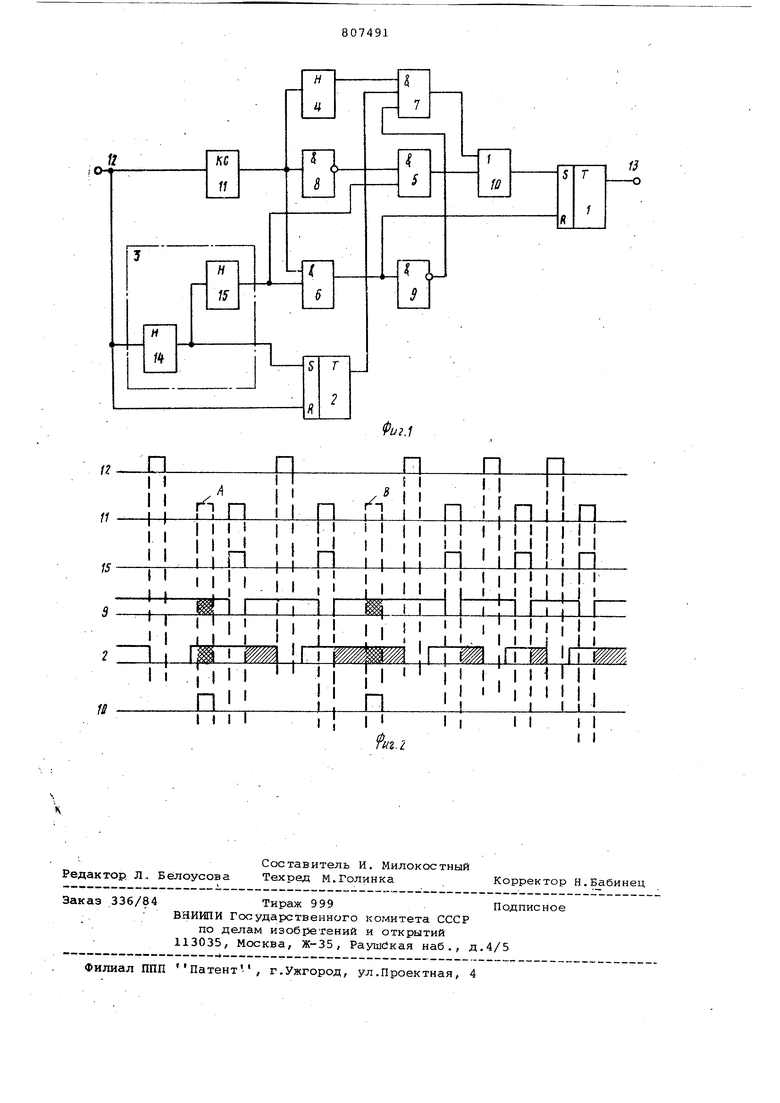

На фиг.1 представлена функциональная схема устройства; на фиг.2 временные диаграммы, поясняющие работу предлагаемого устройства.

Устройство содержит триггер 1 и 2, блок 3 задержек, элемент 4 заде{}жки, двухвхрдовые элементы И 5 и 6, трехвходовойэлемент И 7, инверторы 8 и 9, логический эле1у1ент ИЛИ 10, контролируемую счетную схему 11, вход 12 и выход 13 устройства

Блок задержек 3 содержит первый элемент 14 задержки и второй элемент 15 задержки.

Устройство работает следующим образом.

Каждый импульс входной импульсной последовательности поступает на вход {Контролируемой счетной схемы 11, на вход блока 3 задержек и устанавливает триггер 2 в нулевое состояние. Сигнал с выхода элемента 14, задержки, предназначенного для задержки входного сигнала на-время установки триггера 2 в нулевое состояние, устанавливает триггер 2 в единичное состояние и поступает на вход элемента 1 5 задержки. Время задержки элемента задержки 15 равно минимально1му периоду следования входной импульсной последовательности. Единичный потенциал с выхода триггера 2 поступает на второй вход элемента И 7. До тех пор, пока на входах элемента И б не совпадут сигналы с выхода элемента 15 задержки и выхода контролируемЪй счетной схемы 11, на его выходе будет присутствовать нулевой потенциал, который поступает на вход инвертора 9, с выхода которого единичный потенциал поступает на третий вход элемента И 7. Такш-л образом элемент И 7 открыт по второму и третьему входу и если в интервале времени, на который настроен элемент задержки 15, на выходе контролируемой счетной схемы 11 появится ложный сигнал (на фиг.2, А), то он,пройдя через элемент задержки 4, элемент И 7 и элемент ИЛИ 10, переключит триггер 1 в единичное состоян сигнализирующее о наличии ошибки в контролируемой счетной схеме 11. Элемент задержки 4 предотвращает ложное срабатывание триггера 1, которое возможно из-за задержки срабатывания триггера 2 и совпадения в этом случае сигналов на входах схемы И 7 при правильной работе контролируемой счетной схемы 11. Через определенное время на выходе контролируемой счетной схемы 11 должен появиться сигнал, который поступает на второй вход элемента И б, на первый вход которого поступает сигнал с выхода элемента задержки 15. При совпадении этих сигналов на входах элемента И 6, на его выходе появляется сигнал, подтверждающий нулевое состояние триггера 1 и через инвертор 9 запрещающий прохождение сигнала с выхода контролируемой счетной схемы 11 на выход схемы И 7 (см.фиг.2) .

По окончанию сигнала на выходеконтролируемой счетной схемы 11 на выходе инвертора 9 опять появляется единичный сигнал, который снимает запрет с элемента И 7, тем обеспечивая возможность контроля в последующий, интервал времени до при хода следующего входного сигнала« Если в последующий, теперь уже конт ролируемый, интервал времени на выходе контролируемой счетной схемы 1 появится ложный сигнал (на фиг.2, В то он будет зафиксирован триггером сигнализирующим о неисправности про {веряемого устройства. Если к моменту появления сигнала на выходе элемента задержки 15 на выходе кoнтpoлиpye oй счетной схемы 11 ожидаемый сигнал не появится, то сигнал с выхода элемента задержки 15 через элемент И 5 и элемент ИЛИ 10 установит триггер 1 в единичное состояние, что свидетельствует о неисправной работе контролируемой счетной схемы 11. При поступлении очередного входного сигнала на вход 12 устройства триггер 2 сначала установится в нулевое состояние,, а затем - в единич ное. В дальнейшем работа предлагаемого устройства аналогична описанной выше. Таким образом, устройство позволяет обнаружить как отказы и сбои счетной схемы, связанные с пропаданием сигналов, так и ложные сигналы на выходе контролируемой схемы при произвольном законе поступления импульсов пересчета, что определяет повышение разрешающей способности контроля. Формула изобретения Устройство для контроля счетчика содержащее первый и второй триггеры первый и второй элементы задержки. первый, второй и третий элементы И, первый инвертор и элемент ИЛИ, причем вход контролируемого счетчика соединен со входом стройства, а выход - с nepBbBvi входом первого эле- мента И, входами первого элемента задержки.и первого инвертора, выход которого соединен с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента И, и выходом второго элемента задержки, выход которого соединен с нулевым входом первого триггера, единичный вход которого соединен с выходом элемента ИЛИ, входы которого соединены соответственно с выходами второго и третьего элементов И, первый и второй входы третьего элемента И соединены соответственно с выходами первого элемента задержки и второго триггера, выход первого триггера является выходом устройства, отличающееся тем, что, с целью повыдения разрешающей способности контроля сигналов пересчета, в устройство введены второй инвертор и трётйй элемент задержки, причем вход третьего элемента задержки соединен с нулевым входом триггера и входом устройства, а выход - с входом второго элемента задержки и единичным входом второго триггера, вход второго ий- вертора соединен с выходом первого элемента И, а выход - с третьим входом третьего элеме.нта И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 463973, кл. G 06 F 11/00, 1975. 2.Авторское свидетельство СССР № 532861, кл. G 06 F 11/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределителя | 1982 |

|

SU1057960A1 |

| Устройство для контроля счетчика | 1980 |

|

SU884148A1 |

| Устройство для контроля дешифратора | 1980 |

|

SU918948A1 |

| Устройство для контроля последовательности импульсов | 1982 |

|

SU1064444A1 |

| Устройство для контроля -разряд-НОгО СчЕТчиКА | 1979 |

|

SU839060A1 |

| Селектор импульсов по длительности | 1980 |

|

SU917331A2 |

| Пересчетное устройство | 1976 |

|

SU702526A1 |

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Устройство для контроля последовательности импульсов | 1981 |

|

SU957425A1 |

| Устройство для контроля работы @ -разрядного счетчика | 1982 |

|

SU1167727A1 |

Авторы

Даты

1981-02-23—Публикация

1978-05-03—Подача