(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифраторов | 1986 |

|

SU1339899A1 |

| Устройство для контроля дешифратора | 1982 |

|

SU1024923A1 |

| Устройство для контроля дешифраторов | 1985 |

|

SU1298924A1 |

| Устройство для контроля дешифратора | 1983 |

|

SU1149267A1 |

| Устройство для контроля дешифратора | 1979 |

|

SU811262A1 |

| Устройство для контроля цифровых объектов | 1982 |

|

SU1072048A1 |

| Устройство для контроля цифровых блоков | 1980 |

|

SU960826A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

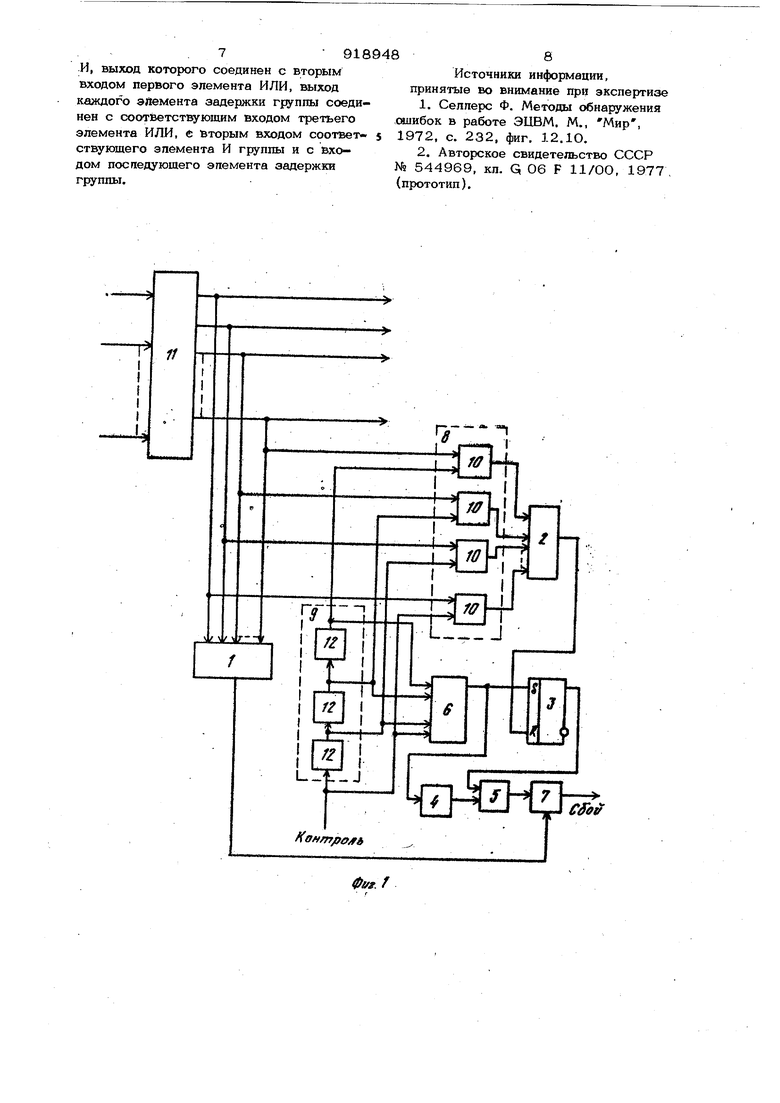

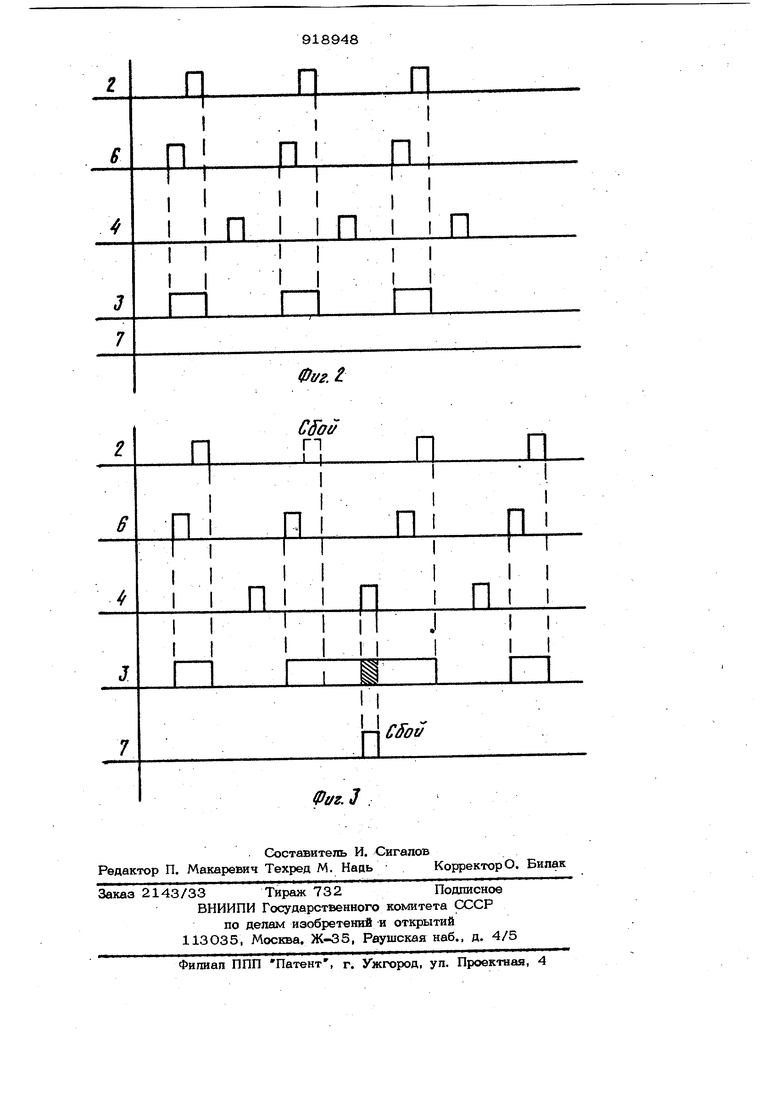

Изобретение относится к автоматике, I телемеханике и вычислительной технике и может быть использовано для контроля различных дешифраторов. Известно устройство для контроля де-. шифратора, содержащее дешифратор, многовходовую схему ИЛИ, схемы НЕ, И и схему нечетности Щ. Недостатком этого устройства является то, что оно не выявляет такие отказы в работе дешифратора, когда возбуждаются требуемая и нетребуемая шинь1, а также когда возбуждается нетребуемая шина. ..Наиболее близким по технической сущ ности к предлагаемому является устройство для контроля дешифратора, содержащее .блок аналогового суммирования, пороговые элементы, элемент ИЛИ 2. Известное устройство работает следующим образом. Для выявления отказа шифратора в одном пороговом элементе устанавливается порог срабатывания, рав ный нулю. С помошью этого порогового элемента выявляются отказы дешифратора, выражающиеся в отсутствии сигналов на его выходах при подаче на входы определенной кодовой комбинации. В другом пороговом элементе устанавливается порог срабатывания, превышающий номинагоь х нов значение выходного потенциала дешифратора. Таким образом, этот порого-. вый элемент способствует выявлению таких отказов дешифратора, когда на двух и более выходах: дешифратора одновремен-. но появляются сигналы. Однако известное устройство не конч ролирует соответствие выходного сигнала кодовой комбинации. Поэтому указанное устройство не фиксирует отказы дешифратора в случае, когда на его выходе возбуждается нетребуемая шина. Цель изобретения - повышение разрешающей способности контроля. Поставленная цель достигается тем, что в устройство для контроля дешифратора содержащее пороговый элемент и первый элемент ИЛИ, выход которого явпяется первым выходом устройства, выходы контролируемого дешифратора соеди нены со входами порогового элемента и являются группой входов устройства, выход порогового элемента соединен с первым входом первого элемента ИЛИ, введены второй и третий элементы ИЛИ группа элементов И,группа элементов задержки, элемент задержки, триггер и элемент И, причем каждый выход контро лируемого дешифратора соединен с первым входом соответствующего эпемента И группы, выход каждого элемента И группы соединен с соответствующим входом второго элемента ИЛИ, выход которого соединен с нулевым установочным входом триггера, управляющий вход уса ройства соединен со входом первого элемента задержки группы, со вторым входом первого элемента И группы, с первым входом третьего элемента ИЛИ, выход которого соединен с единичным уста новочным входом триггера и со входом элемента задержки, единичный выход три гера соединен с первым входом эпемента И, выход элемента задержки соединен со вторым входом элемента И, выход крторого соединен со вторым входом первого элемента ИЛИ, выход каждого элемента задержки группы соединен с соответствующим входом третьего элемента ИЛИ, со вторым входом соответствующего элемента И группы и со входом последую шего элемента задержки группы. На фиг. 1 приведена функциональная схема устройства для контроля дешифратора; на фиг. 2 и 3 - временные диаграммы работы дешифратора, Предлагаемое устройство содержит пороговый элемент 1, элемент ИЛИ 2, триггер 3, элемент 4 задержки, элемент И 5, элементы ИЛИ 6 и 7, группу элементов И 8, группу элементов 9 задержек, каждый -1 выход которого соединен с первым входом i +1 элемента И 1О (i 1, 2, ..., п ) группы элементов И В, к другим входам которого подвключены соответствующие выходы контро лируемого дешифратора 11, объединенные со входами порогового элемента 1. Группа элементов 9 задержки содержит (п-1) элемента 12 задержки, Выход элемента ИЛИ 2 соединен с ну левым управляющим входом триггера 3, выход которого соединен с первым входом элемента И 5, второй вход которого соединен через элемент 4 задержки с единичным управляющим входом триггера 3 И С выходом элемента ИЛИ 6, входы которого, кроме первого, соответственно соединены с выходами группы элементов 9 задержки, а первый вход элемента ИЛИ 6 соединен с управляющим входом устрюйства и со входом группы элементов 9 задержки и первым входом элемента И 10 группы элементов И 8, выходы которого соединены со входами элемента ИЛИ 2. Выход -элемента И 5 соединен с первым входом элемента ИЛИ 7, вторюй вход которого соединен с выходом порогового элемента 1, причем выход элемента ИЛИ 7 является выходом устройства, Устройство работает следующим образом. В исходном состоянии триггер 3 устанавливается в нулевое состояние (низкий потенциал на прямом выходе). Цепи установки не указаны, В режиме Контропь кодовые комбинации на вход дешифратора 11 подаются с произвольной частотой (период Т), Последовательность кодовых комбинаций выбирается так, что на выходах дешифратора 11 появляются сигналы в заранее заданной последовательности (например, в порядке возрастания, с 1-го по п-й). Время задержки -fc сигнала каждым элементом 12 задержки группа элементов 9 задержки равно периоду Т смены кодовых комбинаций на входе дешифратора 11, поэтому появление сигнала на выходе любого элемента 12 задержки группы элементов 9 задержки совпадает с появлением сигнала на соответствующем ему выходе дешифратора 11. Время задержки t эпемента 4 задержки равно J-. На временных диаграммах (фиг, 2 и 3) указаны сигналы на выходах соответствующих блоков. Одновременно с подачей на входы дешифратора 11 первой кодовой комбинации на вход первого эпемента 12 задержки по управляющему входу устройства подается импупьс, который через элемент ИЛИ 6 устанавливает триггер 3 в единичное состояние и одновременно задерживается на время -г- элементом 4 задержки. Кроме того, этот же импульс опрашивает первый выход дешифратора 11 на первом элементе И 10 группы элементов И 8. Если же в этот момент на первом выходе дешифратора 11 присутствует сигнал, то, пройдя через первый элемент И 10, он появится на выходе эпемента ИЛИ 2 и задним фронтом 591 возвратит триггер 3 в исходное состояние (фиг. 2). Через время, равное периоду Т смены кодовых комбинаций, на входы дешиф ратора 11 поступит вторая кодовая ком- бинация, в результате воздействия которой на втором выходе децгафратора 11 должен появиться сигнал. В это же время на выходе первого элемента 12 задержки также появляется опросный си нал, который через, элемент ИЛИ 6 внов устанавливает триггер 3 в единичное со стояние и одновременно задерживается на 4- элементом 4 задержки. В результате совпадения опросного сигнала с выхода первого элемента 12 задержки, с сигналом, который появился на втором выходе дешифратора 11, на выходе второго элемента И 10 появляется сигнал, который, пройдя через элемент ИЛИ 2,. задним фронтом возвратит триггер 3 в исходное состояние (фиг. 2). Если дешифратор 11 исправен, т.е. сигнал на выходе дешифратора 11 соответствует входной кодовой комбинации, то в дальнейшем устройство для контроля дешифратора 11 будет работать аналогично описаннок(у выше (фиг. 2). I. При возникновении различных видов неисправностей в дешифраторе 11 (например, когда при наличии входной ко.довой комбинации не возбуждается ни одна выходная шина или когда возбуждается нетребуемая шина, т.е. случай несоответствия выходного си.гнала входной кодовой комбинации) импульсы с его вы ходов и выходов элементов 12 задержки не будут совпадать на соответствую- ших элементах И 10, поэтому триггер 3 не возвратится в исходное состояние. В этом случае на входах элемента И 5 совпадает сигнал с выхода триггера 3 с сигналом, который появляется на вы ходе элемента 4 задержки с периодом Т (фиг. 3). На выходе элемента И 5 появится сигнал, который, пройдя через элемент ИЛИ 7, сигнализирует о сбое в работе дешифратора 11 (фиг. 3). В случае, когда на выходе дешифра; тора 11 вместе с требуемой шиной возбуждается нетребуемая, на выходе порогового элемента 1, настроенного на по рог срабатывания, превышающий номинальное значение выходного потенциала, появляется сигнал сбоя, который проходит через элемент ИЛИ 7 на выход устройства. Таким образом, предлагаемая совокупность признаков позволяет контрюпировать соответствие выходного сигнала дешифратора входной кодовой комбинации. Кроме того, как видно из изложенного, предлагаемое устройство выявляет все виды отказов и сбоев в контролируемом дешифраторе. Технико-экономический эффект предлагаемого устройства заключается в том, что в процессе профилактических работ представляется возможным автоматически выяв:шть все виды отказов и сбоев в работе дешифратора, что сушественно повышает достоверность контроля системы в целом. Особая актуальность проблемы повышения достоверности контроля приобретается в процессе эксплуатации ,, устройств автоматики, телемеханики и вычислительной техники, так как несвоевременно обнаруженный дефект в составляющих их устройствах, в том числе и в дешифраторах в процессе эксплуатации может привести к нежелательным последствиям для всей системы в целом. 1 Формула изобретения Устройство для контроля дешифратора, содержащее пороговый элемент и первый элемент ИЛИ, выход которого является первым выходом устройства, выходы контролируемого дешифратора соединены с входами порогового элемента, а выход порогового элемента соединен-с первым Входом первого элемента ИЛИ, отличающееся тем, что, с целью повышения разрешающей способности контроля, в него введены второй и третий элементы ИЛИ, группа элементов И; группа элементов задержки, элемент задержки, триггер и элемент И, причем каждый кыход контролируемого дешифратора соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен с соответствующим входом второго элемента ИЛИ, выход которого соединен с нулевым -установочным входом триггера, управляк ший вход устройства соединен с входом первого элемента задержки группы, с Вторым входом первого элемента И группы, с первым входом третьего элемента ИЛИ, выход которого соединен с единичным установочным входом триггера и с входом элемента задержки, единичный выход триггера соединен с первым входом элемента И, выход элемента задерж- ки соединен с вторым входом элемента

И, выход которого соединен с вторым входом первого элемента ИЛИ, выход каждого айемента задержки группы соединен с соответствуюшим входом третьего элемента ИЛИ, е вторым входом соответствующего элемента И группы и с входом поспедуюшего элемента задержки группы.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР № 544969, кп. Q 06 F 11/ОО, 1977 , (прототип).

Авторы

Даты

1982-04-07—Публикация

1980-08-15—Подача