(54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутирующее устройство последовательного действия | 1982 |

|

SU1081668A1 |

| Релейное коммутирующее устройство | 1974 |

|

SU843278A1 |

| Коммутирующее устройство | 1974 |

|

SU729853A1 |

| Устройство для включения исполнительного электромагнитного механизма | 1983 |

|

SU1141470A1 |

| Переключающее устройство | 1987 |

|

SU1499521A1 |

| Ячейка памяти для регистра сдвига | 1986 |

|

SU1424057A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU268494A1 |

| Регистр сдвига | 1981 |

|

SU1048518A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2013861C1 |

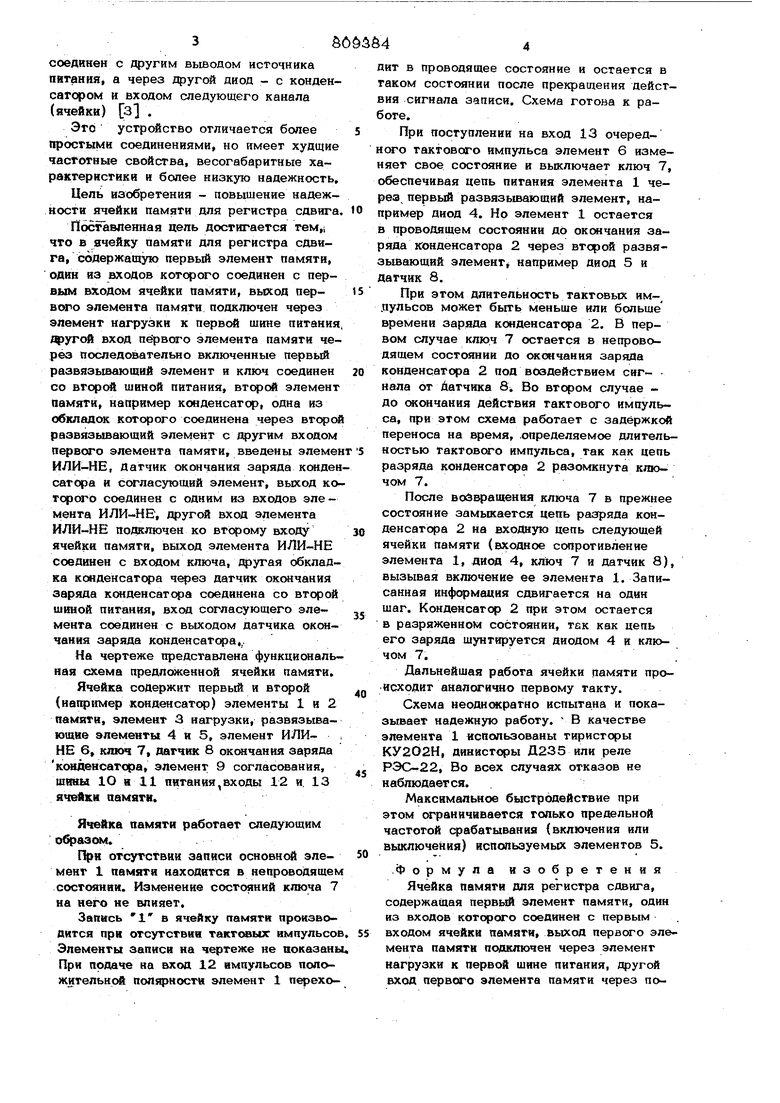

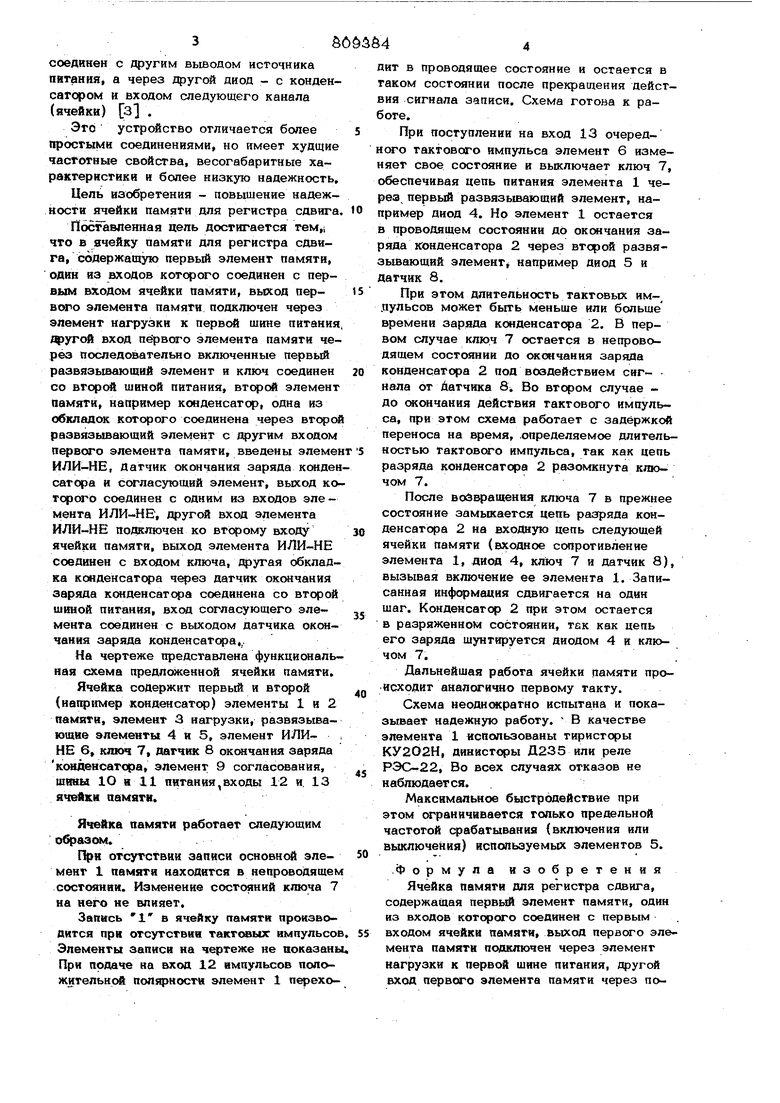

Изобретение относится к автоматике. Вычислительной -технике и программному управлению и может быть использовано в устройствах автоматизации и ксштроля производственных .прс«ессов в системах телемеханики и связей в качестве распределителя, счетчика, коммутатора, регистра сдвига, шифратора или дешифратора и т.п. Известны схемы коммутирующих устройств последовательного действия с задержкой переноса, каждый канал (разряд, ячейка) которых содержит основной запоминающий элемент, например реле, динистор, тиристор, тиратрон... и т.п., вспомогательный замыкающий элемент, например конденсатор и развязьтаюшие диоды, причем в общую цепь питания основных запоминающих элементов и общую цепь переноса, например разряда всех конденсаторов, включен размыкающий контакт или ключ управления tl и t2 . Достоинством таких схем является возможность работы без перекрытия и с задержкой переноса, возможность использования обоих состояний коммутирующих элементов для управления коммутируюемыми нагрузками. Тиристфные варианты таких схем по сравнению со схемами, использующими коммутирующие конденсаторы, имеют меньшие весогабаритные характеристики, лучшие частотные свойства и большую помехозащищенность, особенно от внутренних помех. Недостаток известных схем сложность схемных решений и зависимость структуры ячеек от выбрра коммутирующего элемента. Наиболее близким к предлагаемому является устройство последовательного действия, каждый канал (ячейка) которого содержит динистор, конденсатор н развязывающие диоды, причем один из выводов диннстора соединен через нагрузку с одним из выводов источника питания. Другой вьюод динистора через один из развязьюаюших диодов и ключ угфавления соединен с щэугнм выводом нсгочника питания, а через другой диод - с конденcarqJOM и входом следующего канала (ячейки) з . Это устройство отличается более простыми соединениями, но имеет худщие частотные свойства, весогабаритные характеристики и более низкую надежность. Цепь изобретения - повышение надежности ячейки памяти для регистра сдвига Поставяенная цель достигается тем,; что в ячейку памяти для регистра сдвига, с6|Держа1цую первый элемент памяти, один из входов которого соединен с первым входом ячейки памяти, выход первого элемента памяти подключен через элемент нагрузки к первой шине питания яругой вход первого элемента памяти через последовательно включенные первый развязывающий элемент и ключ соединен со вторсЛ шиной питания, второй элемент памяти, например конденсатор, одна из обкладок которого соединена через развязывающий элемент с щэугим входом первого элемента памяти, введены элеме ИЛИ-НЕ, Датчик окончания заряда конден сатора и согласующий элемент, выход ко соединен с одним из входов элемента ИЛИ-НВ, другой вход элемента ИЛИ-НЕ подключен ко второму входу ячейки памяти, выход элемента ИЛИ-НЕ соединен с входом ключа, другая обкладка конденсатора через датчик окончания заряда конденсатора соединена со второй шиной питания, вхсд согласующего элемента соединен с выходом датчика окончания заряда конденсатфа... На чертеже представлена функциональная схема предложенной ячейки памяти. Ячейка содержит первый и второй (например конденсатор) элементы 1 и 2 памяти, элемент 3 нагрузки, развязывающие элементы 4 и 5, элемент ИЛИНЕ 6 ключ 7, датчик 8 окончания заряда конденсатора, элемент 9 согласования. шины 1О и 11 питания,входы 12 и. 13 ячейки памяти. Ячейка памяти работает следующим образом.. При отсутствии записи основной элемент 1 памяти находится в непроводящем состоянии. Изменение состояний ключа 7 на него не влияет. Запись в ячейку памяти производится при отсутствии тактовых импульсо Элементы записи на чертеже не показаны При подаче на вход 12 импульсов полоЖительнсЛ полярности элемент 1 перехоит в проводящее состояние и остается в аком состоянии после прекращения дейстия сигнала записи. Схема готова к раоте. При поступлении на вход 13 очередого тактового импульса элемент 6 измеяет свое состояние и выключает ключ 7, беспечивая цепь питания элемента 1 чеез первый развязывающий элемент, наример диод 4. Но элемент 1 остается проводящем состоянии до окончания заяда конденсатора 2 через второй развяьюающий элемент например диод 5 и атчик 8, При этом длительность тактовых им- .пульсов может быть меньше или больше времени заряда конденсатора 2. В первом случае ключ 7 остается в непроводящем состоянии до окончания заряда конденсатора 2 под воздействием сиг- нала от Датчика 8 Во втором случае До сжончания действия тактового импульса, при этом схема работает с задержкой переноса на время, .определяемое длительностью тактового импульса, так как цепь разряда конденсатора 2 разомкнута ключом 7. После воЗщ)ащения ключа 7 в прежнее состояние замьиается цепь разряда конденсатора 2 на входную цепь следующей ячейки памяти (входное сопротивление элемента 1, диод 4, ключ 7 и датчик 8), вызывая включение ее элемента 1. Записанная информация сдвигается на один шаг. Конденсатор 2 при этом остается в разряженном состоянии, так как цепь его заряда шунтируется диодом 4 и ключом 7. Дальнейшая работа ячейки памяти происходит аналогично первому такту. Схема неоднсжратно испытана и показывает надежную работу. - В качестве элемента 1 использованы тиристоры КУ2О2Н, динистсчэы Д235 или реле РЭС-22, Во всех случаях отказов не наблюдается. Максимальное быстродействие при этом смграничивается только предельной частотой срабатывания (включения или выключения) используемых элементов 5. Формула изобретения Ячейка памяти для регистра сдвига, содержащая первый элемент памяти, один из входов которсяго соединен с первым входом ячейки памяти, выход первого элемента памяти подключен через элемент нагрузки к первой шине питания, другой вход первого элемента памяти через последовательно включенные первый развяэьюающий элемент и ключ соединен со второй шиной питания, второй элемент па мяти, например конденсатор, одна из об-, кладок которого соединена через второй развязывающий элемент с другим входом первого элемента памяти, о т л и ч а ю- щ а я с я тем, что, с целью повышения надежности ячейки памяти, в нее введены элемент ИЛИ-НЕ, датчик окончания заряда конденсатора и согласующий элемент, выход которого соединен с одним из входов элемента ИЛИ-НЕ, другсЛ вход .элемента ИЛИ-НЕ подключен ко второму входу ячейки памяти, выход элемента ИЛИ-НЕ соединен со входом ключа, друS46гая обкладка конденсатора через датчик окончания заряда конденсатора соедвнена со второй шиной питания, вход согласующего элемента соединен с выходом датчика окончания заряда ксяденсатора. Источники информедии, принятые во внимание при экспергвзе , 1. Авторское .свидетельство СССР № 284i03, кл. И 03 К 23/ОЗ, 1970, 2.Авторское свидетельство СССР № 44517О, кл. Н O3L 13/12, 1974. 3.Ауэн Л. Ф. Бесконтактные переключатели и пересчетные схемы на тирвсгорах Л., Энергия, 1968, с. 67, рвс.54 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-05-23—Подача