1

Изобретение относится к вычиспигельной технике и может быть использовано при построении помехозащищенных аналоговых и аналого-цифровых систем.

Известно аналоговое запоминающее устройство, обеспечивающее запоминание информационного сигнала при воздействии помех l .

Однако с о характеризуется недостаточно высокой помехоустойчивостью и низкой точностью.

Известно также аналоговое запоминающее устройство, обладающее высокой точностью 2. Однако оно не является помехоустойчивым.

Наиболее близким к предлагаемому является устройство, которое содержит основной усилитель, дополнительный усилитель, подключенный инвертирующим входом через резистор к выходу основного усилителя, а выходом - через резистс э к инвертирующему входу дополнительного усилителя и через ключ к неинвергирующему входу дополнительного усилигеля

И инвертирующему входу основного усилителя, подключенного неинвертирующим входом через ключ к источнику входных сигналов.

В режиме выборки замкнуты ключи, подключающие неинвертирующий вход основного усилителя к источнику входных сигналов, и его выход к конденсатору памяти. Ключ, соединяющий не инвертирующий вход основного усилителя с выходом дополнитеяьнсяо, разомкнут. Конденсатор памяти заряжается до напряжения, соответствующего входному. При переходе в режим хранения состояние всех ключей изменяется на противоположное, и на выходе устройства воспроизводится мгновенное значение напряжения, присутствовавшего на входе в момент переключения ключей ГЬ..

В режиме выборки входной сигнал подается на вход основного усилителя, включенного по неинвертирующей схеме. Вход устройсгва несимметричен и чувствителен

к наведенным помехам. Напряжение помехи фиксируется на конденсатсре памяти и присутствует на выходе устройства в режиме хранения. Это не позволяет в полней мере использовать вьюокие метрологические свойства схемы, в особенности при работе со входными сигналами низкого уровня.

Цель изобретения - повышение помехрустойчивости устройства.

Поставленная цель достигается.тем, что в аналоговое запоминающее устройство, содержащее основной усилитель, первый неинвертирующий вход котсрого соединен первый ключ с одним из входов устройства и через втароЛ ключ с выходом устройства и выходом дополни тельного усилителя, неинвертирующий вход дополнительного усилителя соединен с накопительным элементом, например, с одной из обкладсж конденсатора и первым инвертирующим входом основного усилителя, другая обкладка конденсатора соединена с шиной нулевого потенциала, выход основного усилителя через третий ключ соединен с неинвертирующим входом дополнительного усилителя, инвертирующий вход котсрого подключен через пассивный элемент к выходу основного усилителя, введены четвертый и пятый ключи причем инвертирующий вход основного усилителя через четвертый ключ соединен с другим входом устройства и через пятый ключ - с шиной нулевого потенциала и вторым неинвертирующим входом основного усилителя.

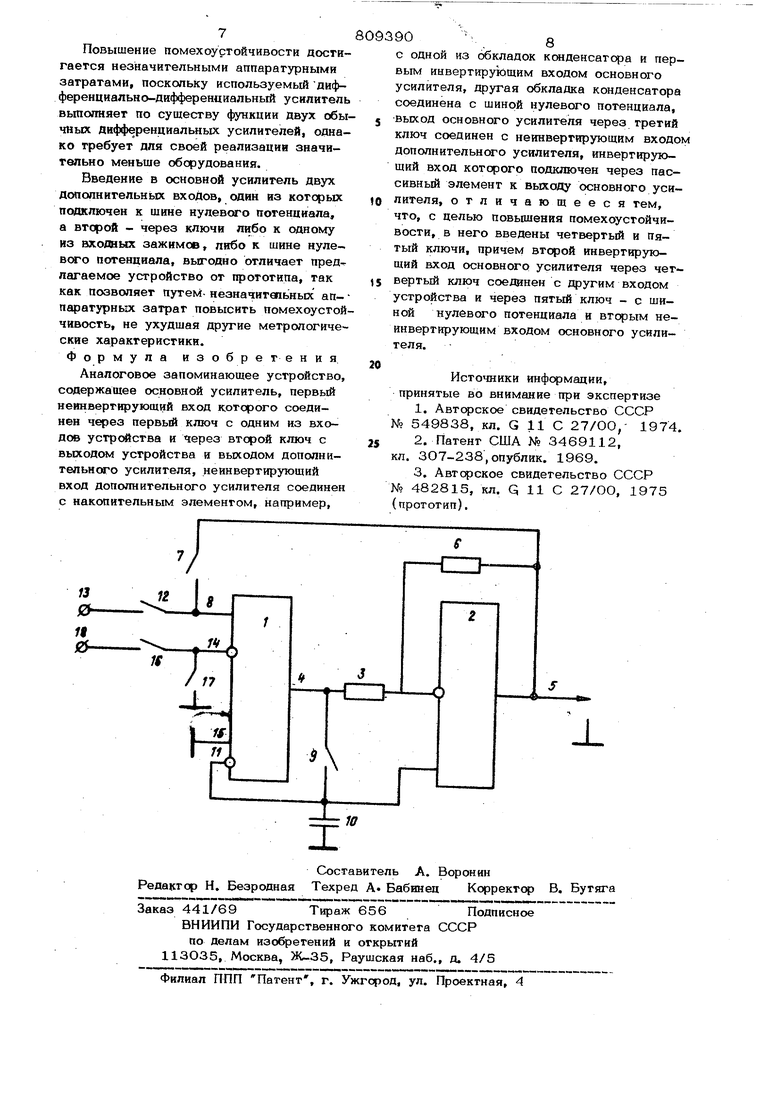

На чертеже представлена функциональная схема аналогового запоминающего устройства.

Устройство содержит основной усилитель 1, дополнительньй усилитель 2, подключенньй инвертирующим входом через .пассивный элемент, например резистор 3, к выходу 4 основного усилителя 1, а выходом 5 через пассивный элемен например резистор 6, - к инвертирующем входу дополнительного силителя 2 и через ключ 7 - к первому неинтервирующе му входу 8 основного усилителя 1, выход 4 которого через ключ 9 -подключен к накопительному элементу, например кoндeнcaтqэy 10, неинвертирующему входу дополнительного усилителя. 2 и первому инвертирующему входу 11 основного усилителя 1, подключенного первым неинвертирующим входом 8 через ключ 12 к первому входу устройства 13. Второй неинвертирующий вход 15 основного усилителя 1 подключен к шине нулевого

потенциала, а второй инвертирующий 14 через ключи 16 и 17 ко второму входу устройства 18 и к шине нулевого потенциала. Выходом устройства является выход 5 дополнительного усилителя 2.

Устройство работает в двух режимах.

В режиме выборки замкнуты ключи 9, 12 и 16 и разомкнуты 7 и 17. Входное дифференциальное напряжение, присутствующее между зажимами 13 и 18 подается на входы 8 и 14 основного усилителя. Основной усилитель, представляющий собой по конфигурации дифференциально-дифференциальный усилитель, при замкнутом ключе -9 охвачен отрицательной обратной связью и является повторителем напряжения на его выходе U относительно шины нулевого потенциала

U (и U ) 4 и

С-) l т Q-1Ч4lC - (

- 01 -, + к.

- входное дифференциальное

где и

вх

напряжение; К. - коэффициент усиления дифференциального :напряжения от входов 8 и 14 к выходу 4;

- коэффициент усиления дифференциального напряжения от входов 15 и 11 к выходу 4} %11%1 напряжения смещения нуля

основного усилителя по входам 8, 14 и 15, 11 соответственно с учетом синфазных ошибок в режиме выборки.

Конденсатор Ю, подключенный к выходу 4 основного усилителя 1, также заряжаеся в режиме до напряжения U . При переходе в режим хранения размыкаются ключи 12, 16 и 9 И замыкаются ключ 17, подключающий вход 14 основного усилителя 1 к шине нулевого потенциала , и ключ 7, замыкающий цепь общей обратной связи. Напряжение U запоминается на конденсаторе памяти 1О. В режиме хранения на выходе устройства присутствует постоянное напряжение

(Ui

(.tuj

()

- коэффициент передачи до(Ь полнительного усилителя 2 в инвертирующем включении, примерно равный отношению сопротивлени резисторов 6 и 3; напряжение смещения ну дополнительного усилите с учетом синфазных оши бок ; 01 oi напряжения смещения ну основного усилителя по входам 8, 14 и 15, 11 соответственно с учетом синфазных .ошибок в реж хранения. Поскольку напряжение между входами и 11 при переходе в режим хранения н изменяется, то U . Подставл (1) в значение и из после несложных преобразований получаем { К-« ,, J.,, j., i-i -V%:f вЫХ К, )(. и +u BX 011+рК, 01 i+fiK S + H,j - Oli+Kj|b 031+|ЬК 8Х(НК2)(7+П) К-, ICa.fi(ft+)K . aX-+liti) (1+К )(-ffpK. oi(i-,t)(i+(bS) Из (3)- следует, что UQ и Q , приведенные к выходу устройства , подавл ются при р, 1 (tga. - примерно в К. - в 4г . Далее их мо раз, а и но не учитывать. Коэффициенты при и L/o близки к 1. Формулу (3) можно упростить K:.itta.+ -.-(,} И) ВЫК (.)) Представляя oi и оч иде двух слагаемых %1 Ч;м+ синф Мм 6м + + Uj- viHcj) гдеи -напряжение смещения нуля основного усилителя 1 по входам 8 и 14, аисмнф -синфазные ошибки основного усилителя по входам 8 и 14 в режиме выборки и в режиме хранения, соответственно запишем .вх.с., 01 Ol синфазное напряжение на входных зажимах 13 и 1в в режиме выборки; коэффициент ослабления син фазного сигнала, присутствующего на входах 8 и 14 основного усилителя 1. 906 В предлагаемом устройстве напряжения смещения нуля усилителей, а также синфазные напряжения на входах 15 я 11 основного усилителя и. на входах дополнительнсяо усилителя эффективно подавляются. Применение во вхооных каскадах усилителя полевых или ЛЮТ1-.транзисторов приводит к увеличению напряжения смещения нуля и его {фейфу. Как правилу это снижает точность устройства, в котором используется подобный усилитель; В предлагаемом устройстве возможно применение неподобранных пар полевых или МОП-транзисторов во входньрс каскадах основного 1 и дополнительного 2 усилителей практически без ухудшения точности, что позволяет максимально увеличить входное сопротивление усгрой. ства, уменьшить токи разряда конденсатора памяти 3 режиме хранения. Погрешность передачи входного дифференциального напряжения, как следует из (4), равна ,г.,-К, ,, Даже при относительно малых и К и большом разбросе их значений устройство обеспечивает высокую точность. Например, пусть k 90, , f 1. Тогда погрешность iS по формуле (6) равна 0,12%. Для сравнения отметим,что если бы дифференциально-дифференциальный усилитель использовался вне предлагаемого устройства в качестве повторителя, то погрешность при тех же условиях была бы равна jMJCi-Ki -100%Х1-1% (7) оотношения (3) и (6), полученные при асчете, показьшают, что предлагаемое стройство в целом не уступает протоипу по точности, однако значительно ревосходит его по помехоустойчивости. Предлагаемое устройство имеет симетричный вход и нечувствительно к поехам. Указанное преимущество особено ощутимо при работе с информационныи сигналами низкого уровня. Помеху на ходе устройства можно представить как екоторое синфазное напряжение, прилоенное к обоим входным зажимам. Стеень подавления, как следует из (5), опеделяется коэффициентом kQj, ф , знаение которого, например, для дифференцильно-дифференциального усилителя в инегральным исполнении и может составять 1О и более. В прототипе подавлеие помех практически отсутствует. Повышение помехоустойчивости достигается незначительными аппаратурными затратами, поскольку используемый дифференциально-дифференциальный усилитель вьгаопняет по существу функции двух обы чных дифференциальных усилителей, однако требует для своей реализации значительно меньше оборудования. Введение в основной усилитель двух дополнительней входов, один из которых подключен к шине нулевого потенциала, а второй - через ключи либо к одному из входных зажимов, либо к шине нулевого потенциала, выгодно отличает предлагаемое устройство от прототипа, так как позволяет путеМ- незначительных аппаратурньус затрат повысить помехоустой чивость, не ухудшая другие метрологиче ские характеристики. Формула изобретения Аналоговое запоминающее устройство содержащее основной усилитель, первый неинвертирующий вход которого соединен через первый ключ с одним из входов устройства и через второй ключ с выходом устройства и выходом дополнительного усилителя, неинвертируюший вход дополнительного усилителя соедине с накопительным элементом, например, 0 с одной из с кладок конденсатора и первым инвертирующим входом основного усилителя, другая обкладка конденсатора соединена с шиной нулевого потенциала, выход основного усилителя через третий ключ соединен с неннвертирующим входом дополнительного усилителя, инвертирующий вход которого подключен через пассивный элемент к выходу основного усилителя, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены четвертый и пятый ключи, причем второй инвертирующий вход основного усилителя через четвертый ключ соединен с другим входом устройства и через пятый ключ - с шиной нулевого потенциала и вторым неинвертирующим входом основного усилителя. Источники информации, принятые во внимание при экспертизе 1.Автсрское свидетельство СССР № 549838, кл. G 11 С 27/ОО,- 1974. 2.Патент США № 3469112, кл. ЗО7-238,опублик. 1969. 3.Авторское свидетельство СССР № 482815, кл. Q 11 С 27/ОО, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1983 |

|

SU1223307A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU966749A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU953671A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU936031A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881869A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU942155A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU894795A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU748511A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU938318A1 |

Авторы

Даты

1981-02-28—Публикация

1978-07-03—Подача