(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1989 |

|

SU1667047A1 |

| Устройство для сравнения чисел | 1984 |

|

SU1188729A2 |

| Устройство для сравнения чисел | 1987 |

|

SU1474637A2 |

| Устройство для сортировки и выборки информации | 1983 |

|

SU1087986A1 |

| Устройство для выбора упорядоченной последовательности данных | 1984 |

|

SU1218381A1 |

| Устройство для сортировки чисел | 1981 |

|

SU960800A1 |

| Устройство для выделения экстремального из @ @ -разрядных чисел | 1984 |

|

SU1179316A1 |

| Устройство для сортировки чисел | 1980 |

|

SU943707A1 |

| Устройство для упорядочивания @ чисел | 1986 |

|

SU1339548A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

I

Изобретение относится к автоматике и вычислительной технике и предназначено для сравнения двоичных чисел и выбора из них большого или меньшего, в зависимости от заданного режима работы.

Известно устройство-сравнения, содержашее регистры, элементы И и ИЛИ, предназначенные для сравнения п-разрядных чисел 1.

Недостатком известного устройства является то, что оно сравнивает числа и вырабатывает в качестве результата сравнения сигнал, характеризуюш,ий величину заданного числа, а также малые функциональные возможности, так как оно производит сравнение только двух чисел.

Наиболее близким к предлагаемому по технической сушности является устройство, содержашее генератор импульсов, счетчики, элементы И и ИЛИ, триггеры 2.

Однако устройство имеет малое быстродействие.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для сравнения чисел введены шифратор и п дешифраторов, входы которых соединены с информационными входами устройства, а каждый i выход -го дешифратора, где i 1,2,..., j 1,2,...п подключен к -ому входу i-ro элемента ИЛИ, выход каждого i-ro элемента ИЛИ соединен с i-ым входом узла анализа, управляющий вход которого подключен к управляющему входу устройства, каждый i-ый выход которого подключен к i-ому входу шифратора.

При этом узел анализа содержит элемент

НЕ и п ячеек сравнения, причем каждый i-ый вход узла анализа, где i 1,2,..., соединен с первым входом i-ой ячейки сравнения, управляющий вход узла анализа подключен ко второму входу первой ячейки сравнения и через элемент НЕ - к третьему входу 2-ой ячейки сравнения, первый выход каждой i-ой ячейки сравнения соединен с i-biM, выходом узла анализа, второй выход каждой i-ой ячейки сравнения подключен ко второму входу (i + 1)-ой ячейки

сравнения, третий выход каждой i-ой ячейки сравнения соединен с третьим входом (i-l)-oй ячейки сравнения.

Кроме того, каждая ячейка сравнения содержит элементы И, ИЛИ и НЕ, причем

первый вход ячейки соединен с первым входом первого элемента И и через элемент НЕ - с первыми входами второго и третьего элементов И, второй вход каждой ячейки сравнения подключен ко второму входу второго элемента И и к первому входу элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, выход которого подключен к первому выходу ячейки, третий вход ячейки сравнения соединен со вторы.ми входами элемента ИЛИ и третьего элемента И, выход которого соединен с третьим выходом ячейки сравнения, выход второго элемента И подключен ко второму выходу ячейки сравнения.

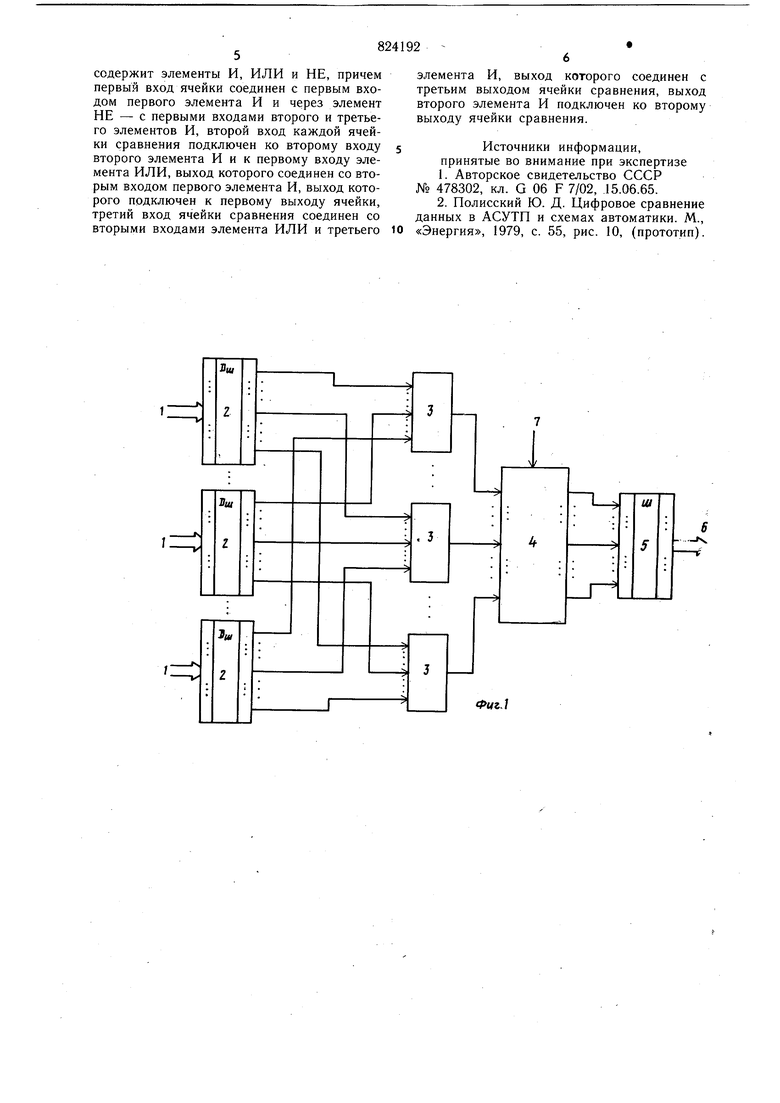

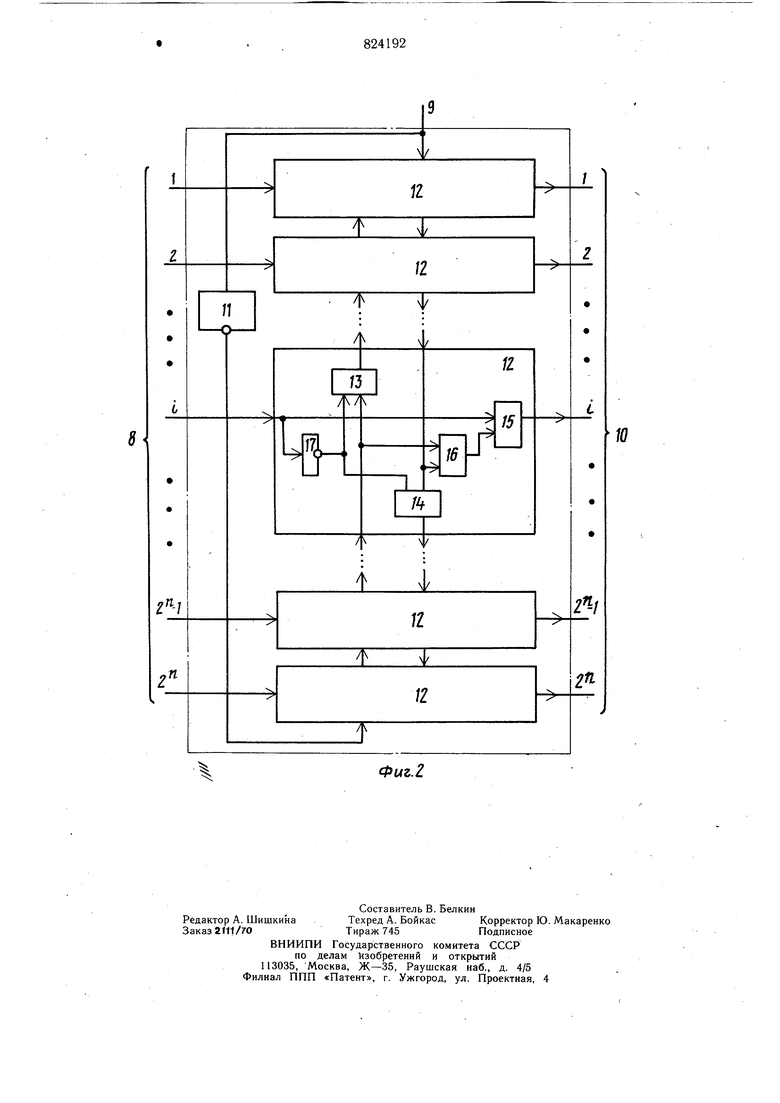

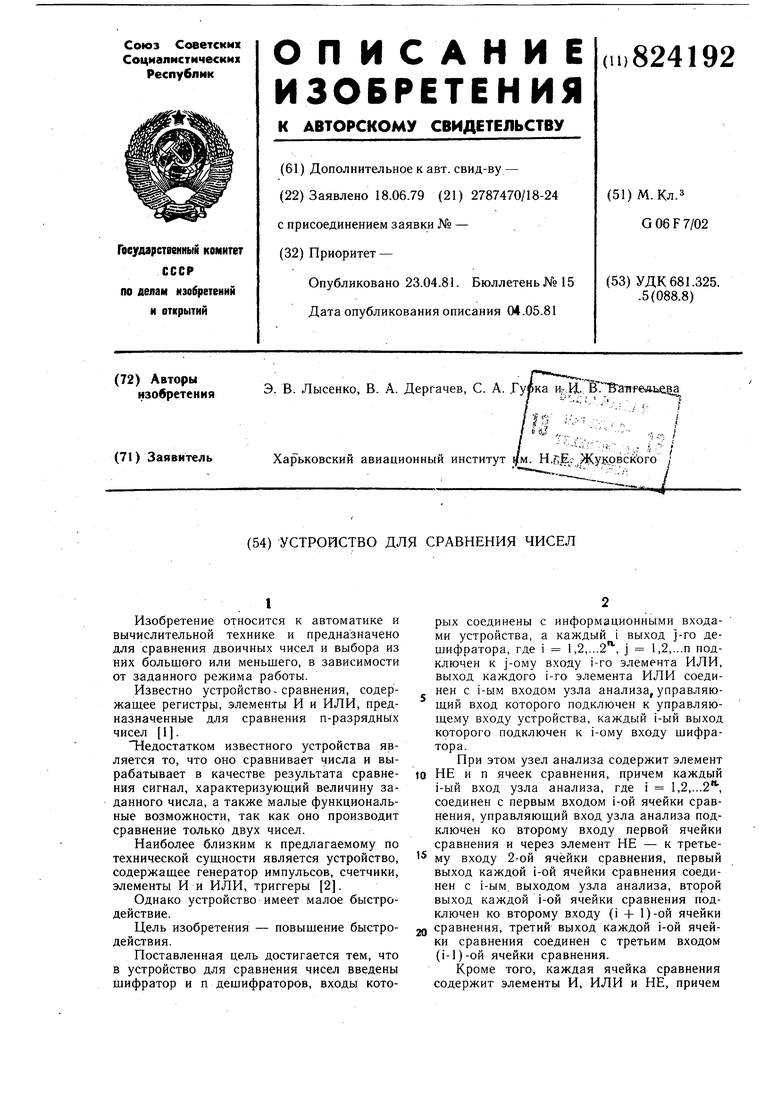

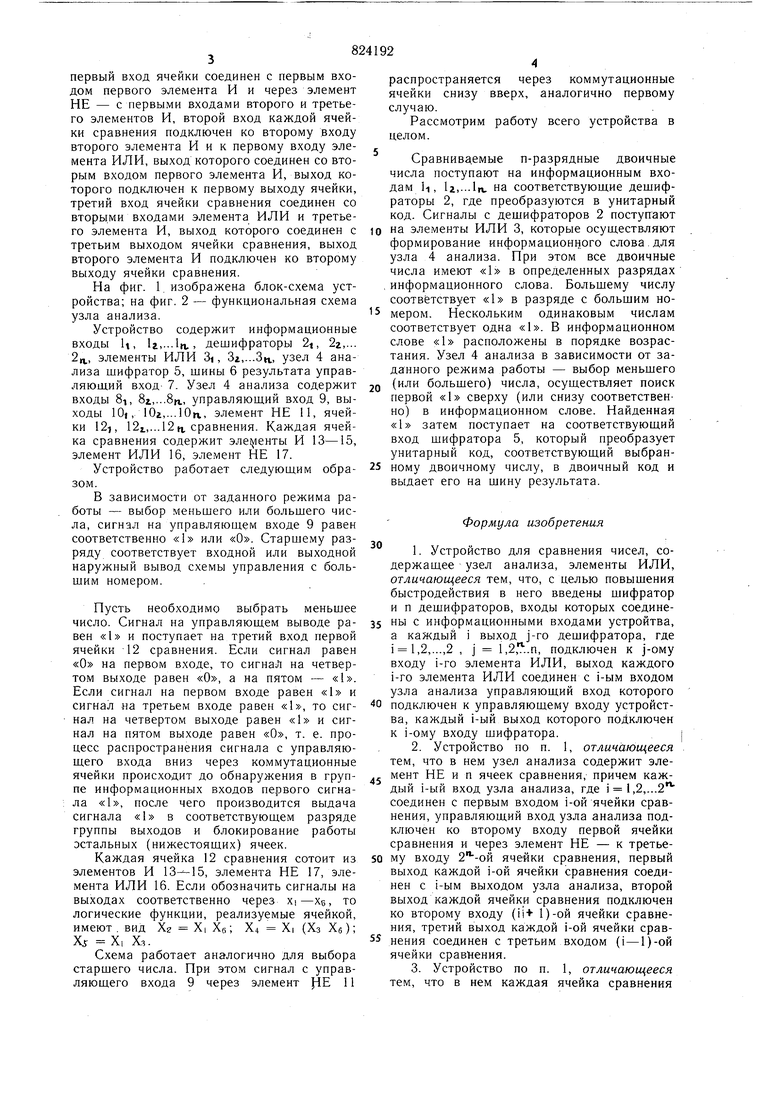

На фиг. 1, изображена блок-схема устройства; на фиг. 2 - функциональная схема узла анализа.

Устройство содержит информационные входы U, и,...In., дешифраторы 2,, 2г,... 2п., элементы ИЛИ 3i, Зг,...3ц., узел 4 анализа шифратор 5, шины 6 результата управляющий вход- 7. Узел 4 анализа содержит входы 8i, 8i,...8n., управляющий вход 9, выходы lOj, 10г,...10п., элемент НЕ 11, ячейки 12-1, 12i.,...12ц сравнения. Каждая ячейка сравнения содержит И 13-15, элемент ИЛИ 16, элемент НЕ 17.

Устройство работает следующим образом.

В зависимости от заданного режима работы - выбор меньшего или больщего числа, сигнал на управляющем входе 9 равен соответственно «1 или «О. Старшему разряду соответствует входной или выходной наружный вывод схемы управления с большим номером.

Пусть необходимо выбрать меньшее число. Сигнал на управляющем выводе равен «1 и поступает на третий вход первой ячейки 12 сравнения. Если сигнал равен «О на первом входе, то сигнал на четвертом выходе равен «О, а на пятом - «1. Если сигнал на первом входе равен «1 и сигнал «а третьем входе равен «1, то сигнал на четвертом выходе равен «1 и сигнал на пятом выходе равен «О, т. е. процесс распространения сигнала с управляющего входа вниз через коммутационные ячейки происходит до обнаружения в группе информационных входов первого сигнала «1, после чего производится выдача сигнала «1 в соответствующем разряде группы выходов и блокирование работы остальных (нижестоящих) ячеек.

Каждая ячейка 12 сравнения сотоит из элементов И , элемента НЕ 17, элемента ИЛИ 16. Если обозначить сигналы на выходах соответственно через Xi-хе, то логические функции, реализуемые ячейкой, имеют . вид Хг Xi Xg; Х4 Xi (Хз Хе); XjT Х| Хз.

Схема работает аналогично для выбора старшего числа. При этом сигнал с управляющего входа 9 через элемент liE 11

распространяется через коммутационные ячейки снизу вверх, аналогично первому случаю.

Рассмотрим работу всего устройства в целом.

Сравниваемые п-разрядные двоичные числа поступают на информационным входам li, l2, на соответствующие дешифраторы 2, где преобразуются в унитарный код. Сигналы с дешифраторов 2 поступают

на элементы ИЛИ 3, которые осуществляют формирование информационного слова.для узла 4 анализа. При этом все двоичные числа имеют «1 в определенных разрядах информационного слова. Больщему числу соответствует «1 в разряде с большим номером. Нескольким одинаковым числам соответствует одна «1. В информационном слове «1 расположены в порядке возрастания. Узел 4 анализа в зависимости от заданного режима работы - выбор меньщего

(или больщего) числа, осуществляет поиск первой «1 сверху (или снизу соответственно) в информационном слове. Найденная «1 затем поступает на соответствующий вход щифратора 5, который преобразует унитарный код, соответствующий выбранному двоичному числу, в двоичный код и выдает его на щину результата.

Формула изобретения

подключен к управляющему входу устройства, каждый i-ый выход которого подключен к i-ому входу шифратора.

содержит элементы И, ИЛИ и НЕ, причем первый вход ячейки соединен с первым входом первого элемента И и через элемент НЕ - с первыми входами второго и третьего элементов И, второй вход каждой ячейки сравнения подключен ко второму входу второго элемента И и к первому входу элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, выход которого подключен к первому выходу ячейки, третий вход ячейки сравнения соединен со вторыми входами элемента ИЛИ и третьего

Hut I

jffi

г

элемента И, выход которого соединен с третьим выходом ячейки сравнения, выход второго элемента И подключен ко второму выходу ячейки сравнения.

Источники информации, принятые во внимание при экспертизе

ta

. 3

8

Ю

Фиг. 2

Авторы

Даты

1981-04-23—Публикация

1979-06-18—Подача