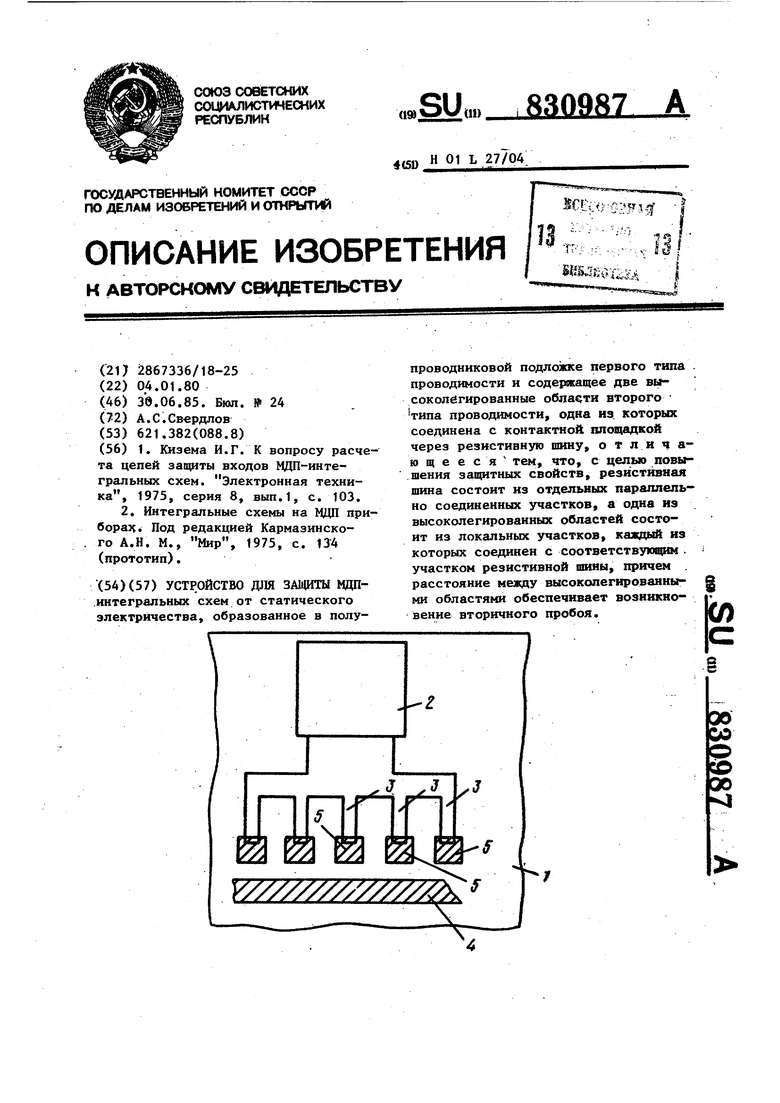

Изобретение относится к области электронной техники, а именно к уст ройствам для защиты ВДП-интегральных схем от статического электричества. Известно устройство для защиты МДП-интегральных схем от статического электричества Ш, содержащее полупроводниковую подложку, на которой размещены контактная площадка, первая и вторая диффузионные шины. Первая диффузионная шина сое динена непосредственно с контактной площадкой. Вторая диффузионная шина соединена с нулевой шиной или .подложкой. Расстояние между диффу.эионными шинами выбирается такой величины, чтобы сделать возможным .их смыкание. Когда напряжение на первой диффузионной шине достигает определенной величины, области про странственного заряда обеих диффузионных шин смыкаются, в результате чего между ними возникает ток. Недостатком такого устройства для защиты ВДП интегральных схем от статического электричества явля ется низкая устойчивость к воздействию статического заряда и большо последовательное сопротивление. Наиболее близким по технической сущности к изобретению является устройство для защиты ВДП-интеграл ных схем от статического электриче тва,, образованное в полупроводнико вой подложке первого типа проводимости и содержащее две высоколегированные области второго типа пр водимости, одна из которых средине на с контактной площадкой через ре зистивную шину |Y. . Однако такие устройства, включа мые между входом интегральной схемы и затворх м защищаемого транзист ра, в соединении с входной емкость этого транзистора, приводят к снижению быстродействия интегральной схемы. Кроме того, для улучшения характеристик защитного устройства необходимо уменьшать динамическое сопротивление выходного элемента, что может быть вьшолнено, главным образом, за счет увеличения площади устройства. Целью изобретения является повы шение заоситных свойств. Цель достигается тем, что в известном устройстве для защиты ЬЩП72интегральных схем от статического электричества, образованном в полупроводниковой подложке первого типа проводимости и содержащем две высоколегированные области второго типа проводимости, одна из которых соединена с контактной площадкой через резистивную шину, резистивная шина состоит из отдельных параллельно соединенных участков, а одна из высоколегированных областей состоит из локальных участков, каждый из- которых соединен с соответствующим участком резистивной шины, причем расстояние между высоколегированными областями обеспечивает возникновение -вторичного пробоя. Изобретение поясняется чертежом, где полупроводниковая подложка 1, например р-типа проводимости, контактная площадка 2, резистивная шина 3, высоколегированные области 4,5, например П -типа проводимости. Устройство работает следующим образом. При возникновении на участках области 5 напряжения (положительного для и-канального устройства) через переход этих участков начинает протекать обратный ток. При этом происходит разделение электронов и дырок. Дырки остаются в. участке .подложки 1 между областью А и локальными участками области 5, создавая дырочный ток, направленный . вглубь подложки 1 от rt -области. Возникающее на сопротивлении подложки 1 падение напряжения смещает в прямом направлении переход области 4, вызывая инжекцию элe cтpo- нов на области 4 в подложку 1. Эти инжектированные электроды, в свою очередьj способствуют усилению генерации электронно-дырочных пар, появлению дополнительнрго дьфочного тока и дополнительному смещению. перехода области 4. Существующая, таким образом, положительная обратная связь приводит при определенной величине напряжения к лавинообразному возрастанию тока (вторичному пробою) в перехода локального участка области 5. В этом режиме переход имеет близкое к нулевому динамическое сопротивление. .Напряжение вторичного пробоя эависит от расстояния между областью 4 и локальными участками области 5. с уменьшением расстояния это напря жение уменьшается. При превышении некоторой величины лавина не образ ется, и напряжение на р-п переходё определяется процессом обычного пробоя. В данном устройстве каждый локальный участок области 5 соединяется с контактной площадкой 5 одним из рези.стивных участков шИны 3 Вследствие этого входной ток распр деляется равномерно между участкам 5. Перегрузка одного какого-либо участка исключается/В результате максимальное значение входного ток которое может вьщержать без разрушения данное устройство повышаетс Таким образом, возрастает устойчивость устройства к воздействию статического заряда. Одновременно снижается динамическое сопротивление в режиме пробоя, поскольку сопротивление ряда 874 . . . параллельно включенных резистивных участков включено последовательно с почти нулевым сопротивлением локальных участков области 5, находящихся в состоянии вторичного пробоя. В данном устройстве вообще исключено последовательное сопротивление. В качестве такового при залете интегральных схем используется внутрен нее сопротивление источника статического заряда. Благодаря малому динамическому сопротивлению это приводит к высокой стецени ослабления выходного. н&пряжеиия ino отношению к напряжению источника заряда . Использование изобретения позволяет создавать устройства защиты в которых без .ухудшения степени ослабления выходного напряжения, удается исключить последовательное сопротивление ycтpoйctвa и одновременио увеличить его устойчивость к воздействию статического заряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА | 1990 |

|

RU1699313C |

| Микропиксельный лавинный фотодиод | 2021 |

|

RU2770147C1 |

| Способ изготовления вертикального низковольтного ограничителя напряжения | 2019 |

|

RU2698741C1 |

| Полупроводниковый лавинный детектор | 2023 |

|

RU2814514C1 |

| ЛАВИННЫЙ ФОТОДЕТЕКТОР | 1991 |

|

SU1823725A1 |

| МИКРОКАНАЛЬНЫЙ ЛАВИННЫЙ ФОТОДИОД | 2006 |

|

RU2316848C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ МОЩНЫХ ПОЛЕВЫХ LDMOS ТРАНЗИСТОРОВ | 2008 |

|

RU2364984C1 |

| МНОГОКАНАЛЬНЫЙ МАТРИЧНЫЙ СТАБИЛИТРОН С МАЛЫМ ТЕМПЕРАТУРНЫМ ДРЕЙФОМ | 2024 |

|

RU2839079C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КНС (КРЕМНИЙ НА САПФИРЕ), КНИ (КРЕМНИЙ НА ИЗОЛЯТОРЕ) СТРУКТУРАХ | 2011 |

|

RU2467431C1 |

УСТРОЙСТВО ДЗЮ ЗАЩИТЫ МДП- .интеграпьных схем от статического электричества, образованное в полупроводниковой подложке первого типа . проводимости и содержащее две высоколегированные области второго • 'типа проводимости, одна из которых соединена с контактной площадкой через резистивную щину, отличающееся' тем, что, с целью повышения защитных свойств, резйстйвяая шина состоит яз отдельных параллельно соединенных участков, а одна иэ высоколегированных областей состоит из локальных участков, каждый из которых соединен с соответствуюа(им . участком резистивной шины, причем . расстояние между высоколегированными областями обеспечивает возникновение вторичного пробоя.00со§00^Y7//////77///Z^ ^

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кизема И.Г | |||

| та цепей запщты входов МДП-инте- гральных схем | |||

| "Электронная техника", 1975, серия 8, вып.1, с | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| Интегральные схемы на ЩП приборах^ Под редакцией Кармазинско- го А.Н | |||

| М., "Мир", 1975, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

Авторы

Даты

1985-06-30—Публикация

1980-01-04—Подача