(54) УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического допускового контроля импульсов | 1982 |

|

SU1084988A1 |

| Устройство для допускового контроля | 1986 |

|

SU1406779A2 |

| Устройство контроля одиночного импульса | 1983 |

|

SU1157474A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| Устройство автоматического контроля монтажа с радиоэлементами | 1984 |

|

SU1190312A1 |

| Частотный компаратор | 1988 |

|

SU1555843A2 |

| Устройство для контроля амплитуды импульсной последовательности | 1985 |

|

SU1582142A1 |

| Устройство для контроля пружин | 1991 |

|

SU1809332A1 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1748240A1 |

I

Изобретение относится к радиоизмерительной технике и может быть использовано в устройствах контроля, в которых происходит определение соответствия, контролируемого периода и параметров импульсов заранее установленному полю допусков.

Известно устройство для допускового контроля временных интервалов между импульсами, содержащее блок дискретной задержки сигнала, инвертор, триггер и элемент совпадения 1.

Недостаток этого устройства - ограниченные возможности, не обеспечивающие возможности контроля, кроме периода, других параметров импульсной последовательности.

Известно также устройство для допускового контроля временных интервалов, содержащее инвертор, элементы совпадения, два триггера и элемент задержки 2.

Однако известное устройство также не позволяет контролировать одновременно период и все параметры импульсов.

Цель изобретения - расширение функциональных возможностей устройства -за счет обеспечения одновременного контроля периода следования, амплитуды и длительности импульсоа, длительности переднегй и заднего фронтов импульсов, а также амплитуды отрицательно1О выброса.

Указанная цель достигается тем, что в устройство допускового контроля, содержащее два триггера и элемент задержки, два выхода которого соединены со входами первого триггера,, дополнительно введены триггер, элемент ИЛИ и четыре компаратора, первые входы которых соединены со входом элемента задержки, два дополнительных выхода которого подключены к первому и второму входам второго триггера, третий вход которого соединен с третьим входом первого триггера, первым входом дополнительного триггера и вторыми входами компараторов, выходы которых через элемент ИЛИ подключены ко второму входу дополнительного триггера, а выходы первого и второго триггеров соединены с третьими входами первого и второго компараторов.

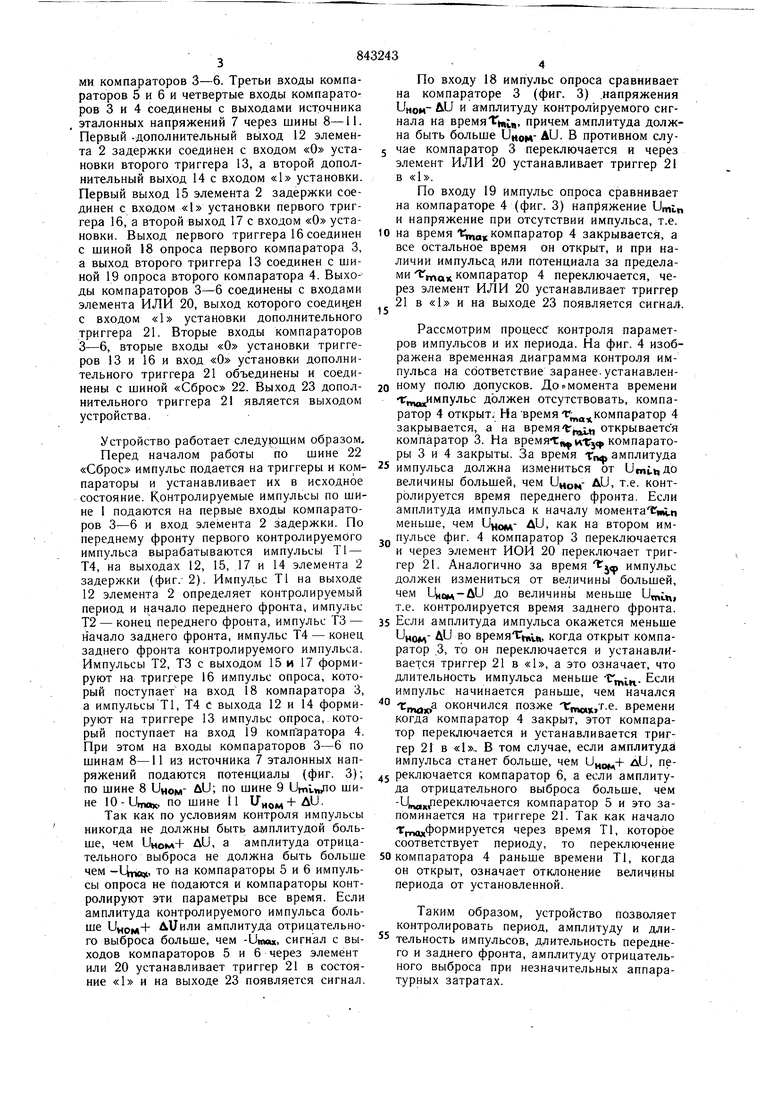

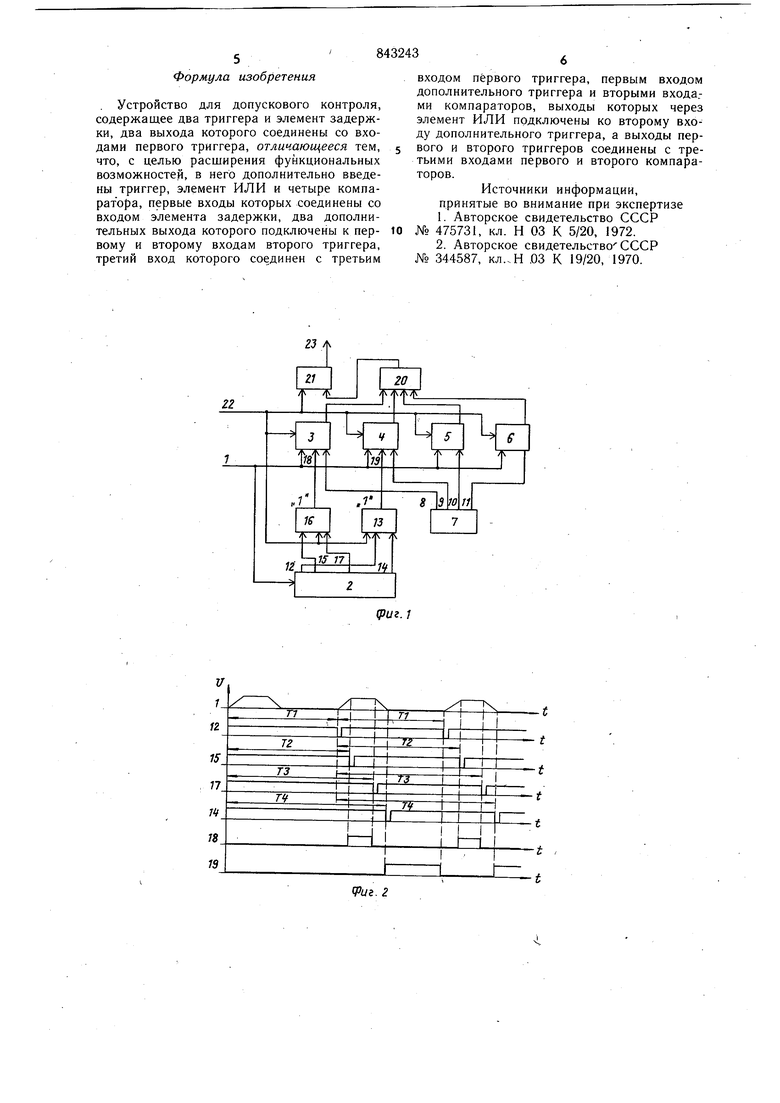

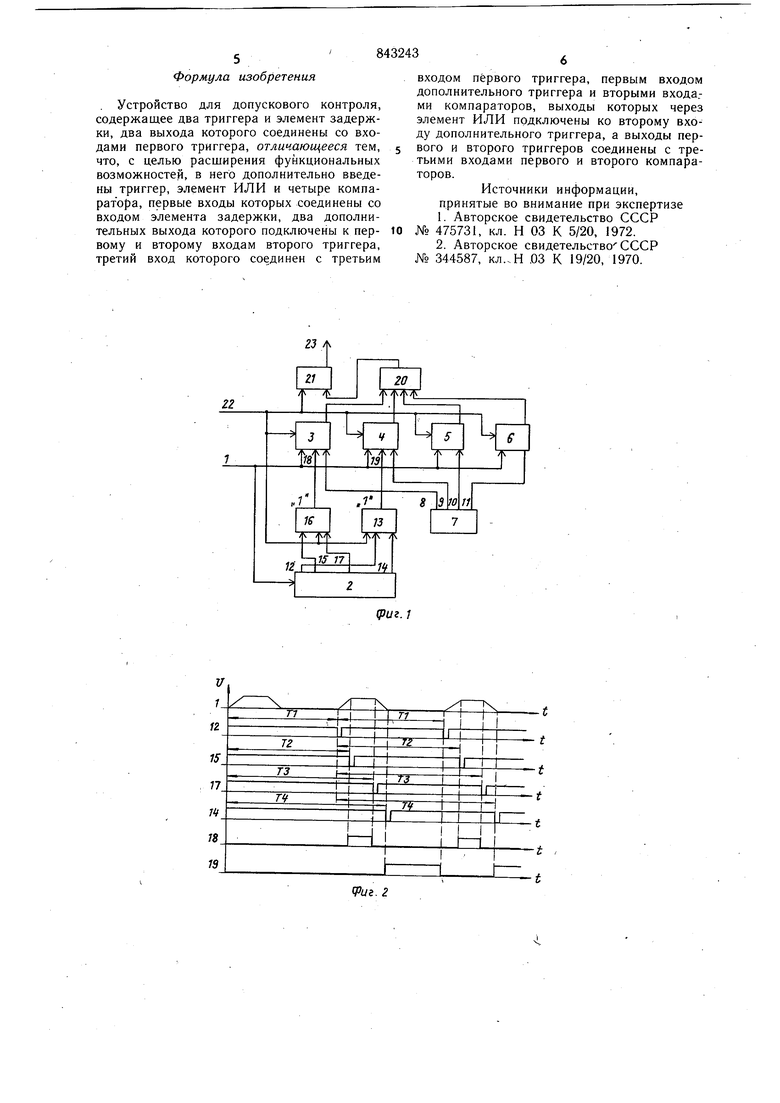

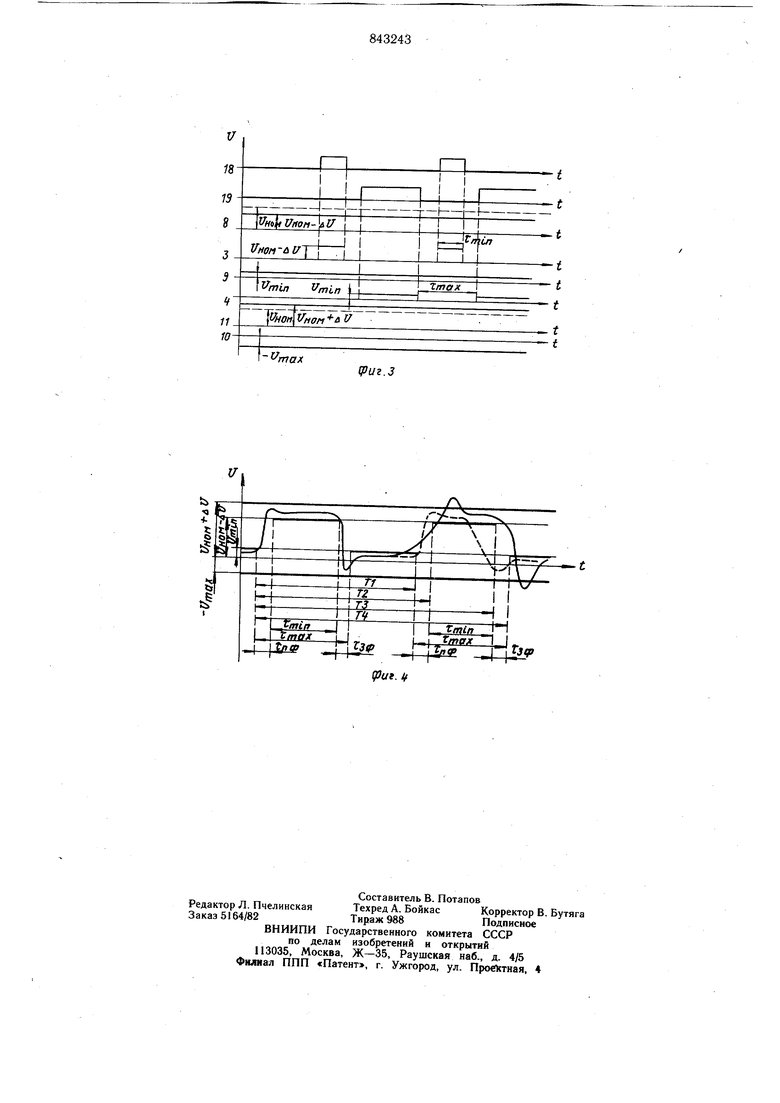

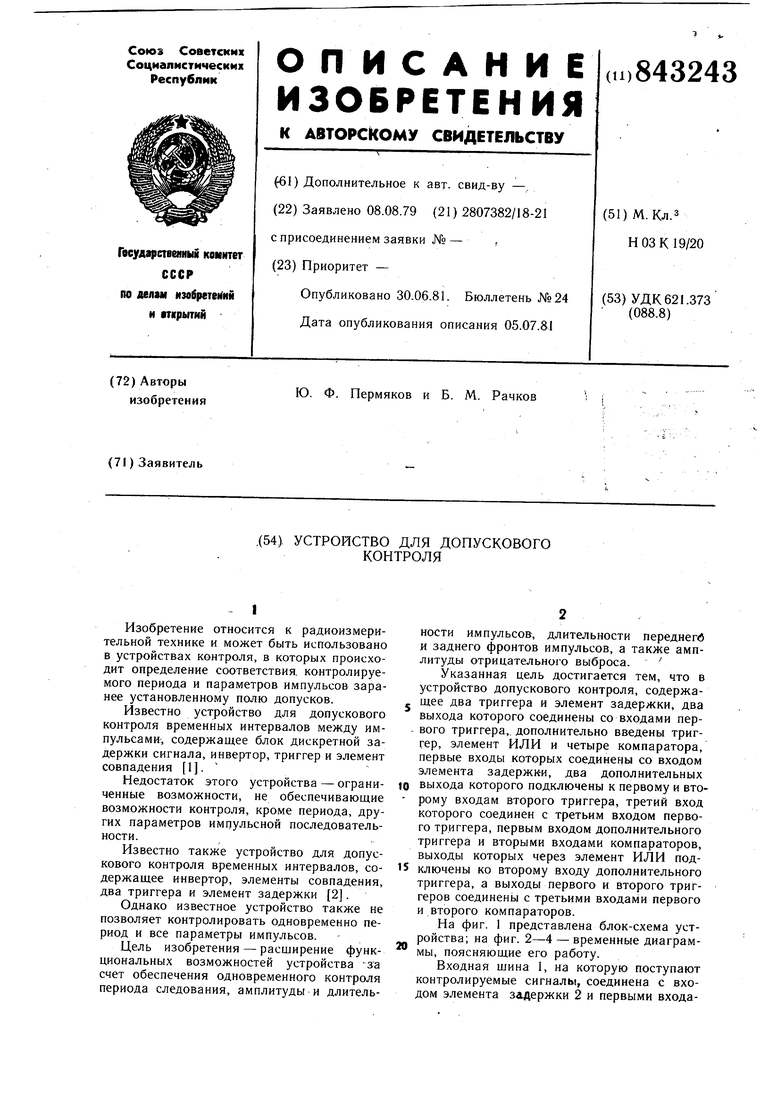

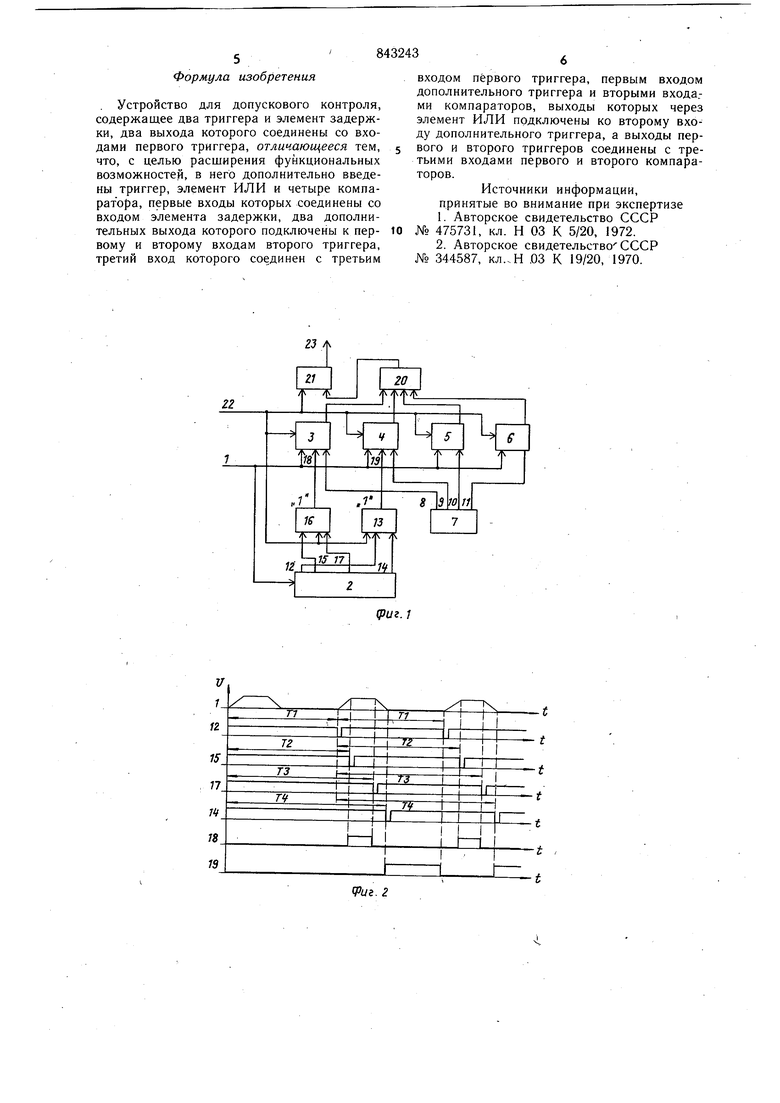

На фиг. 1 представлена блок-схема устройства; на фиг. 2-4 - временные диаграммы, поясняющие его работу.

Входная щина 1, на которую поступают контролируемые сигналы, соединена с входом элемента задержки 2 и первыми входами компараторов 3-6. Третьи входы компараторов 5 и 6 и четвертые входы компараторов 3 и 4 соединены с выходами источника эталонных напряжений 7 через шины 8-П. Первый -дополнительный выход 12 элемента 2 задержки соединен с входом «О установки второго триггера 13, а второй дополнительный выход 14 с входом «1 установки. Первый выход 15 элемента 2 задержки соединен с входом «1 установки первого триггера 16, а второй выход 17 с входом «О установки. Выход первого триггера 16 соединен с шиной 18 опроса первого компаратора 3, а выход второго триггера 13 соединен с шиной 19 опроса второго компаратора 4. Выходы компараторов 3-6 соединены с входами элемента ИЛИ 20, выход которого соединен с входом «1 установки дополнительного триггера 21. Вторые входы компараторов 3-6, вторые входы «О установки триггеров 13 и 16 и вход «О установки дополнительного триггера 21 объединены и соединены с шиной «Сброс 22. Выход 23 дополнительного триггера 21 является выходом устройства. Устройство работает следуюшим образом. Перед началом работы по шине 22 «Сброс импульс подается на триггеры и компараторы и устанавливает их в исходное состояние. Контролируемые импульсы по шине 1 подаются на первые входы компараторов 3-6 и вход элемента 2 задержки. По переднему фронту первого контролируемого импульса вырабатываются импульсы Т1- Т4, на выходах 12, 15, 17 и 14 элемента 2 задержки (фиг.-2). Импульс Т1 на выходе 12 элемента 2 определяет контролируемый период и начало переднего фронта, импульс Т2 - конец переднего фронта, импульс ТЗ - начало заднего фронта, импульс Т4 - конец заднего фронта контролируемого импульса. Импульсы Т2, ТЗ с выходом 15 и 17 формируют на триггере 16 импульс опроса, который поступает на вход 18 компаратора 3, а импульсы Т1, Т4 с выхода 12 и 14 формйруют на триггере 13 импульс опроса, который поступает на вход 19 компаратора 4. При этом на входы компараторов 3-6 по шинам 8-11 из источника 7 эталонных напряжений подаются потенциалы (фиг. 3); по шине 8 UHOM- U; по 9 шине 10-Umax, по шине П 1Гцом+Д-Так как по условиям контроля импульсы никогда не должны быть амплитудой больше, чем UHOHA+ AU, а амплитуда отрицательного выброса не должна быть больше чем то на компараторы 5 и 6 импульсы опроса не подаются и компараторы контролируют эти параметры все время. Если амплитуда контролируемого импульса больше Диили амплитуда отрицательного выброса больше, чем -Umax, сигнал с выходов компараторов 5 и 6 через элемент или 20 устанавливает триггер 21 в состояние «1 и на выходе 23 появляется сигнал. По входу 18 импульс опроса сравнивает на компараторе 3 (фиг. 3) .напряжения UHOM и и амплитуду контролируемого сигнала на времяТ,, причем амплитуда должна быть больше Оном- AU. В противном случае компаратор 3 переключается и через элемент ИЛИ 20 устанавливает триггер 21 в «1. По входу 19 импульс опроса сравнивает на компараторе 4 (фиг. 3) напряжение Umin и напряжение при отсутствии импульса, т.е. на время 1т„д компаратор 4 закрывается, а все остальное время он открыт, и при наличии импульса, или потенциала за пределамиСта к парато р 4 переключается, через элемент ИЛИ 20 устанавливает триггер 21 в «I и на выходе 23 появляется сигнал. Рассмотрим процесс контроля параметров импульсов и их периода. На фиг. 4 изображена временная диаграмма контроля импульса на соответствие заранее, устанавленному полю допусков. До « момента времени -г ц мпульс должен отсутствовать, компаратор 4 открыт; Навремя .компаратор 4 закрывается, а на время открывается компаратор 3. На времят:, компараторы 3 и 4 закрыты. За время Тпл амплитуда импульса должна измениться от UmutiflO величины большей, чем ЛЫ, т.е. контролируется время переднего фронта. Если амплитуда импульса к началу момента Сж п меньше, чем ищ,(ц- ди, как на втором и.мпульсе фиг. 4 компаратор 3 переключается и через элемент ИОИ 20 переключает триггер 21. Аналогично за время f импульс должен измениться от величины большей, чем UHCM-UU ДО величины меньше Umi.,,, т.е. контролируется время заднего фронта. Если амплитуда импульса окажется меньше ди во времяТ „,п. когда открыт компаратор 3, то он переключается и устанавливается триггер 21 в «1, а это означает, что длительность импульса меньше f.:. Если импульс начинается раньше, чем начался окончился позже тг„цд,т.е. времени когда компаратор 4 закрыт, этот компаратор переключается и устанавливается триггер 21 в «1.. В том случае, если амплитуда импульса станет больше, чем ди, пеР - ается компаратор 6, а еслйамплитуда отрицательного выброса больше, чем -Ц,зд /1ереключается компаратор 5 и это запоминается на триггере 21. Так как начало сформируется через время Т1, которое соответствует периоду, то переключение компаратора 4 раньше времени Т1, когда он открыт, означает отклонение величины периода от установленной. Таким образом, устройство позволяет контролировать период, амплитуду и длительность импульсов, длительность переднего и заднего фронта, амплитуду отрицательного выброса при незначительных аппаратурных затратах.

Формула изобретения

Устройство для допускового контроля, содержащее два триггера и элемент задержки, два выхода которого соединены со входами первого триггера, отличающееся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены триггер, элемент ИЛИ и четыре компаратора, первые входы которых соединены со входом элемента задержки, два дополнительных выхода которого подключены к первому и второму входам второго триггера, третий вход которого соединен с третьим

входом первого триггера, первым входом дополнительного триггера и вторыми входа.ми компараторов, выходы которых через элемент ИЛИ подключены ко второму входу дополнительного триггера, а выходы первого и второго триггеров соединены с третьими входами первого и второго компараторов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-06-30—Публикация

1979-08-08—Подача