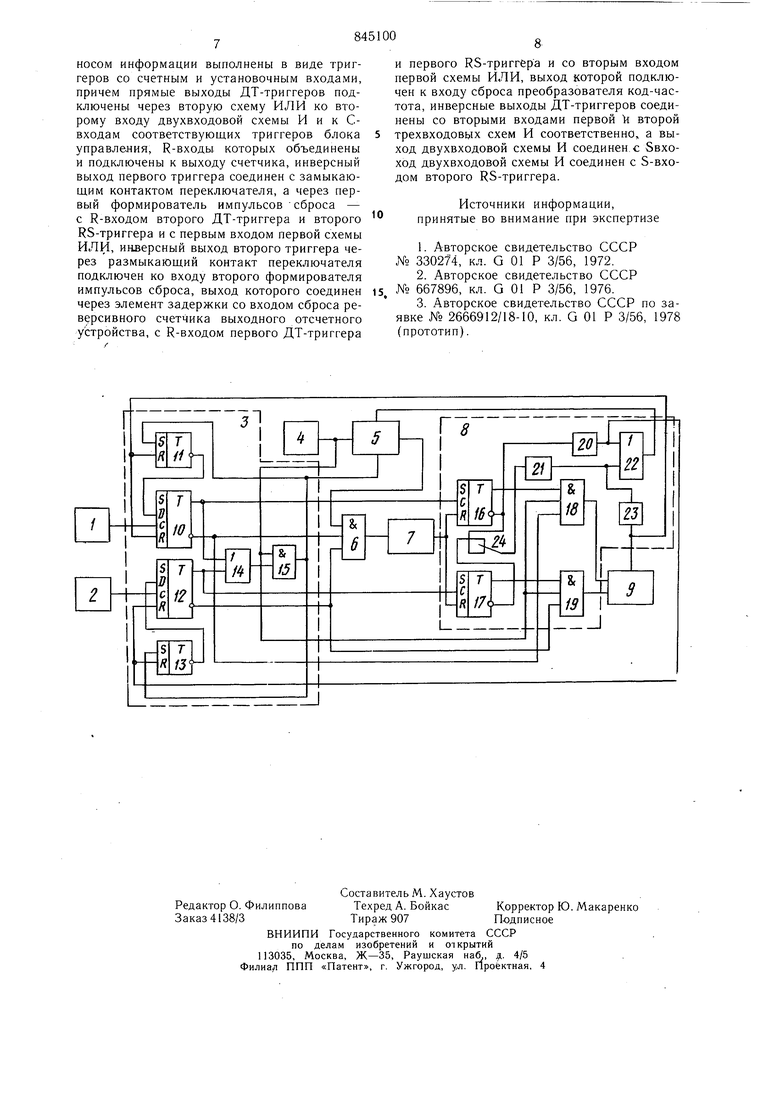

Изобретение относится к те.хнике электрических измерений параметров движения и может быть использовано для измерения разности скоростей вращения или перемещения рабочих органов машин и механизмов, в частности разности скоростей приводных точек многодвигательных агрегатов, выпускающих полосовые материалы, - бумагоделательных мащин, прокатных станов и др. Известен цифровой измеритель скоростей содержащий и.мпульсные датчики скорости, формирователи временных интервалов, генератор эталонной частоты, счетчики промежуточной памяти, блок сравнения и управления переносо.м информации, выходное отсчетное устройство 1. Недостатком известного устройства является использование метода измерения частоты, а не периода датчиков, что приводит к необходимости применения датчиков с большим числом импульсов на оборот. Известно устройство измерения скорости, содержащее импульсные датчики скорости, блок измерения периода с двумя триггерными формирователями, генератор эталонной частоты, преобразователь код-частота. счетчики промежуточной па.мяти, схему И, блок сравнения и управления переносом информации, вы.ходное отсчетное устройство нереверсивного типа 2. В указанном устройстве резко снижены требования к разрешающей способности датчика, но функции устройства ограничены только измерением относительных значений разности скоростей, измерение же абсолютных значений скорости или разности скоростей оказывается невозможным. Известен также измеритель скоростей, содержащий импульсные датчики скорости, генератор эталонной частоты, преобразователь код-частота, блок измерения периода с двумя триггерными формирователями, связанными общей шиной сброса, счетчики, блок управления переносом информации с двумя RS-триггерами, схемами И и ИЛИ и одним формирователем импульса сброса, связанным с выходами обоих триггеров, и выходное отсчетное устройство 3. В устройстве, работающем по методу измерения периода, реализовано измерение абсолютных значений скоростей. Недостаток его - отЬутствие возможности измерения абсолютных значений разности скоростей. Целью изобретения является измерение абсолютных значений разности скоростей. Цель достигается за счет того, что в устройство введены двухвходовая схема ИЛИ.Два формирователя импульсов сброса, элемент задержки, счетчик выходного отсчетного устройства выполнен реверсивным, а в качестве триггеров блока управления переносом информации применены триггеры со счетным и установочным входами, причем прямые выходы ДТ-триггеров подключены через вторую схему ИЛИ ко второму входу двухвходовой схемы И и к С-входам соответствующих триггеров блока управления, R-входы которых объединены и подключены к выходу счетчика, инверсный выход первого триггера соединен с замыкающим контактом переключателя, а через первый формирователь импульсов сброса - с R-входом второго ДТ-триггера и втррого RS-триггера и с первым входом первой схемы ИЛИ, инверсный выход второго триггера через размыкающий контакт переключателя подключен ко входу второго формирователя импульсов сброса, выход которого соединен через элемент задержки со входом сброса реверсивного счетчика выходного отсчетного устройства, с R-входом первого ДТ-триггера и первого RS-триггера и со вторым входом первой схемы ИЛИ, выход которой подключен к входу сброса преобразователя кодчастота, инверсные выходы ДТ-триггеров соединены со вторыми входами первой и второй трехвходовых схем И соответственно, а выход двухвходовой схемы И соединен с входом второго RS-триггера. На чертеже представлена схема измерителя. Измеритель включает датчики импульсов 1 и 2, связанные с вращающимися валами, скорость которых контролируется, блок измерения периода 3, генератор эталонной частоты 4, преобразователь кодчастота 5, трехвходовую схему И 6, счетчик 7, блок управления переносом информации 8, выходное отсчетное устройство с реверсивным счетчиком 9. Блок измерения периода 3 состоит из первого и второго триггерных формирователей временного интервала. В первый входят ДТ-триггер 10 и RSтриггер И, во второй - ДТ-триггер 12 и RS-триггер 13. Единичные выходы триггеров 10 и 12 подключены ко входам схемы ИЛИ 14, выход которой связан с одним из входов схемы И 15, второй вход которой связан с выходом генератора 4, а выход - со входами установки единицы триггеров 11 и 13 и входом управления преобразователя 5. Блок управления переносом информации 8 содержит триггеры 16 и 17 со счетным и установочным входами каждый, причем их счетные входы связаны соответственно с единичными выходами триггеров 10 и 12, а входы установки нуля с выходами счетчика 7, трехвходовые схемы И 18 и 19, первые входы которых связаны с единичными выходами триггеров 16 и 17, вторые - с инверсными выходами триггеров 10 и 12, третьи - с выходом генератора 4, а выходы - со входами сложения и вычитания реверсивного счетчика выходного отсчетного устройства 9. В состав блока входят также формирователи импульсов сброса 20 и 21, входы которых подключены к инверсным выходам -триггеров 16 и 17, выходы - ко входам схемы ИЛИ 22. выход которой связан с цепью сброса преобразователя 5. Кроме того, выход формирователя 21 связан через элемент задержки 23 с цепями сброса счетчика выходного отсчетного устройства 9 и первого триггерного формирователя блока 3, а формирователь 20 - с цепью сброса второго триггерного формирователя блока 3. В блоке 8 введен переключатель, который включен так, что его нормально открытый и нормально закрытый контакты подключают на вход формирователя 21 инверсный выход триггера 16 и 17. Устройство работает следующим образом, Цикл измерения разности скоростей состоит из трех этапов: первого - этапа измерения скорости, контролируемой датчиком 1; второго - этапа измерения скорости, контролируемой датчиком 2; и третьего - этапа индикации абсолютного значения разности двух измерений, записанного к концу второго этапа в счетчике выходного отсчетного устройства 9. В свою очередь каждый из первых двух этапов состоит из двух интервалов: первого - интервала измерения числа импульсов эталонной частоты f генератора 4, проходящих за период частоты импульсов датчика 1 или 2, и второго - интервала преобразования и переноса информации в выходное отсчетное устройство 9. К началу цикла измерения элементы схемы измерителя нахбдятся в следующем состоянии. Реверсивный счетчик выходного отсчетного устройства 9, счетчик кода управления преобразователя 5, счетчик 7 обнулены, триггеры 10, 11, 12, 16 и 17 - в состоянии нуля, триггер 13 - в состоянии единицы. Частота преобразования f на выходе преобразователя 5 отсутствует. Схема И 6 открыта, схемы И 15, 18 и 19 закрыты. Включение переключателя 24 такое, как показано на чертеже. Блокировка по Д-входу триггера 12 сигналом нуля с инверсного выхода триггера 13 исключает запуск второго триггерного формирователя блока 3 на первом этапе цикла измерения, что и определяет очередность измерения каждой из составляющих измеряемой разности скоростей. Очередной импульс датчика 1 вызывает запись единицы в триггер 10 по счетному входу, сигнал с выхода которого открывает схему И 15 и записывает единицу по счетному входу в триггер 16. Одновременно сигнал нуля с инверсного выхода триггера 10 блокирует схемы И 6 и 18. Импульсы эталонной частоты через схему И 15 поступают на вход управления преобразователя 5, формируя код периода NT, датчика 1 в памяти преобразователя 5. Второй импульс датчика 1 возвращает триггер 10 в исходное состояние, схема И 15 перекрывается, прекращая дальнейшее увеличение кода N. При этом следует иметь в виду, что первый же импульс с выхода схемы И 15 в начале интервала измерения периода Т-, устанавливает в состояние единицы триггер 11 и, тем самым, блокирует по Д-входу триггер 10 от повторной записи единицы.

Возврат триггера 10 в исходное состояние снимает блокировку со входов схем И 6 и. 18, фиксируя начало интервала преобразования и переноса информации. Процесс преобра:зования информации заключается в формировании временного интервала Г, длительность которого обратно пропорциональна значению периода Т датчика и прямо пропорциональна значению его частоты f, а значит и скорости вращения п,. Указанный интервал Г формируется как время заполнения счетчика 7 импульсами выходной частоты ffjp преобразователя 5, т. е.

т - /

г-г inp

где NO - емкость счетчика 7.

В то время

для первого этапа цикла измерения

и Г - «

fnjC

КпрЛ/т/

где коэффициент преобразования преобразователя 5.

Импульс переполнения счетчика возвращает триггер 16 в исходное состояние и вновь блокирует схему И 18. Последняя была открыта для прохождения импульсов эталонной частоты на вход сложения реверсивного счетчика выходного отсчетного устройства 9 в течение всего интервала преобразования, сойпадающего по времени с интервалом переноса информации.

Таким образом, в счетчике устройства 9 к концу первого этапа цикла измерения будет записано число

/Vofo

N,

ппЛ/.

Пр ,

учетом

Л/с

V O-TT N.-f,Ka,.

К

пр

Соответствующим выбором параметров устройства можно получить N., п., в единицах измерения скорости.

При окончании первого этапа измерения с помощью формирователя 20 генерируется импульс сброса, обнуляющий память преобразователя 5 и подготавливающий второй

триггерный формирователь блока 3 к приему информации.

Начало второго этапа измерения фиксируется поступлением очередного импульса датчика 2. Последовательность работы схемы аналогична работе на первом этапе. Перенос информации осуществляется с помощью триггера 17 и схемы И 19. При этом к концу этапа на вход вычитания реверсивного сче1чика устройства 9 поступит число импульсов N2, численно равное п, и,, таким образом, в нем окажется записанным результат, равный разности измеряемых скоростей.

После окончания интервала преобразования и переноса информации второго этапа цикла измерения с помощью формирователя 2 генерируется импульс сброса, обнуляющий память преобразователя 5, и с задержкой, вьфабатываемой элементом задержки 23, сбрасывающий в исходное состояние счетчик устройства 9 и первый триггерный формирователь блока 3. Время задержки выбирается равным требуе.мой длительности этапа индикации.

При необходимости осуществить режим измерения не разности, а абсолютного значения скорости переключатель 21 нужно включить в противоположное положение. При этом роль датчика скорости играет датчик 1.

Формула изобретения

Цифровой измеритель скоростей, содержащий два импульсных датчика скорости, выходы которых соединены с С-входами соответствующих ДТ-триггеров, Д-входы которых подключены к инверсным выходам, а R-входы - к R-входам соответствующих RS-триггеров, генератор эталонной частоты, выход которого соединен с первым входом двухвходовой схемы И и со входом преобразователя код-частота, второй вход которого подключен к выходу двухвходовой схемы И и к S-входу первого RS-триггера, а выход - к третьему входу первой трехвходовой схемы И, первый и второй вход которой соединены с инверсными выходами ДТ-триггеров, а выход - со счетчиком, первый и второй триггеры блока управления переносом информации, прямые выходы которых подключены к первым входам второй и третьей трехвходовым схемам И, вторые входы которых объединены и подключены к выходу генератора эталонной частоты, а выходы - к выходному отсчетному устройству, двухвходовую схему ИЛИ и переключатель, отличающийся тем, что, с целью измерения абсолютных значений разности скоростей, в него введены двухвходовая схема ИЛИ, два формирователя импульсов сброса, элемент задержки, счетчик выходного отсчетного устройства выполнен реверсивным, а триггеры блока управления переносом информации выполнены в виде триггеров со счетным и установочным входами, причем прямые выходы ДТ-триггеров подключены через вторую схему ИЛИ ко второму входу двухвходовой схемы И и к Свходам соответствующих триггеров блока управления, R-входы. которых объединены и подключены к выходу счетчика, инверсный выход первого триггера соединен с замыкающим контактом переключателя, а через первый формирователь импульсов сброса - с R-входом второго ДТ-триггера и второго RS-триггера и с первым входом первой схемы ИЛИ, инверсный выход второго триггера через размыкающий контакт переключателя подключен ко входу второго формирователя импульсов сброса, выход которого соединен через элемент задержки со входом сброса рев рсивного счетЧика выходного отсчетного устройства, с R-входом первого ДТ-триггера

И первого RS-триггера и со вторым входом первой схемы ИЛИ, выход которой подключен к входу сброса преобразователя код-частота, инверсные выходы ДТ-триггеров соединены со вторыми входами первой k второй трехвходовых схем И соответственно,, а выход двухвходовой схемы И соединен с SBXOход двухвходовой схемы И соединен с S-BXOдом второго RS-триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 330274, кл. G 01 Р 3/56, 1972.

2.Авторское свидетельство СССР № 667896, кл. G 01 Р 3/56, 1976.

3.Авторское свидетельство СССР по заявке № 2666912/18-10, кл. G 01 Р 3/56, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель относительных значений разности скоростей | 1979 |

|

SU934384A2 |

| Цифровой измеритель разности скоростей | 1979 |

|

SU934385A2 |

| Цифровой измеритель относительной разности скоростей | 1975 |

|

SU763797A1 |

| Измеритель параметров движения | 1979 |

|

SU873146A1 |

| Устройство для измерения относительных значений разности скоростей | 1980 |

|

SU957109A2 |

| Измеритель относительных значений разности скоростей | 1976 |

|

SU657349A1 |

| Цифровой измеритель соотношения скоростей | 1982 |

|

SU1040415A1 |

| Измеритель относительных значений разности частот | 1985 |

|

SU1272269A1 |

| Цифровой измеритель длительности периода | 1988 |

|

SU1582176A1 |

| Устройство для измерения текущего радиуса рулона | 1980 |

|

SU1040326A2 |

Авторы

Даты

1981-07-07—Публикация

1979-08-10—Подача