( 54 )УСТРОЙСТВО ЗАДЕРЖКИ АНАЛОГОВЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный источник питания с бестрансформаторным входом | 1986 |

|

SU1543392A1 |

| Интегратор | 1979 |

|

SU824226A1 |

| ВиьииЮОНАЯ | 1973 |

|

SU388303A1 |

| Расширитель импульсов | 1977 |

|

SU687575A1 |

| Генератор пилообразного напряжения | 1979 |

|

SU809519A1 |

| Двухтактный релаксатор | 1978 |

|

SU765987A1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2432669C1 |

| Устройство регулирования запасаемой энергии в первичной обмотке катушки зажигания | 1986 |

|

SU1498934A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU378873A1 |

Изобретение относится к импульсной технике и может использоваться в радиотехнических устройствах в которых требуется задержка аналоговых сигналов, например в радиоприемных устройствах диапазона очень низких и крайне низких частот.

Известны линии задержки сигналов с двухфазным питанием на МДП-транзисторах с последовательным переносом заряда, содержащие входной амплитудный квантователь с запоминающим конденсатором , п каскадов задержки, каждый из которых состоит из транзистора и конденсатора, включенного между стоком и затвором транзистора, и выходной истоковый повторитель с нагрузочным транзистором 1 ,

Однако такие линии задержки основаны на использовании противофазных источников тактовых импульсов, что усложняет устройство. Кроме того, в выходном сигнале присутствует несущая тактовая частота.

Известно также устройство задерж-. ки аналоговых сигналов, содержащее п последовательно соединенных звеньев, состоящих из разделительного конденсатора на входе, резистивного делителя питающего напряжения, средняя точка которого подключена к разделительному конден- ,catTOpy и к входу транзисторного усилителя с коллекторной и эмиттерной нагрузками, и времязадающей цепочки, состоящей из последовательно соединенных между коллектором и эмиттером конденсатором и резистором 2.

10

Однако указанное устройство задержки имеет недостаточную точность из-за сильно искаженной импульсной переходной характеристики.

Цель изобретения - повышение на15дежности .

Для достижения указанной цели в устройство зсшержки аналоговых сигналов , содержащее п последователь- . но соединенных звеньев, каждое из ко20торых содержит разделительный конденсатор,- подключенный ко входу узла, состоящего из транзисторного: усилителя с коллекторной и эмиттерной нагрузками, вход которого соеди25нен со средней точкой резистивного делителя питающего напряжения и входом узла задержки, и рремязадающей последовательной RC-цепи, включенной между коллектором и эмиттером тран30зисторного усилителя, в каждое звено

задержки введены первый суммирующий резистор на выходе узла задержки, последовательно соединенные эмит терный повторитель, дифференцирующая резистивно-емкостная цепочка и второй суммирующий резистор, вход эмиттерногр повторителя соединен с входом транзисторного усилителя, а другой выход второго суммирующего, резистора соединен с вторым выводом первого суммирующего резистора, и корректирующий усилитель -на транзистора с коллекторной нагрузкой, база транзистора соединена с общей точкой суммирующих резисторов, между эмиттером и общей шиной включен резистор обратной связи, к которому параллельно включена корректирующая цепочка, состоящая из последовательно соединённых конденсатора и резистора.

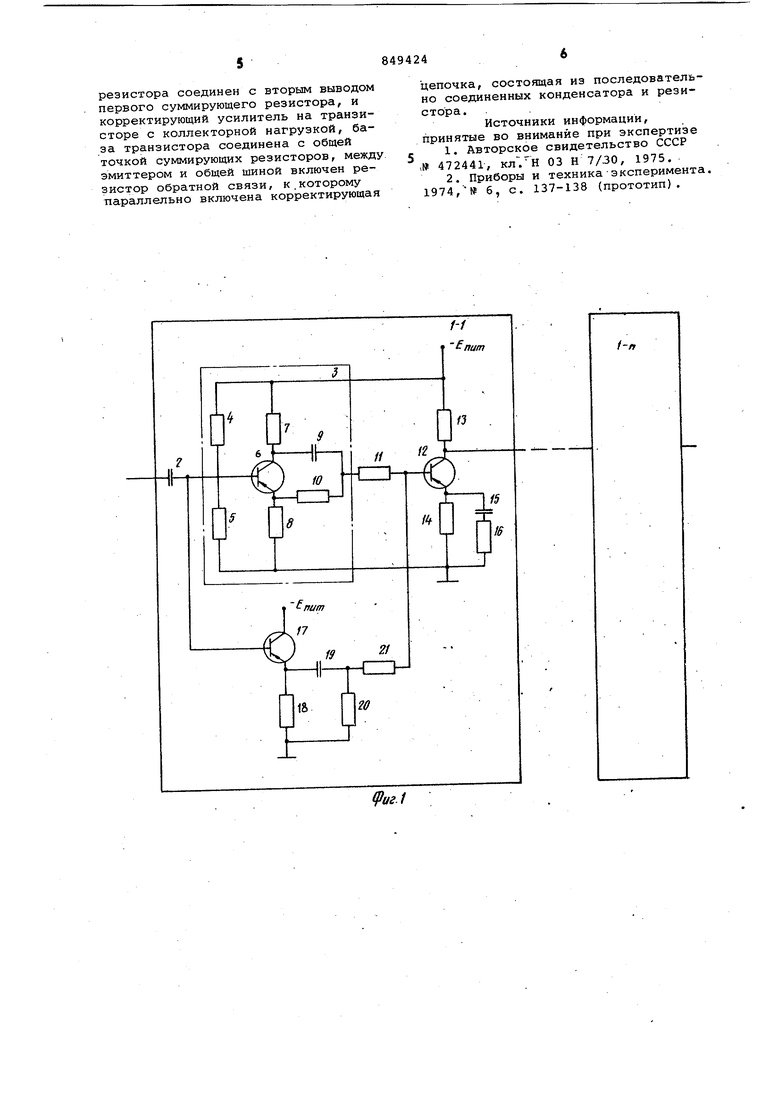

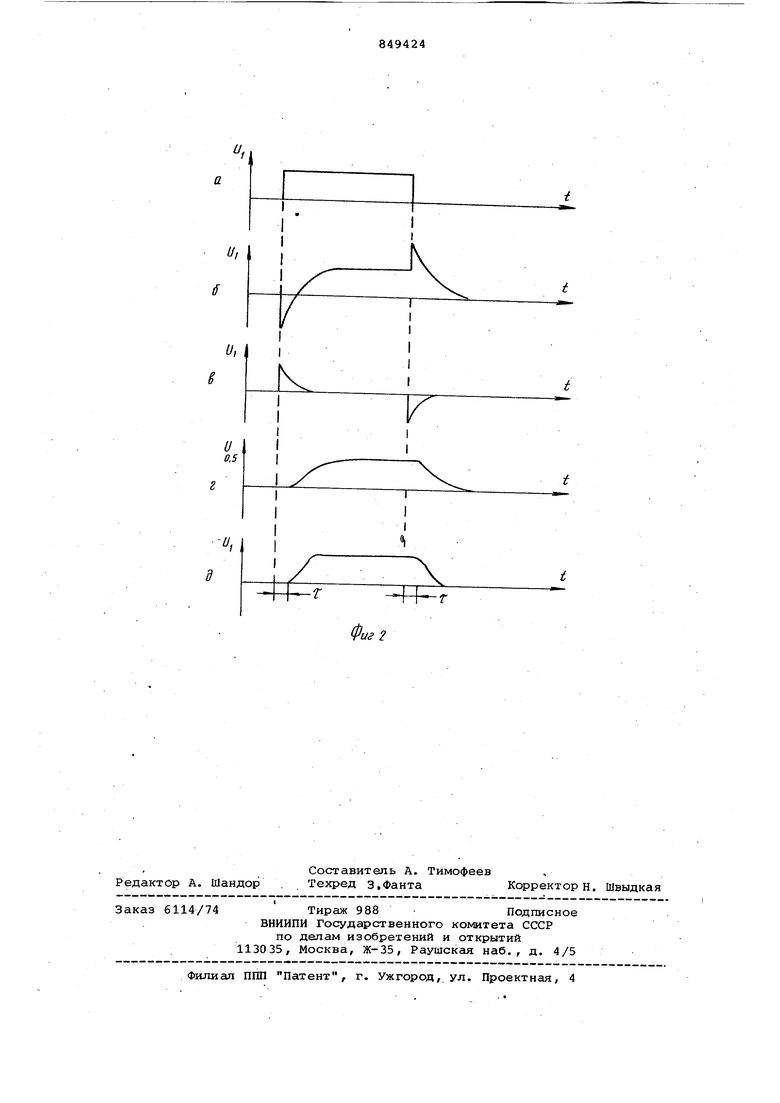

На фиг. 1 представлена принципиальная электрическая схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство задержки содержит п последовательно соединенных звеньев ,каждое из которых содержит разделительный конденсатор 2, узел задержки 3, состоящий из делителя питающего напряжения на резисторах 4 и 5, транзисторный усилитель 6 с нагрузками 7 и 8, времязадающей RCцепи на конденсаторе 9 и резистора 10. В состав каждого звена задержки входят суммирующий резистор 11, корректирующий усилитель на транзисторе 12 с резистором 13 в коллекторной цепи, резистор обратной связи 14, корректирующая цепочка на конденсаторе 15 и резисторе 16, эмиттерный повторитель на транзисторе 17 и резисторе 18, дифференцирующая цепочка конденсатора 19 и резистор 20, второй суммирующий резистор 21.

На фиг. 2а показан сигнал на входе устройства задержки аналоговых сигналов; на фиг. 2 б и в показаны изменения напряжения на выходе узла задержки и на выходе дифференцирующей цепочки; на фиг. 2 г и д показаны изменения напряжения на выходе суммирующих резисторов 11 и 12 и на выходе звена задержки 1-1.

Устройство работает следующим образом.

Выходной сигнал, показанный на фиг. 2 а, через, разделительный конденсатор 2 поступает.на входы на тразисторном усилителе.6 и эмиттерного повторителя на транзисторе 17. На фиг. 2 б видно, что форма импульса на выходе узла задержки 3 сильно искажена. Для устранения искажения переднего и заднего фронтов импульса вводится через эмиттерный повторител служащий для согласования, дифференцирующая цепочка, выделяющая передний и задний фронты импульса. Форма

напряжения на выходе дифференцирующей цепочки представлена на фиг. 2 в. Сигналы с выходов узла Задержки и дифференцирующей цепочки складываются на суммирующих резисторах 11 и 2 21. Как видно из фиг. 2 г, сигнал на выходе суммирующих резисторов ослабляется и имеет относительно .большое время нарастания и спада фронтов. Дляустранения указанных

Q недостатков вводится корректирующий усилитель на транзисторе 12. Корректирующей цепочкой, состоящей из конденсатора 15 и резистора 16 осуществляется регулировка фронтов нарастания и спада импульса.На фиг.2д

5 показано изменение напряжения на выходе корректирующего усилителя, являющегося выходом звена задержки, где - время задержки импуль- . сного сигнала.

0 Использование эмиттерного повторителя с дифференцирующей цепочкой, суммирующих резисторов, корректирующего усилителя с корректирующей цепочкой выгодно отличает предлагаемое устройство от известного, так как позволяет за счет значительного улучшения импульсной переходной характеристики повысить надежность устройства.

Q Применение предлагаемого устройства задержки аналоговых сигналов в исследовании спектральных и статиG ческих характеристик тонкой структуры резонансных излучений магнитосферы в радиодиапазоне позволяет

5 бблее точно измерять интенсивность естественного радиоизлучения верхней атмосферы.

40

Формула изобретения

Устройство задержки аналоговых сигналов, содержащее п последовательно соединенных звеньев, каждое из которых содержит разделительный конденсатор, подключенный ко входу узла задержки,состоящего из транзисторного усилителя с коллекторной и змиттерной нагрузками, вход которого

соединен со средней точкой резистИвного делителя питающего напряжения и входом узла задержки, и времязадающей последовательной RC-цепи, включенной между коллектором и эмиттером транзисторного усилителя, о тличающееся тем, что, с целью повышения надежности, в каждое звено задержки введены цервый суммирующий резистор на выходе узла задержки, последовательно соединенные эмиттерный повторитель, дифференцирующая резистивно-емкостная цепочка и второй суммирующий резистор, вход эмиттерного повторителя соединен с входом транзисторного усилителя, а

другой вывод второго суммирующего

резистора соединен с вторым выводом первого суммирующего резистора, и корректирующий усилитель на транзисторе с коллекторной нагрузкой, база транзистора соединена с общей точкой суммирующих резисторов, между эмиттером и общей шиной включен резистор обратной связи, к.которому параллельно включена корректирующая

цепочка, состоящая из последовательно соединенных конденсатора и резистора.

Источники информации, принятые во внимание при экспертизе

/-/

и,

и,

К

к

Авторы

Даты

1981-07-23—Публикация

1979-07-04—Подача