(54) РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулируемый преобразователь переменного напряжения в переменное | 1986 |

|

SU1339819A1 |

| Электропривод переменного тока | 1987 |

|

SU1508336A1 |

| СПОСОБ ПЕРЕКЛЮЧЕНИЯ ОТВЕТВЛЕНИЙ ОБМОТКИ ТРАНСФОРМАТОРА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2133977C1 |

| Преобразователь постоянного напряжения в однофазное переменное с амплитудно-импульсной модуляцией | 1981 |

|

SU997204A1 |

| Асинхронный электропривод | 1986 |

|

SU1339864A1 |

| Устройство для ограничения угла регулирования многозонного сетевого преобразователя | 1983 |

|

SU1128347A1 |

| Преобразователь с многофазной широтноимпульсной модуляцией | 1991 |

|

SU1793523A1 |

| Устройство для управления током луча электронно-лучевой термической установки | 1980 |

|

SU877801A1 |

| Устройство для автоматического регулирования реактивной мощности | 1989 |

|

SU1674306A1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТНЫМ АСИНХРОННЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2081503C1 |

1

Изобретение относится к электротехнике, а более конкретно к устройствам для регулирования напряжения потребителей переменного тока промышленной и повышенной частоты повышенной мош,ности.

Известны регуляторы 1 и 2.

Однако они не позволяют осуществлять индивидуальное регулирование напряжения потребителей промышленной и повышенной частот в условиях изменения их параметров .

Известен регулятор, который содержит группу встречно-параллельно соединенных тиристоров, дросселя для выравнивания токов между параллельными ветвями тиристоров и схему управления, формирующую пакеты синусоид питающего напряжения, период которых постоянен, а длительность меняется в зависимости от требуемого напряжения на нагрузке 3.

Неравномерное распределение токов между параллельно включенными вентилями в регуляторе приводит к завышению мощностей применяемых вентилей и к необходимости применять выравнивающие, индуктивные делители тока, что приводит к увеличению массы и габаритов устройства и ухудшению его энергетических показателей. Кроме того, этот регулятор работоспособен только на промышленной частоте 50 Гц. Пчмене ние индуктивных делителей нагрузки с целью выравнивания токов через параллельно включенные тиристоры эффективно толькб при работе регулятора на низких частотах (порядка 50 Гц), когда длительность установившегося режима работы тиристора, равная при число-импульсном регулировании полупериоду питающего нагрузку напряжения, значительно (на 1-2 порядка) превышает длительность динамических режи10мов работы тиристора (включение и выключение тиристора). При работе регулятора на повышенных частотах (500-10000Гц) длительность установившегося режима работы тиристора становится соизмеримой с временем включения и выключения, поэтому при15менение магнитных делителей нагрузки не обеспечивает равномерного распределения тока через согласно-параллельно включенные тиристоры, что ведет к неустойчивой работе регулятора и выходу из строя тиристо20ров.

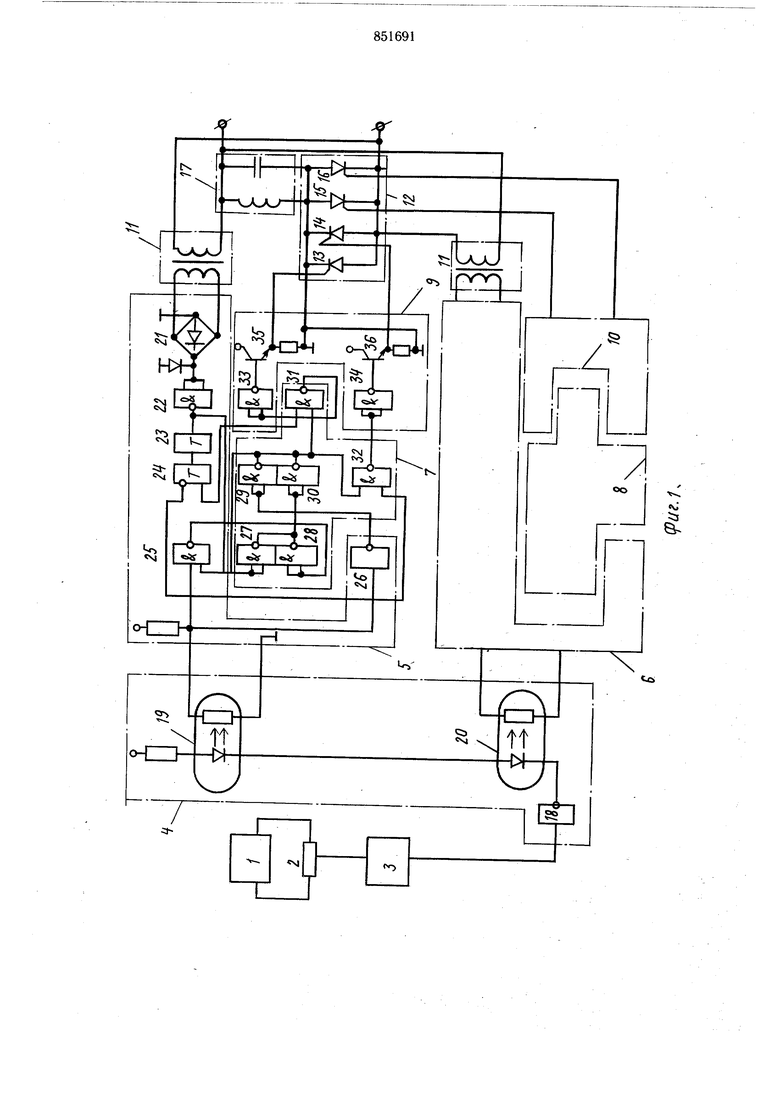

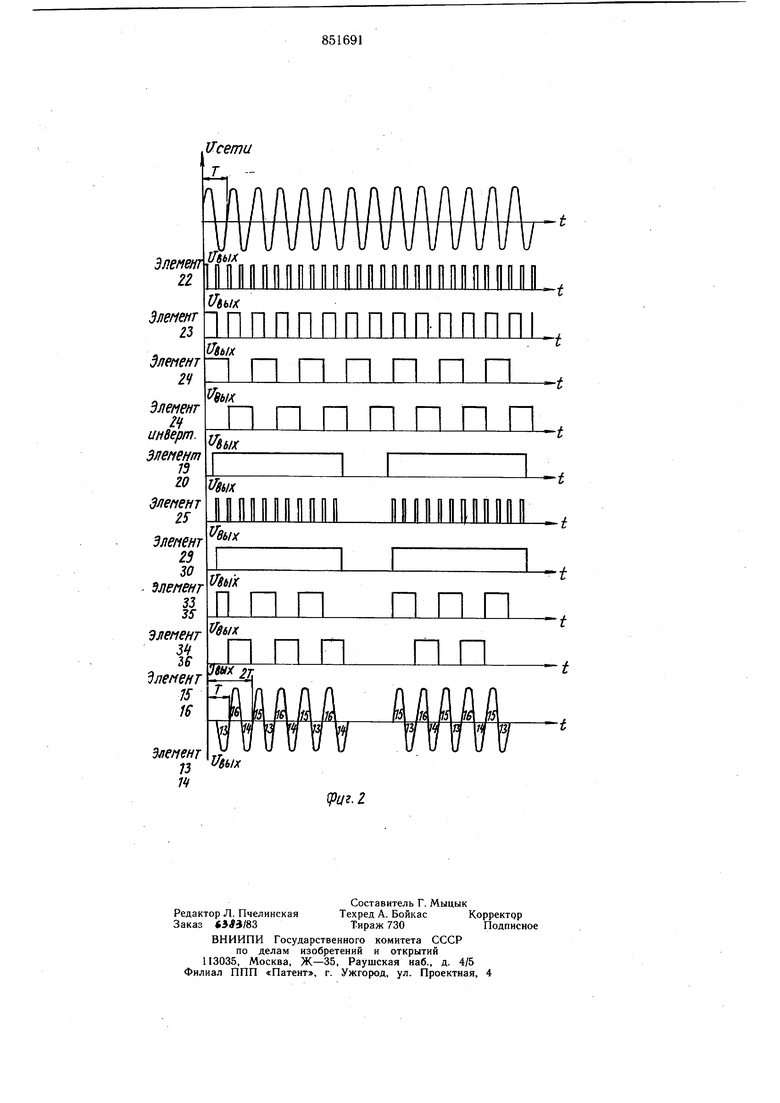

Известен также - регулятор, который при переменном индуктивноемкостном характере нагрузки ведет к неустойчивой работе. а при значительных сдвигах фазы тока нагрузки относительно напряжения - к невозможности нормальной работы, вследствие появления одноволнового режима 4. Наиболее близок к предлагаемому по технической сущности регулятор, содержащий бивентиль на тиристорах и схему управления, состоящую из источника питания, цепи обратной связи, задатчика, логического блока, коммутационного и выходного блоков. Схема управления формирует пакет однополярных управляющих импульсов с длительностью каждого импульса, равной половине периода питающего тиристоры напряжения повыщенной частоты, и щириной пакета, определяемой уровнем задающего сигнала в момент прохождения синусоиды питающеро нагрузку напряжения через ноль 5. Недостатком известного регулятора является отсутствие устройств, обеспечивающих равномерную токовую нагрузку согласно-параллельно включенных тиристоров и их завышенная установленная мощность. Цель изобретения - снижение ма.ссы и габаритов регулятора, а также снижение потерь электроэнергии. Поставленная цель достигается тем, что регулятор содержащий две группы встречно-параллельно включенных тиристоров и схему управления, состоящую из последовательно включенных задатчика, генератора пилообразного напряжения и блока развязки каналов управления тиристорами, подключенного к логическому блоку, ко входу которого подключен блок синхронизации, а к выходу - выходной блок формирования управляющих импульсов введены два блока формирования сигналов управления и два блока коммутации, формирующие пакет упр авляющих импульсов, поочередно поступающих на согласно-параллельно включенные тиристоры с длительностью каждого импульса не более одного периода питающего нагрузку напряжения и щириной пакета, определяемой уровнем задающего сигнала, причем вход блока формирования сигналов управления соединен с блоком синхронизации и блоком развязки каналов управления, а выход - с блоком коммутации, выход которого соединен с выходным блоком. Блок формирования сигналов управления содержит два последовательно включенных триггера со счетным входом, образующих делитель частот на четыре, причем вход этого делителя подключен через логический элемент НЕ и двухполупериодный выпрямитель к блоку синхронизации, а прямой и инверсный выходы - к блоку ком1 утации, содержащему триггер образованный четырьмя логическими элементами 2И-НЕ, вход которого-подключен к блоку формирования сигналов управления, а выход через элементы 2И-НЕ соединен со вхбдом блока выходного устройства. На фиг. 1 представлена электрическая схема предлагаемого регулятора; на фиг. 2временные диаграммы, поясняющие его работу. Регулятор содержит источник 1 питания, задатчик 2; генератор 3 пилообразного напряжения, блок 4 развязки каналов управления тиристорами, два блока 5 и 6 формирования сигналов управления, два блока 7 и 8 коммутации, два блока 9 и 10 формирования управляющих импульсов, два блока 11 формирования синхронизирующих импульсов, бивентиль 12, состоящий из двух групп па-, раллельно-согласно соединенных тиристоров 13-16, соединенный последовательно с нагрузкой 17. Блок развязки каналов управления содержит логический элемент НЕ 18 выполняющий функцию компаратора, к выходу которого подключены оптронные резисторы 19 и 20. Каждый из блоков формирования сигналов управления cocfoит из двухполупериодного выпрямителя 21, соединенного через логический элемент НЕ 22 с двумя последовательно включенными триггерами 23 и 24, и двух логических элементов 2И-НЕ 25 и 26 передающих сигналы в блок коммутации. Каждый из блоков коммутации содержит триггер, образованный четырьмя логическими элементами 2И-НЕ 27-30, к выходу которого подключены логические элементы 2И-НЕ 31 и 32. Каждый из блоков формирования управляющих импульсов содержит по два логических элемента НЕ 33 и 34, подключенных к транзисторам 35 и 36. Рассмотрим работу регулятора с момента времени (фиг. 2). Все тиристоры бивентиля закрыты, так как отсутствуют сигналы управления. Логические элементы 25 и 26 и триггер 27-30 формируют сигнал управления «1, синхронизированный передним фронтом с моментом прохождения через ноль напряжения в сети (и ы элементов 29 и 30). Триггер 24 формирует прямой и инвертированный сигналы «1 длительностью, равной периоду сети Т (U|,элемента 24), синхронизированные сетевым напряжением. Логические элементы 2И-НЕ 31 и 32 передают сигналы с выходов триггера 25 и 27- 30 на элементы НЕ 33 и 34. Выходные сигналы элементов 33 и 34 усиливают транзисторы 35 и 36 и подают их на управляющие электроды тиристоров 13 и 14 бивентиля. Таким образом, на управляющие электроды согласно-параллельно включенных тиристоров поочередно поступают импульсы длительностью t Т, при этом каждый импульс передним фронтом синхронизирован с моментом прохождения через ноль сетевого напряжения, а число имульсов определено величиной напряжения задатчика 2.

Таким образом, при Т /2 подан сигнал управления на тирнсторы 13 и 15, но включен один из них (тиристор 13), так как другой (тиристор 15) закрыт обратным напряжением сети. Считаем, что на аноде тиристора 13 положительный потенциал относительно катода.

В интервал времени 2Т t Т подан сигнал управления на тиристоры 14 и 16. Вентиль 16 открыт, а 14 закрыт обратным напряжением сети до момента t Т + , затем закрыт вентиль 16 и открыт 14, т.е. согласно-параллельно включенные тиристоры 13 и 14 проводят ток нагрузки поочередно, при этом период коммутации одного и того же тиристора составляет 2Т.Коммутация тиристоров 15 и 16 происходит аналогично.

Как видно из диаграммы (фиг. 2) согласно-параллельно включенные тиристоры поочередно проводят ток в течение соответствующего полупериода питающего напряжения. В этом случае для всякой нагрузки средние значения токов за период коммутации 2Т через согласно-параллельно соединенные тиристоры равны.

В случае применения большего (трех и более) количества согласно-параллельно включенных тиристоров бивентиля необходимо изменить блок коммутации тиристоров, дополнив его счетчиком управляющих импульсов.

Таким образом, предлагаемое устройство позволяет уменьшить массу и габариты регулятора переменного напряжения благодаря отсутствию индуктивных делителей тока и увеличить нагрузочную способность регулятора благодаря равенству токов через согласно-параллельно включенные вентили без увеличения числа установленных тиристоров Например, в случае применения бивентиля из двух групп согласно-параллельно включенных вентилей на промышленной частоте 50 Ги, масса и габариты регулятора снижаются на 14%, а выходной ток увеличивается на 25- 30%.

Формула изобретения

напряжения и блока развязки каналов управления тиристорами, подключенного к логическому блоку, ко входу которого подключенного к логическому блоку, ко входу которого подключен блок синхронизации, а к

выходу - блок формирования управляющих импульсов, отличающийся тем, что, с целью улучшения массо-габаритных и энергетических показателей, в него введены два блока формирования сигналов управления и два блока коммутации, формирующие пакет управляющих импульсов, поочередно поступающих на согласно-параллельно включенные тиристоры с длительностью каждого импульса не более одного периода питающего натрузку напряжения и щириной пакета, определяемой уровнем задающего сигнала,

5 причем вход блока формирования сигналов управления соединен с блоком синхронизации и блоком развязки каналов управления, а выход - с блоком коммутации, выход которого соединен с блоком формирования .управляющих импульсов.

5 вход этого делителя подключен через логический элемент НЕ и двухполупериодный выпрямитель к блоку синхронизации, прямой и инверсный выходы - к блоку коммутации, содержащему триггер, образованный

Q четырьмя логическими элементами 2И-НЕ, входы которого подключены к блоку формирования сигналов управления, а выход через логические элементы 2И-НЕ соединен со входом блока формирования управляющих импульсов.

5Источники информации,

принятые во внимание при экспертизе

o-CZ}--f

M

Элемент

zz

J6/X

Элемент

1ППППППППП-ПППП1 23

бш

длепент 24

%/лг

Элемент

Л нВерт.

6bfX

Jienenm 75 W

вш

Злепет 25

вых

Элемент 23

го

Шб1Х длемен)

П

33 35

Vet/x

элемент 3

36

тг

Элемент 15 IS

длемент

бых

13 14

(Риг.г

П

Авторы

Даты

1981-07-30—Публикация

1978-10-17—Подача