Изобретение относится к электротехнике, а именно к устройствам для регулирования напряжения потребителе переменного тока промышленной и по- вышенной частот.

Цель изобретения - повышение надежности и исключение высших гармони в кривой питающего напряжения.

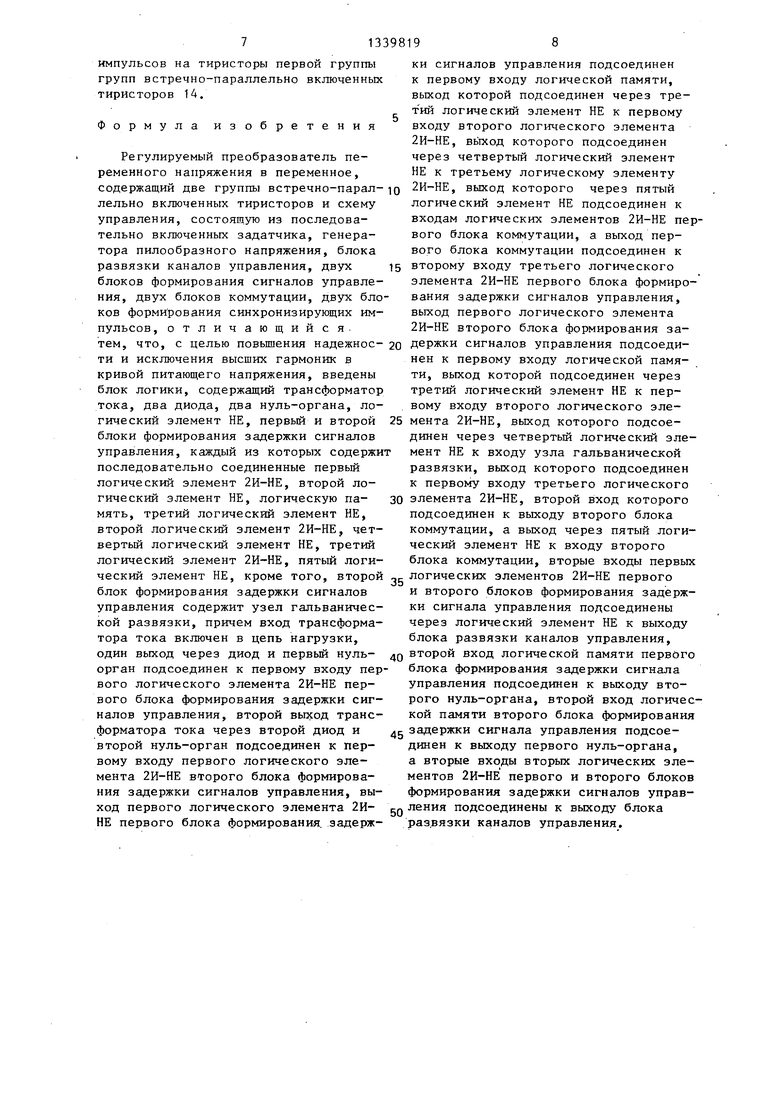

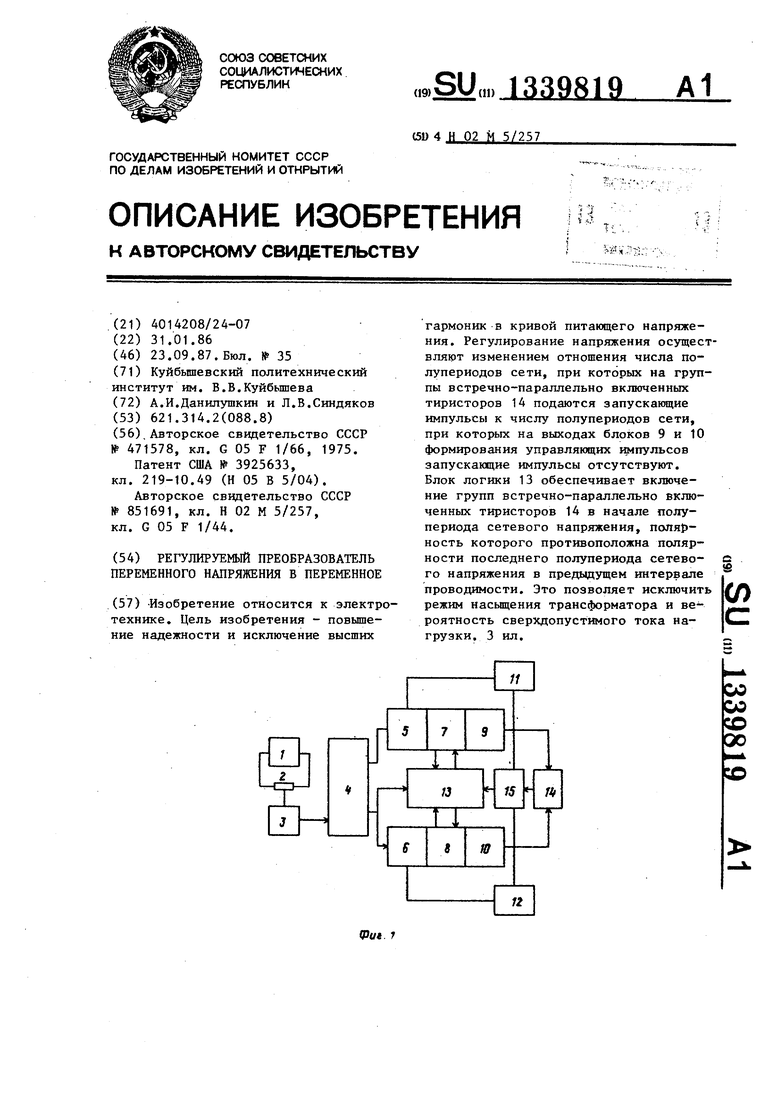

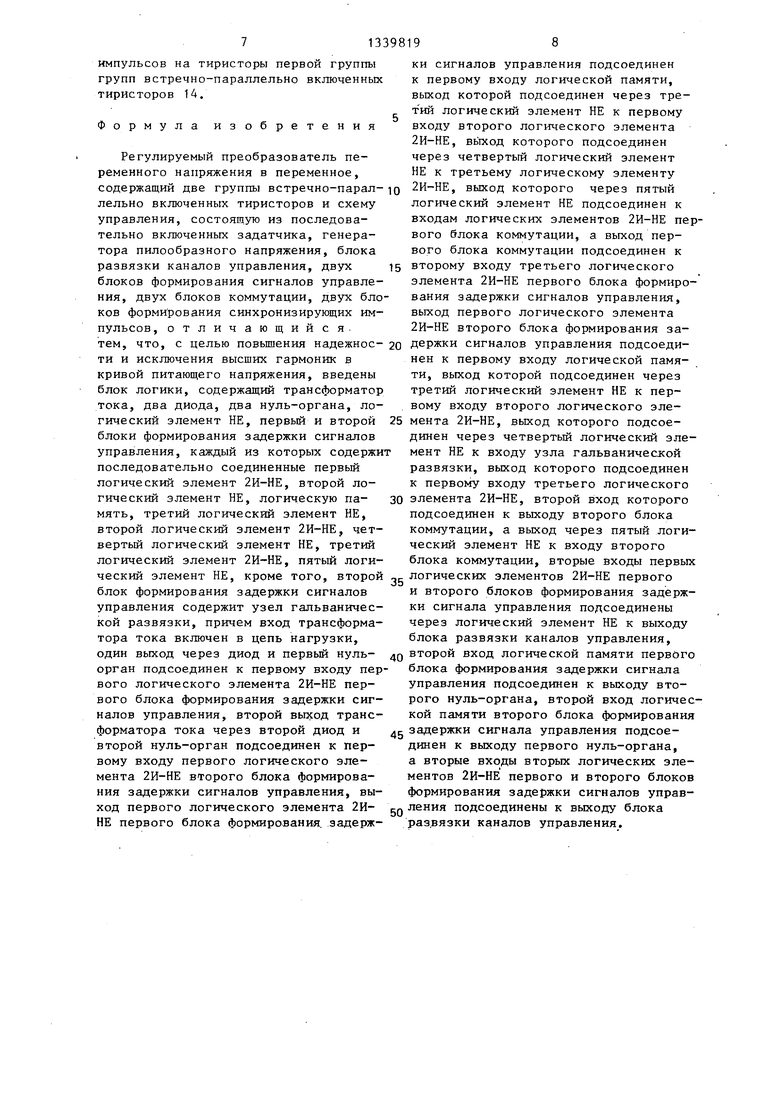

Ни фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - электрическая схема блока логики; на фиг. 3 - временная диаграмма, поясняющая работу -устройства.

Устройство содержит источник 1 питания, задатчик 2, генератор 3 пилобразного напряжения, блок 4 развязки каналов управления, два блока 5 и 6 формирования сигналов управления два блока 7 и 8 коммутации, два блока 9 и 10 формирования управ- ляющйх импульсов, два блока 11 и 12 формирования синхронизирующих импульсов, блок 13 логики, две группы встречно-параллельно включенных тири торов 14, соединенные последовательн с нагрузкой 15.

Блок 13 логики (фиг. 2) содержит трансформатор 16 тока, два диода 17 и 18, два нуль-органа 19 и 20, логи- ческий элемент НЕ 21, два блока 22 и 23 формирования задержки сигнала управления, причем вход трансформатора 16 тока, подсоединен к нагрузке, один выход через диод 17 и первый нуль-орган 19 подсоединен к первому входу блока 22 формирования задержки сигнала управления, второй выход через диод 18 и второй нуль-орган 20 подсоединен к первому входу блока 23 формирования задержки сигнала управления, к вторым входам первого 22 и второго 23 блоков формирования задерки сигнала управления подсоединен выход первого логического элемента НЕ 21, вход которого и третий вход первого 22 и второго 23 блоков формирования задержки сигналов управления подсоединены к первому выходу блока 4 развязки каналов управления, чет- вертый вход первого блока 22 формирования задержки сигнала управления подсоединен к одному из выходов первого блока 7 коммутации, четвертый вход второго блока 23 формирования

задержки сигнала управления подсоединен к одному из выходов второго блока 8 коммутации, пятьй вход первого блока 22 формирования задержки сигнала

.

5

о д -

5

5

управления подсоединен к выходу второго нуль-органа 20, пятый вход второго блока 23 формирования задержки сигнала управления подсоединен к выходу первого нуль-органа 19, выход первого блока 22 формирования задержки сигнала управления подсоединен к одному из входов первого блока 7 коммутации, выход второго блока 23 формирования задержки сигнала управления подсоединен к одному из входов второго блока 8 коммутации.

Блок 22 (23) формирования задержки сигнала управления содержит последовательно соединенные первый логический элемент 2И-НЕ 24 (25), второй логический элемент НЕ 26 (27), логическую память 28 (29), третий логический элемент НЕ 30 (31), второй логический элемент 2И-НЕ 32 (33), четвертый логический элемент НЕ 34 (35), третий логический элемент 2И-НЕ 36 (37), пятый логический элемент НЕ 38 (39) . Кроме того, второй блок 23 формирования задержки сигнала управления содержит дополнительно узел 40 гальванической развязки, выполненный, например, на оптронных резисторах, вход которого подсоединен к выходу четвертого логического элемента НЕ 35, а выход - к первому входу третьего логического элемента 2И-НЕ 37, причем выход пятого логического элемента НЕ 38 (39) блока 22 (23) формирования задержки сигнала управления подсоединен к одному из входов соответствующего блока 7 и 8 коммутации, первый вход первого логического элемента 2И-НЕ 24 (25) подсоединен к выходу первого или второго нуль-органа 19 и 20 соответственно, а второй вход - к выходу первого логического элемента НЕ 21, вход которого и один из входов второго логического элемента 2И-НЕ 32 (33) подсоединены к одному из выходов блока развязки каналов управления, второй вход третьего логического элемента 2И-НЕ 36 (37) блока 22 (23) формирования задержки сигнала управления подсоединен к одному из выходов соответствующего блока 7 или 8 коммутации, один из входов логической памяти 28 первого блока 22 формирования задержки сигнала управления подсоединен к выходу второго нуль-органа 20, а один из входов логической памяти 29 второго блока 23 формирования задержки сигнала управления подсоединен к выходу первого нуль-органа 19.

Каждый из блоков коммутации 7 и 8 содержит триггер, образованный логическими элементами 41-44, выход которого подсоединен к четвертому входу блока 22 формирования задержки сигнала управления, и два логических элемента 2И-НЕ 45 и 46, один из вхо- дов которых подсоединен к выходу блока 22 формирования задержки сигнала управления. Предлагаемое устройство может быть реализовано, например, на элементах серии 511,

Устройство работает следующим образом.

Пока сигналы управления отсутствуют, сигнал на выходе блока 4 равен нулю, все тиристоры групп встречно- параллельно включенных тиристоров 14 закрыты, и ток нагрузки 15 равен 0. Логический элемент НЕ 21 формирует на выходе сигнал логической 1, а нуль-органы 19 и 20 формируют логический О. При отсутствии сигнала управления на выходе блока 4 сигнал на выходе блоков 7 и 8 равен О и логические элементы обоих блоков 22 и 23 формируют на выходе логических элементов НЕ 38 и 39 сигнал, соответствующий логическому О,

При подаче сигнала задания с за

датчика 2 в момент t, (фиг. 3) блок 4 формирует сигнал логической 1, который воздействует на логический элемент НЕ 21 и логические элементы 2И-НЕ 32 и 33. Так как в момент t, подачи сигнала управления тиристоры закрыты, нуль-органы 19 и 20 формируют на вькоде сигнал О. На входы логических элементов 2И-НЕ 24 и 25 блоков 22 и 23 формирования задержки сигнала управления воздействуют

.сигналы О, Логический элемент 2И-НЕ 45 менты 2И-НЕ 32 и 33, 24, логические элементы НЕ 26иЗО, логическая память 28 и логический элемент 2И-НЕ 25, логические элементы НЕ 27 и 31, логическая память 29 формируют на выходе элементов НЕ 30 и 31 gQ сигнал логической 1, который воздействует на логические элементы 2И- НЕ 32 и 33 соответственно. На второй вход каждого из логических элементов 2И-НЕ 32 и 33 в момент времени t, воздействует сигнал 1 с выхода блока 4, Сигнал О с выхода логического элемента 2 И-НЕ 32 через логический элемент НЕ 34 воздействует на

Пусть момент t, о управления с выхода ет с интервалом пров группы тиристоров гр раллельно включенных В этом случае в моме логического элемента ствуют две логически элемент НЕ 26 формир 55 1 которая воздейс кую память 28. После на выходе сигнал 1 логический элемент Н ет на один из входов

д

логический элемент 2И-НЕ 36. На второй вход логического элемента 2И-НЕ 36 воздействует сигнал с выхода блока 7 коммутации, синхронизированный передним фронтом с моментом прохождения через О напряжения сети (момент tj). Логический элемент 2И-НЕ 36 и логический элемент НЕ 38 формируют в момент с сигнал логической 1, который воздействует на блок 7 коммутации, разрешая подачу управляющих импульсов на тиристоры первой группы групп встречно-параллельно 5 включенных тиристоров 14. Сигнал 1 с выхода логического элемента 2И-НЕ 33 в момент с, через логический элемент НЕ 35 и узел 40 гальванической развязки воздействует на логический элемент 2И-НЕ 37, на второй вход которого воздействует сигнал с выхода блока 8 коммутации, синхронизированный с моментом прохождения через нуль

0

напряжения сети. В момент t логичес- кий элемент 2И-НЕ 37 и логический элемент НЕ 38 формируют логическую 1, которая воздействует на блок 8 коммутации, разрешая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров 14, Таким обра- зом, при первоначальном включении устройства оба канала управления получают разрешение на включение тиристо

ров в момент с2 прохождения напр5гже- ния сети через нуль. Блоки 9 и 10 воздействуют на тиристоры групп встречно-параллельно включенных тиристоров 14, осуществляя их поочередную коммутацию.

В момент tj окончания сигнала управления сигнал логического О с выхода блока 4 воздействует на логический элемент НЕ 21 и логические элементы 2И-НЕ 32 и 33,

Пусть момент t, окончания сигнала управления с выхода блока 4 совпадает с интервалом проводимости первой группы тиристоров групп встречно-параллельно включенных тиристоров 14. В этом случае в момент tj на входы логического элемента 2И-НЕ 24 воздействуют две логические 1, логический элемент НЕ 26 формирует логическую 1 которая воздействует на логическую память 28. Последняя формирует на выходе сигнал 1, который через логический элемент НЕ 30 воздействует на один из входов логического элемента 2И-НЕ 32. На второй вход логического элемента 2И-НЕ 32 воздействует сигнал логического О с выхода блока 4ь

Сигнал 1 с выхода логического элемента 2И-НЕ 32 воздействует через логический элемент НЕ 34 на один из входов логического элемента 2И-НЕ 36, на второй вход которого воздействует сигнал логического О с выхода блока 7. Логический элемент 2И-НЕ 36 воздействует через логический элемент 38 на вход блока 7, запрещая подачу управлякицих импульсов на тиристоры

первой группы бивентиля.

I

Одновременно в момент tj на один вход логического элемента 2И-НЕ 25 воздействует логическая 1 с выхода логического элемента НЕ 21, а на второй вход - логический О с выхода нуль-органа 20. Логический элемент 2И-НЕ 25, логические элементы 27 и 31 и логическая память 29 формируют на выходе логического элемента НЕ 31 логическую 1, Которая воздействует на один вход логического элемента 2И-НЕ 33, на второй вход которого воздействует сигнал О с выхода блока 4, Сигнал 1 с выхода логического элемента 2И-НЕ через логический элемент НЕ 35, узел 40 воздействует на один из входов логического элемента 2И-НЕ 37, на второй вход которого

нал логической 1 с выхода блока 4. Логический элемент 2И-НЕ 32 формирует сигнал 1, который через логический элемент НЕ 34 воздействует на оди из входов логического элемента 2И-НЕ 36, на второй вход которого воздействует сигнал логической 1 с выхода блока 7, логический элемент

10 2И-НЕ 36 формирует сигнал 1, который через логический элeмeнt НЕ 38 воздействует на блок 7, запрещая подачу управляющих импульсов на тиристоры первой группы групп встречно15 параллельно включенных тиристоров 14. Одновременно в момент t логический элемент 2И-НЕ 25, логические элементы НЕ 27 и 31 и логическая память 29 формируют на выходе логического

20 элемента НЕ 31 сигнал логической 1, который воздействует на один вход логического элемента 2И-НЕ 33, на второй вход которого воздействует сигнал l с выхода блока 4. Быкод25 ной .сигнал О логического элемента 2И-НЕ 33 через логический элемент НЕ 35 и узел 40 воздействует на один вход логического элемента 2И-НЕ 37, на второй вход которого воздейству30 ет сигнал О с выхода блока 8. Выходной сигнал 1 с выхода логического элемента 2И-НЕ 37 через логический элемент НЕ 39 воздействует на вход блока 8, запрещая подачу управляющих

воздействует сигнал О с выхода бло- 35 импульсов на тиристоры второй группы

ка 8 коммутации. Логический элемент 2И-НЕ 37 через логический элемент НЕ 39 воздействует на вход блока коммутации, запрещая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров 14.

В Момент t4 подачи очередного сигнала управления с выхода блока 4 - сигнал логической 1 через логический элемент НЕ 21 воздействует на один из входов логического элемента 2И-НЕ 24 первого блока 22, на второй вход которого воздействует сигнал О с выхода нуль-органа 19. Так как в могрупп встречно-параллельно включенных тиристоров 14 до момента t. В момент времени t блок 8 коммутации формирует на выходе синхронизированный с

40 нулем питающего напряжения сигнал логической 1, который воздействует на второй вход логического элемента 2И-НЕ 37. Последний формирует на выходе сигнал логического О, который

45 через логический элемент НЕ 39 воздействует на блок 8, разрешая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров.

50

В момент t, формирования первого

импульса тока нагрузки 15 нуль-орган

ческой памяти 28 равен О, логический 20 формирует сигнал 1, который воз- элемент 2И-НЕ 24, логические элементы действует на второй вход логической НЕ 26 и 30 и логическая память 28 сво- памяти 28 первого блока 22. Логичес- его состояния и логический элемент 55 память 28 формирует сигнал О, НЕ 30 на выводе формируют сигнал О. Этот сигнал воздействует на один вход логического элемента 2И-НЕ 32, на второй вход которого воздействует сигкоторый через логические элементы НЕ 30, 34 и 38 и логические элементы 2И-НЕ 32 и 36 воздействует на вход блока 7, разрешая подачу управляющих

нал логической 1 с выхода блока 4. Логический элемент 2И-НЕ 32 формирует сигнал 1, который через логический элемент НЕ 34 воздействует на один из входов логического элемента 2И-НЕ 36, на второй вход которого воздействует сигнал логической 1 с выхода блока 7, логический элемент

2И-НЕ 36 формирует сигнал 1, который через логический элeмeнt НЕ 38 воздействует на блок 7, запрещая подачу управляющих импульсов на тиристоры первой группы групп встречнопараллельно включенных тиристоров 14. Одновременно в момент t логический элемент 2И-НЕ 25, логические элементы НЕ 27 и 31 и логическая память 29 формируют на выходе логического

элемента НЕ 31 сигнал логической 1, который воздействует на один вход логического элемента 2И-НЕ 33, на второй вход которого воздействует сигнал l с выхода блока 4. Быкодной .сигнал О логического элемента 2И-НЕ 33 через логический элемент НЕ 35 и узел 40 воздействует на один вход логического элемента 2И-НЕ 37, на второй вход которого воздействует сигнал О с выхода блока 8. Выходной сигнал 1 с выхода логического элемента 2И-НЕ 37 через логический элемент НЕ 39 воздействует на вход блока 8, запрещая подачу управляющих

групп встречно-параллельно включенных тиристоров 14 до момента t. В момент времени t блок 8 коммутации формирует на выходе синхронизированный с

40 нулем питающего напряжения сигнал логической 1, который воздействует на второй вход логического элемента 2И-НЕ 37. Последний формирует на выходе сигнал логического О, который

45 через логический элемент НЕ 39 воздействует на блок 8, разрешая подачу управляющих импульсов на тиристоры второй группы групп встречно-параллельно включенных тиристоров.

50

В момент t, формирования первого

импульса тока нагрузки 15 нуль-орган

20 формирует сигнал 1, который воз- действует на второй вход логической памяти 28 первого блока 22. Логичес- память 28 формирует сигнал О,

который через логические элементы НЕ 30, 34 и 38 и логические элементы 2И-НЕ 32 и 36 воздействует на вход блока 7, разрешая подачу управляющих

713398198

импульсов на тиристоры первой группы ки сигналов управления подсоединен групп встречно-параллельно включенных к первому входу логической памяти, тиристоров 14.выход которой подсоединен через трет ий логический элемент НЕ к первому Формула изобретения входу второго логического элемента

2И-НЕ, вьгход которого подсоединен

Регулируемый преобразователь пе- через четвертый логический элемент ременного напряжения в переменное, НЕ к третьему логическому элементу содержащий две группы встречно-парал- ю 2И-НЕ, выход которого через пятый лельно включенных тиристоров и схему логический элемент НЕ подсоединен к управления, состоящую из последова- входам логических элементов 2И-НЕ пер- тельно включенных задатчика, генера- вого блока коммутации, а выход пер- тора пилообразного напряжения, блока вого блока коммутации подсоединен к развязки каналов управления, двух 15 второму входу третьего логического блоков формирования сигналов управле- элемента 2И-НЕ первого блока формиро- ния, двух блоков коммутации, двух бло- вания задержки сигналов управления, ков формирования синхронизирующих им- выход первого логического элемента пульсов, отличающийся 2И-НЕ второго блока формирования затем, что, с целью повышения надежное- 20 держки сигналов управления подсоеди- ти и исключения высших гармоник в ней к первому входу логической памя- кривой питающего напряжения, введены ти, выход которой подсоединен через блок логики, содержащий трансформатор третий логический элемент НЕ к пер- тока, два диода, два нуль-органа, ло- вому входу второго логического элегический элемент НЕ, первый и второй 25 мента 2И-НЕ, выход которого подсое- блоки формирования задержки сигналов динен через четвертый логический эле- управления, каждый из которых содержит мент НЕ к входу узла гальванической последовательно соединенные первый развязки, выход которого подсоединен логический элемент 2И-НЕ, второй ло- к первому входу третьего логического гический элемент НЕ, логическую па- ЗО элемента 2И-НЕ, второй вход которого мять, третий логический элемент НЕ, подсоединен к выходу второго блока второй логический элемент 2И-НЕ, чет- коммутации, а выход через пятый логи- вертый логический элемент НЕ, третий ческий элемент НЕ к входу второго логический элемент 2И-НЕ, пятый логи- блока коммутации, вторые входы первых ческий элемент НЕ, кроме того, второй с логических элементов 2И-НЕ первого блок формирования задержки сигналов и второго блоков формирования задерж- управления содержит узел гальваничес- ки сигнала управления подсоединены кой развязки, причем вход трансформа- через логический элемент НЕ к выходу тора тока включен в цепь нагрузки, блока развязки каналов управления, один выход через диод и первьй нуль- дд второй вход логической памяти первого орган подсоединен к первому входу пер- блока формирования задержки сигнала вого логического элемента 2И-НЕ пер- управления подсоединен к выходу вто- вого блока формирования задержки сиг- рого нуль-органа, второй вход логичес- налов управления, второй выход транс- кой памяти второго блока формирования форматора тока через второй диод и задержки сигнала управления подсое- второй нуль-орган подсоединен к пер- дршен к выходу первого нуль-органа, вому входу первого логического эле- а вторые входы вторых логических элемента 2И-НЕ второго блока формирова- ментов 2И-НЕ первого и второго блоков ния задержки сигналов управления, вы- формирования задержки сигналов управ- ход первого логического элемента 2И- gQ ления подсоединены к выходу блока НЕ первого блока формирования, задерж- развязки каналов управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод переменного тока | 1987 |

|

SU1508336A1 |

| Преобразователь постоянного напряжения в однофазное переменное с амплитудно-импульсной модуляцией | 1981 |

|

SU997204A1 |

| Регулятор переменного напряжения | 1978 |

|

SU851691A1 |

| Электропривод переменного тока | 1983 |

|

SU1128362A1 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1989 |

|

SU1690137A1 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1987 |

|

SU1554095A1 |

| Электропривод переменного тока | 1986 |

|

SU1517105A1 |

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU968829A1 |

| Электропривод переменного тока | 1987 |

|

SU1517108A1 |

| Мостовой преобразователь постоянного напряжения | 1987 |

|

SU1417138A1 |

-Изобретение относится к электротехнике. Цель изобретения - повышение надежности и исключение высших гармоник в кривой питающего напряжения. Регулирование напряжения осуществляют изменением отношения числа полупериодов сети, при которых на группы встречно-параллельно включенных тиристоров 14 подаются запускающие импульсы к числу полупериодов сети, при которых на выходах блоков 9 и 10 формирования управляющих импульсов запускающие импульсы отсутствуют. Блок логики 13 обеспечивает включение групп встречно-параллельно включенных тиристоров 14 в начале полупериода сетевого напряжения, поля{)- ность которого противоположна полярности последнего полупериода сетевого напряжения в предыдущем интервале проводимости. Это позволяет исключить режим насьпцения трансформатора и вероятность сверхдопустимого тока нагрузки. 3 ил. i (Л С СлЭ со |Х эо

| Регулятор мощности переменного тока | 1972 |

|

SU471578A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США 3925633, кл | |||

| Прибор для записи звуковых волн | 1920 |

|

SU219A1 |

| Регулятор переменного напряжения | 1978 |

|

SU851691A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-09-23—Публикация

1986-01-31—Подача