Изобретение относится к импульсной технике и может быть использовано при проектировании реверсивных счетчиков цифровых вычислительных устройств. Известен реверсивный счетчик импульсов , содержащий входную шину и П разрядов, каждый из которых содержит две шины установки и шесть троичных четыреХБХодовых логических элементов D Недостатком известного устройства является малое быстродействие (500 Гц Известен реверсивный счетчик импульсов, содержащий входную шину, три шины тактового питания и П разрядов, каждый из которых содержит шесть четырехвходовых троичных логических эле ментов и две шины установки, входная шина соединена с первыми входами первого и второго троичных логических эл ментов первого разряда, в каждом разряде выход первого четырехвходового троичного логического элемента соедйней с первыми входами первого троично го логического элемента последующего разряда и третьего троичного логического элемента, выход которого соединен с первым и третьим входами четвертого троичного логического элемента и со вторым, и третьим входами пятого троичного логического элемента, четвертый вход которого соединен с первой шиной установки и с четвертым входом четвертого троичного логического элемента, второй вход которого соединен с первым входом пятого, троичного логического элемента и с выходом шестого четырехвходового троичного логического элемента, первый вход которо го соединен с первым входом второго троичного логического элемента последующего разряда, с четвертым входом третьего троичного логического элемента и с выходом второго четырехвходоВОГ9 троичного логического элемента, четвертый вход которого соединен с соответствующей шиной тактового пита- ния и с четвертым входом первого троичного логического элемента, выход которого соединен с четвертым входом шестого троичного логического элемента, второй и третий входы которого соединены со второй шиной установки, выходы четвертого и пятого четырехвходовых троичных логических элементов

соединены соответственно со вторыми входами первого и второго троичных логических элементов 2 J.

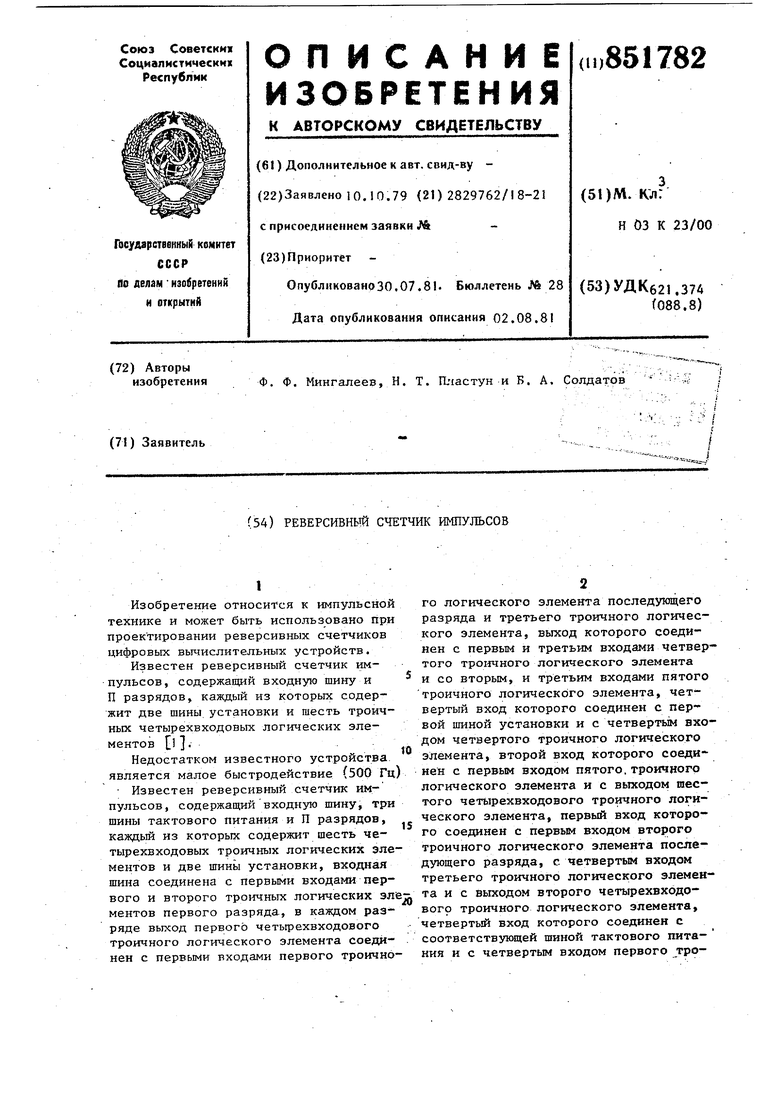

В известном устройстве каждый троичный логический элемент вьтолняет троичные операции, описьгааемые нижеследующей таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик импульсов | 1978 |

|

SU764137A1 |

| Реверсивный п-разрядный счетчик импульсов | 1977 |

|

SU692091A1 |

| Двоичный счетчик импульсов | 1981 |

|

SU1001486A1 |

| Двоичный п-разрядный счетчик импульсов | 1979 |

|

SU782166A1 |

| Троичный реверсивный п-разрядный счетчик импульсов | 1977 |

|

SU733109A1 |

| Троичный реверсивный -разрядныйСчЕТчиК иМпульСОВ | 1979 |

|

SU807492A1 |

| Двоичный п-разрядный счетчик импульсов | 1977 |

|

SU692095A1 |

| Реверсивный счетчик импульсов | 1982 |

|

SU1091347A1 |

| Трехзначный элемент коньюнкции | 1982 |

|

SU1064468A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1405110A1 |

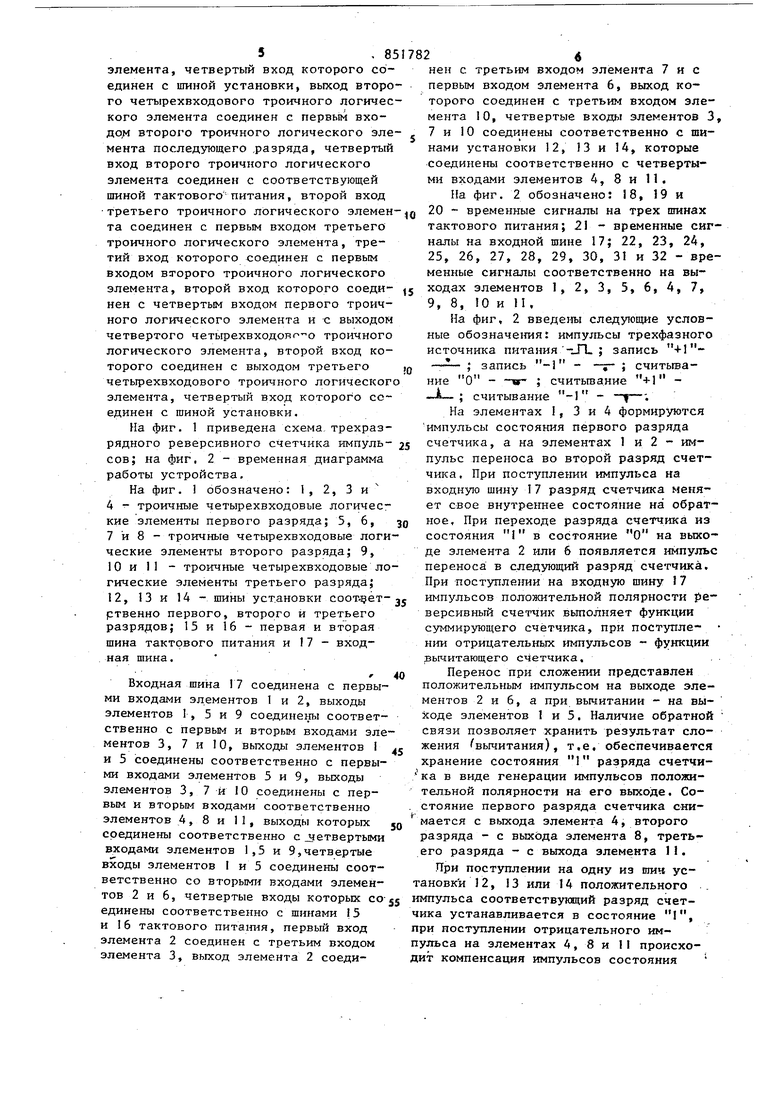

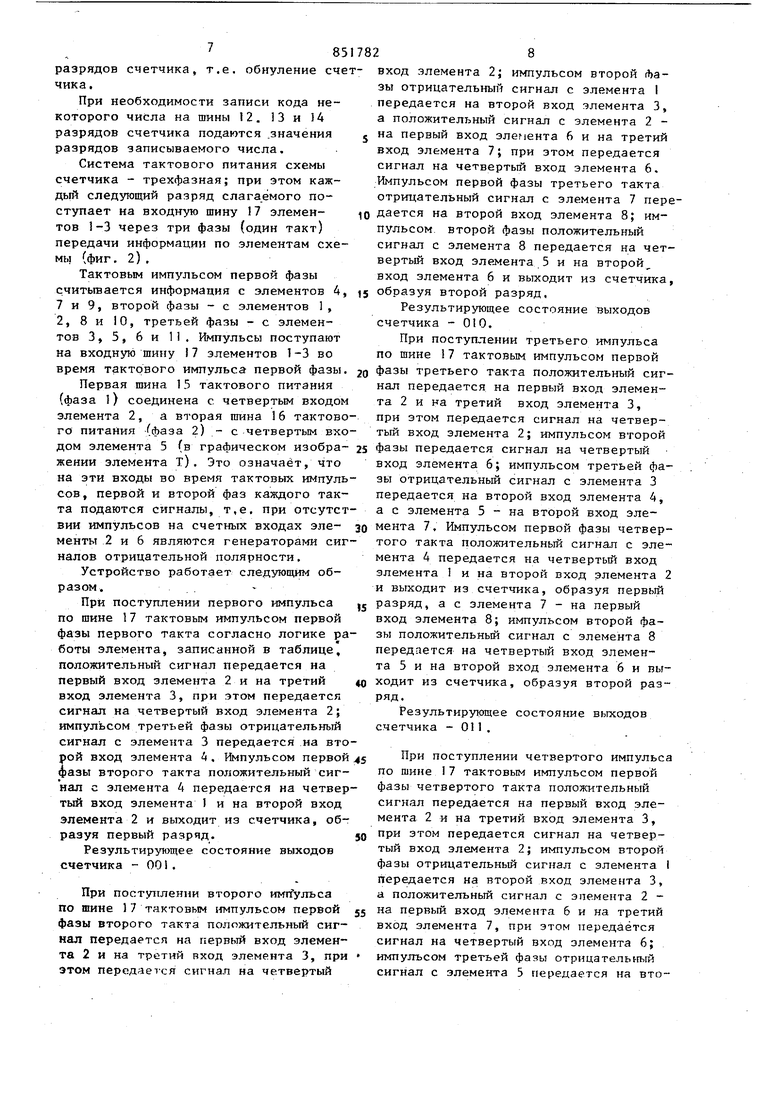

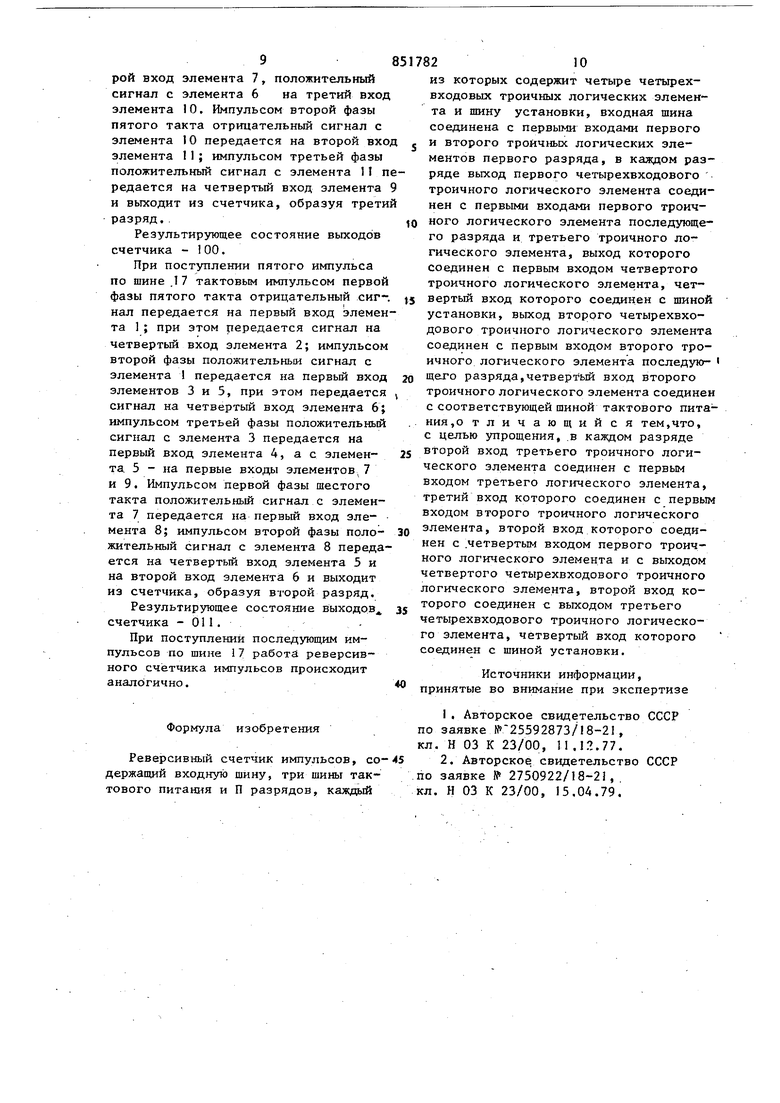

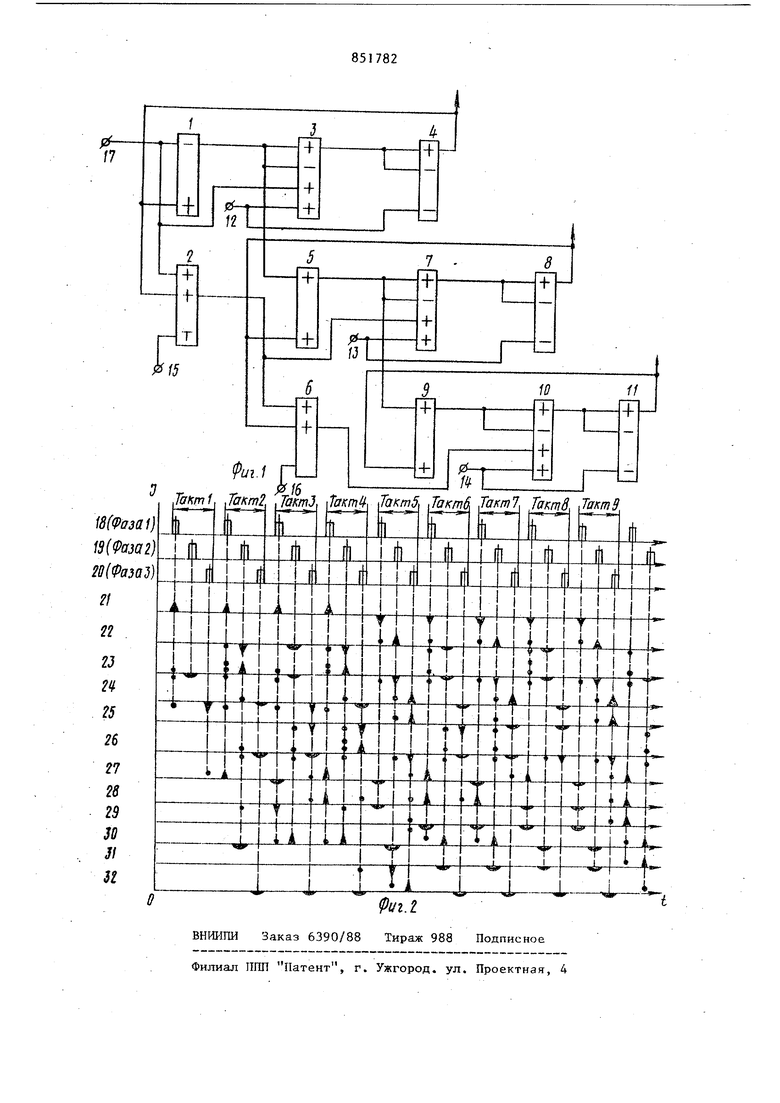

+ 1 Указанные троичные операции образуют функционально полную систему логических функций, В известном устройстве сигнал пере носа в последующий разряд счетчика формируется за одну фазу передачи информации по троичным логическим элементам разряда. Недостатком известного устройства является его относительная сложность Цель изобретения - упрощение устройства. Для достижения поставленной цели в реверсивном сметчике, содержащем входную шину, три шины тактового питания и П разрядов, каждый из которых содержит четыре четырехвходовых троичных логических элемента и шину установки, входная шина соединена с первыми входами первого и второго троичных логических элементов первого разряда, в каждом разряде выход первого четырехвходового троичного логического элемента соединен с первыми входами первого троичного логического элемента последующего разряда и третьего троичного логического элемента, выход которого соединен с первым входом четвертого троичного логического элемента, четвертый вход которого со единен с шиной установки, выход второ го четырехвходового троичного логиче кого элемента соединен с первым входо 1 второго троичного логического эле мента последующего разряда, четвертый вход второго троичного логического элемента соединен с соответствующей шиной тактового питания, второй вход третьего троичного логического элемен та соединен с первым входом третьего троичного логического элемента, третий вход которого соединен с первым входом второго троичного логического элемента, второй вход которого соединен с четвертым входом первого троичного логического элемента и с выходом четвертого четырехвходов о троичного логического элемента, второй вход которого соединен с выходом третьего четырехвходового троичного логическог элемента, четвертый вход которог о соединен с шиной установки. На фиг. 1 приведена схема, трехразрядного реверсивного сЧетчика импульсов; на фиг. 2 - временная диаграмма работы устройства. На фиг. обозначено: 1, 2, 3 и 4 - троичные четырехвходовые логические элементы первого разряда; 5, 6, 7 и 8 - троичные четырехвходовые логи ческие элементы второго разряда; 9, 10 и 11 - троичные четырехвходовые ло гические элементы третьего разряда; 12, 13 и 14 - шины установки соот-цетртвенно первого, второго и третьего разрядов; 15 и 16 - первая и вторая шина тактового питания и I7 - входная шина. Входная шина 17 соединена с первыми входами элементов 1 и 2, выходы элементов 1, 5 и 9 соединен соответственно с первым и вторым входами эле ментов 3, 7 и 10, выходы элементов I и 5 соединены соответственно с первыми входами элементов 5 и 9, выходы элементов 3, 7 и 10 соединены с первым и вторым входами соответственно элементов 4, 8 и 11, выходы которых соединены соответственно с „четвертыми входами элементов 1,5 и 9,четвертые входы элементов I и 5 соединены соответственно со BTopbiMii входами элементов 2 и 6, четвертые входы которых соединены соответственно с шинами 15 и 16 тактового питат1Я, первый вход элемента 2 соединен с третьим входом элемента 3, выход элемента 2 соединен с третьим входом элемента 7 и с первым входом элемента 6, выход которого соединен с третьим входом элемента 10, четвертые входы элементов 3, 7 и 10 соединены соответственно с шинами установки 12, 13 и 14, которые соединены соответственно с четвертыми входами элементов 4, 8 и 11. На фиг. 2 обозначено: 18, 19 и 20 временные сигналы на трех пшнах тактового питания; 21 - временные сигналы на входной шине 17; 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 и 32 - временнь е сигналы соответственно на выходах элементов 1, 2, 3, 5, 6, 4, 7, 9, 8, 10 и И, На фиг, 2 введены следующие условные обозначения: импульсы трехфазного источника питания-JTL ; запись ; запись -1 ; считьгеа +1 ; считьгаание считывание -1 - -f-; элементах I, 3 и 4 формируются импульсы состояния первого разряда счетчика, а на элементах 1 и 2 - импульс переноса во второй разряд счетчика , При поступлении импульса на входную шину 17 разряд счетчика меняет свое внутреннее состояние на обратное. При переходе разряда счетчика из состояния 1 в состояние О на выходе элемента 2 или 6 появляется импульс переноса в следующий разряд счетчика. При поступлении на входную шину 17 и тульсов положительной полярности реверсивный счетчик вьтолняет функции суммирующего счётчика, при поступле НИИ отрицательных импульсов - функции рычитающего счетчика. Перенос при сложении представлен положительньм импульсом на выходе элементов 2 и 6, а при вычитании - на выходе элементов 1 и 5. Наличие обратной связи позволяет хранить результат слоения / вычитания), т.е. обеспечивается ранение состояния 1 разряда счетчиа в виде генерации импульсов положиельной полярности на его выходе. Сотояние первого разряда счетчика сниается с выхода элемента 4, второго азряда - с выхода элемента 8, третьго разряда - с выхода элемента П. При поступлении на одну из шич усновки 12, 13 или 14 положительного . пульса соответствующий разряд счетка устанавливается в состояние 1, и поступлении отрицательного имльса на элементах 4, 8 и П происхот компенсация импульсов состояния разрядов счетчика, т.е. обнуление При необходимости записи кода некоторого числа на шины 12, 3 и 14 разрядов счетчика подаются ,значения разрядов записываемого числа. Система тактового питания схемы счетчика - трехфазная; при этом каждьй следующий разряд слагаемого поступает на входную шину 17 элементов 1-3 через три фазы (один такт) передачи информации по элементам схе мы (фиг, 2). Тактовым импульсом первой фазы считьгеается информация с элементов

7 и 9, второй фазы - с элементов 1, 2, 8 и 10, третьей фазы - с элементов 3, 5, 6 и 11 . Импульсы поступают на входную шину 17 элементов 1-3 во

время тактового импульса первой фазы, о Фазы третьего такта положительный сигПервая шина 15 тактового питания нал передается на первый вход элемен{фаза 1) соединена с четвертым входом та 2 и на третий вход элемента 3, элемента 2, а вторая шина 16 тактово- при этом передается сигнал на четверго питания (фаза 2) - с четвертым вхо- тый вход элемента 2; импульсом второй дом элемента 5 (в графическом изобра- 25 Фазы передается сигнал на четвертый женин элемента Т). Это означает, что вход элемента 6; импульсом третьей фана эти входы во время тактовых импульсов , первой и второй фаз каждого такта подаются сигналы, т,е. при отсутствии импульсов на счетных входах элементы 2 и 6 являются генераторами сиг налов отрицательной полярности, Устройство работает следующим образом.. При поступлении первого импульса по шине 17 тактовым импульсом первой фазы первого такта согласно логике ра боты элемента, записанной в таблице, положительный сигнал передается на первый вход элемента 2 и на третий вход элемента 3, при этом передается сигнал на четвертый вход элемента 2; импульсом третьей фазы отрицательный сигнал с элемента 3 передается на вто рой вход элемента 4. Импульсом первой фазы второго такта положительный сигнал с элемента 4 передается на четвер тый вход элемента 1 и на второй вход элемента 2 и выходит из счетчика, образуя первый разряд. Результирующее состояние выходов счетчика - 001. При поступлении второго иигГульса по шине 17 тактовым импульсом первой фазы второго такта положительный сигнал передается на первый вход элемента 2 и на третий вход элемента 3, при этом передается сигнал на четвертый

Результирующее состояние выходов счетчика - 010.

При поступлении третьего импульса по шине 17 тактовым импульсом первой

зы отрицательный сигнал с элемента 3 передается на второй вход элемента 4, а с элемента 5 - на второй вход эле851782Всчет- вход элемента 2; итчпульсом второй tbaзы отрицательный сигнал с элемента I передается на второй вход элемента 3, а положительный сигнал с элемента 2 на первый вход элемента 6 и на третий вход элемента 7; при этом передается сигнал на четвертый вход элемента 6. Импульсом первой фазы третьего такта отрицательный сигнал с элемента 7 передается на второй вход элемента 8; импульсом второй фазы положительный сигнал с элемента 8 передается на четвертый вход элемента 5 и на второй, вход элемента 6 и выходит из счетчика, образуя второй разряд. мента 7. Импульсом первой фазы четвертого такта положительный сигнал с элемента 4 передается на четвертый вход элемента 1 и на второй вход элемента 2 и выходит из счетчика, образуя первый разряд, а с элемента 7 - на первый вход элемента 8; импульсом второй фазы положительный сигнал с элемента 8 передается на четвертый вход элемента 5 и на второй вход элемента 6 и выходит из счетчика, образуя второй разряд. Результирующее состояние выходов счетчика -011. При поступлении четвертого импульса по шине 17 тактовым импульсом первой фазы четвертого такта положительный сигнал передается на первый вход элемента 2 и на третий вход элемента 3, при этом передается сигнал на четвертый вход элемента 2; импульсом второй фазы отрицательный сигнал с элемента I передается на второй вход элемента 3, а положительный сигнал с элемента 2 на первый вход элемента 6 и на третий вход элемента 7, при этом передаётся сигнал на четвертый вход элемента 6; импульсом третьей фазы отрицатель}гый сигнал с элемента 5 передается на второй вход элемента 7, положительный сигнал с элемента 6 на третий вход элемента 10. Импульсом второй фазы пятого такта отрицательный сигнал с элемента 10 передается на второй вхо элемента 11; импульсом третьей фазы положительный сигнал с элемента 1I п редается на четвертый вход элемента и выходит из счетчика, образуя трети разряд. Результирующее состояние выходов счетчика - 100. При поступлении пятого импульса по шине .17 тактовым импульсом первой фазы пятого такта отрицательный сигнал передается на первый вход элемен та 1; при этом передается сигнал на четвертый вход элемента 2; импульсом второй фазы положительный сигнал с элемента 1 передается на первый вход элементов 3 и 5, при этом передается сигнал на четвертый вход элемента 6; импульсом третьей фазы положительньй сигнал с элемента 3 передается на первый вход элемента 4, ас элемента. 5 - на первые входы элементов. 7 и 9. Импульсом первой фазы шестого такта положительный сигнал с элемента 7 передается на первый вход злемента 8; импульсом второй фазы положительный сигнал с элемента 8 переда ется на четвертый вход элемента 5 и на второй вход элемента 6 и выходит из счетчика, образуя второй разряд. Результирующее состояние выходов счетчика -011. При поступлений последующим импульсов по шине 17 работа реверсивного счётчика импульсов происходит аналогично. Формула изобретения Реверсивный счетчик импульсов, со держащий входную шину, три шины тактового питания и П разрядов, каждый 8210 из которых содержит четыре четырехвходовых троичных логических элемента и шину установки, входная шина соединена с первыми входами первого и второго троичных логических элементов первого разряда, в каждом разряде выход первого четырехвходового троичного логического элемента соединен с первыми входами первого троичного логического элемента последующего разряда и третьего троичного логического элемента, выход которого соединен с первым входом четвертого троичного логического элемента, четвертый вход которого соединен с шиной установки, выход второго четырехвходового троичного логического элемента соединен с первым входом второго троичного логического элемента последующего разряда,четвертый вход второго троичного логического элемента соединен с соответствующей шиной тактового питания,о тличающийся тем,что, с целью упрощения, .в каждом разряде второй вход третьего троичного логического элемента соединен с первым входом третьего логического элемента, третий вход которого соединен с первым входом второго троичного логического элемента, второй вход которого соединен с .четвертым входом первого троичного логического элемента и с выходом четвертого четырехвходового троичного логического элемента, второй вход которого соединен с выходом третьего четырехвходового троичного логического элемента, четвертый вход которого соединен с шиной установки. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР о заявке №25592873/18-21, л. Н 03 К 23/00, 11.12.77. 2.Авторское свидетельство СССР о заявке № 2750922/18-21,. л. Н 03 К 23/00, 15.04.79.

Авторы

Даты

1981-07-30—Публикация

1979-10-10—Подача