(5) двоичный СЧЕТЧИК ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный п-разрядный счетчик импульсов | 1979 |

|

SU782166A1 |

| Реверсивный счетчик импульсов | 1979 |

|

SU851782A1 |

| Двоичный п-разрядный счетчик импульсов | 1977 |

|

SU692095A1 |

| Реверсивный счетчик импульсов | 1978 |

|

SU764137A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Реверсивный п-разрядный счетчик импульсов | 1977 |

|

SU692091A1 |

| Трехзначный элемент коньюнкции | 1982 |

|

SU1064468A1 |

| Троичный реверсивный п-разрядный счетчик импульсов | 1977 |

|

SU733109A1 |

| Трехзначный элемент конъюнкции | 1981 |

|

SU993478A1 |

| Двоичный п-разрядный счетчик импульсов | 1976 |

|

SU678675A1 |

1

Изобретение относится к импульсной технике и может быть использовано при проектировании счетчиков цифровых вычислительных устройств.

Известен двоичный счетчик импульсов, выполненный на троичных логических элементах ЗОднако известный двоичный счетчик импульсов имеет сложную реализацию, так как каждый разряд счетчика выполнен на трех троичных логических элементах.

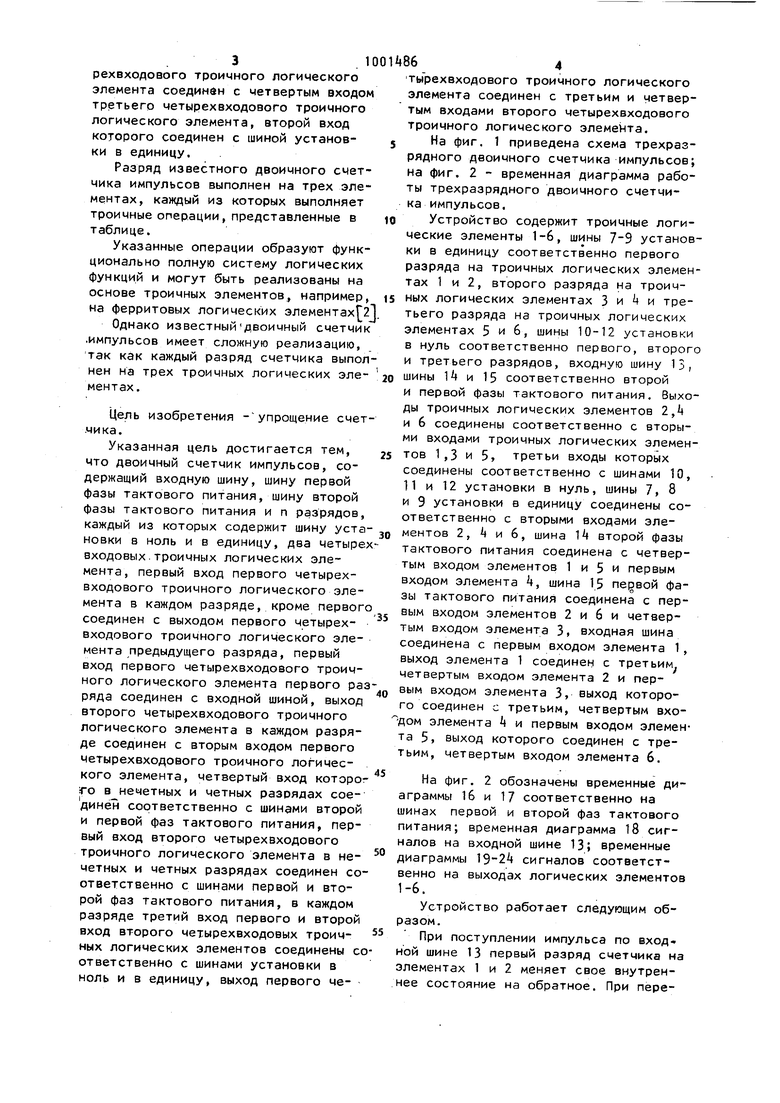

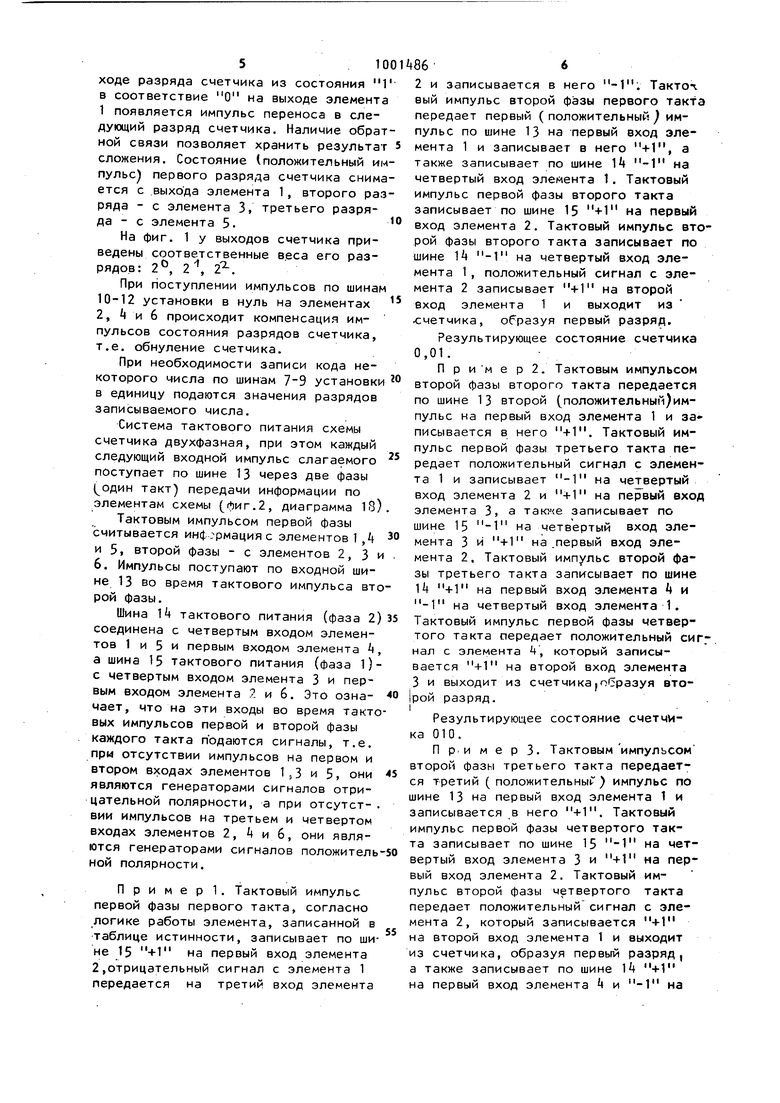

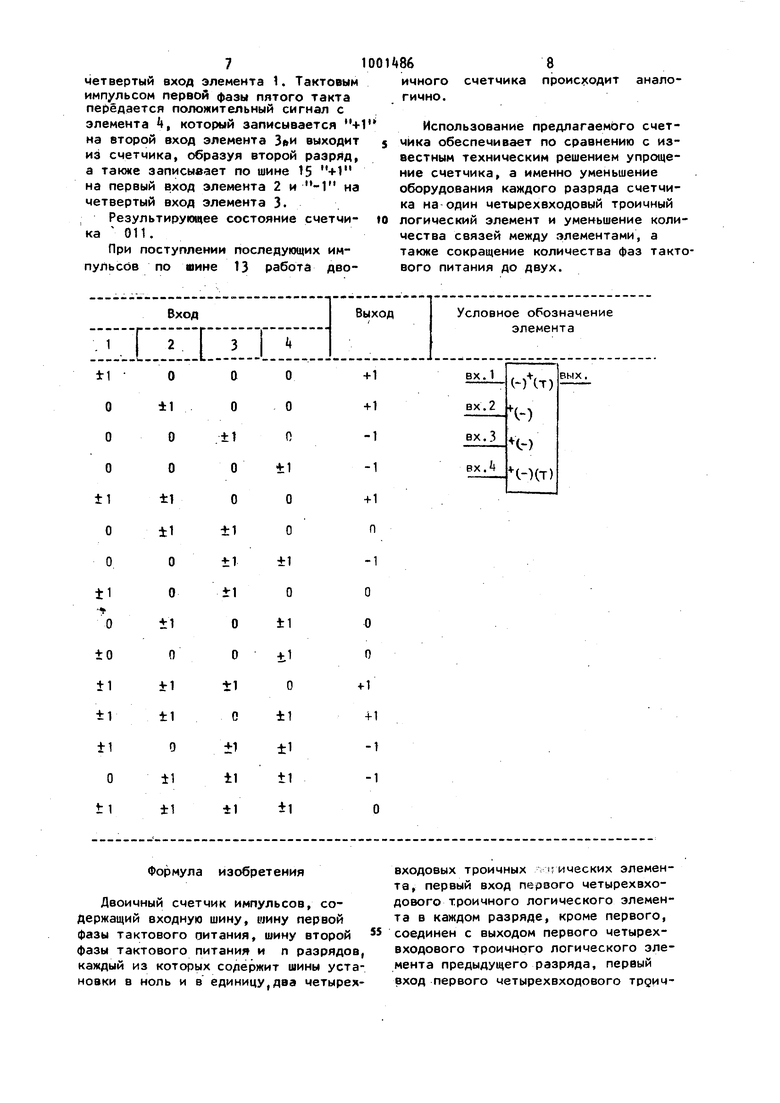

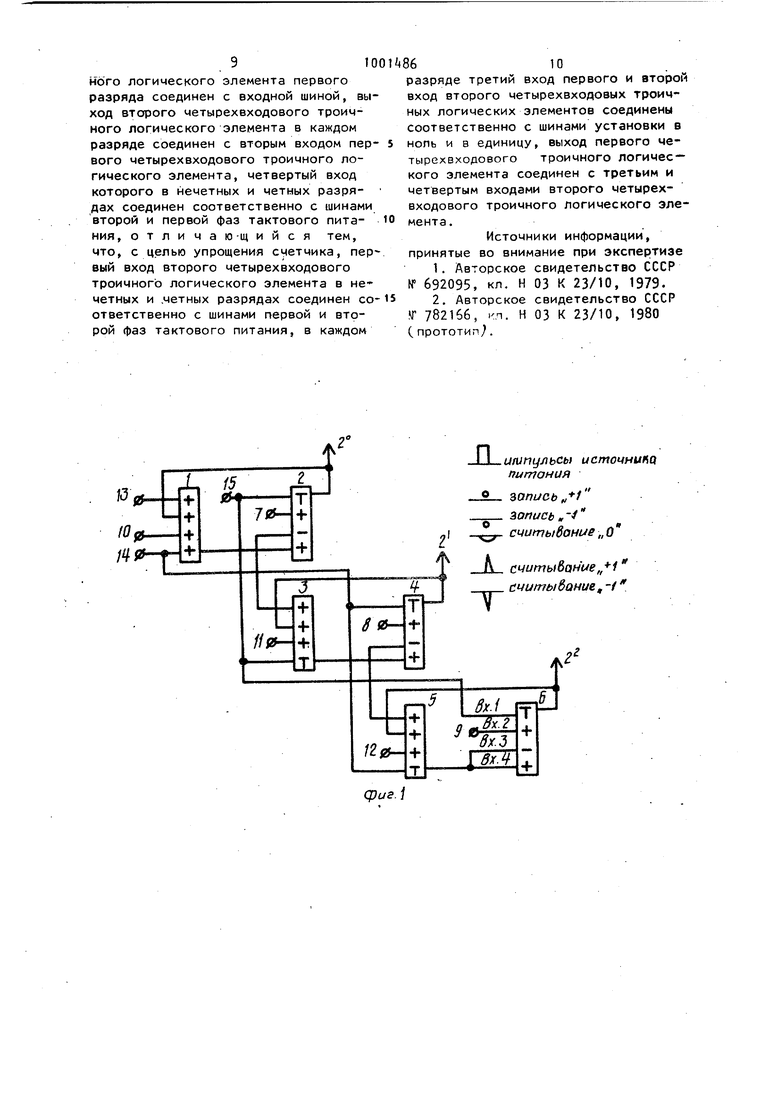

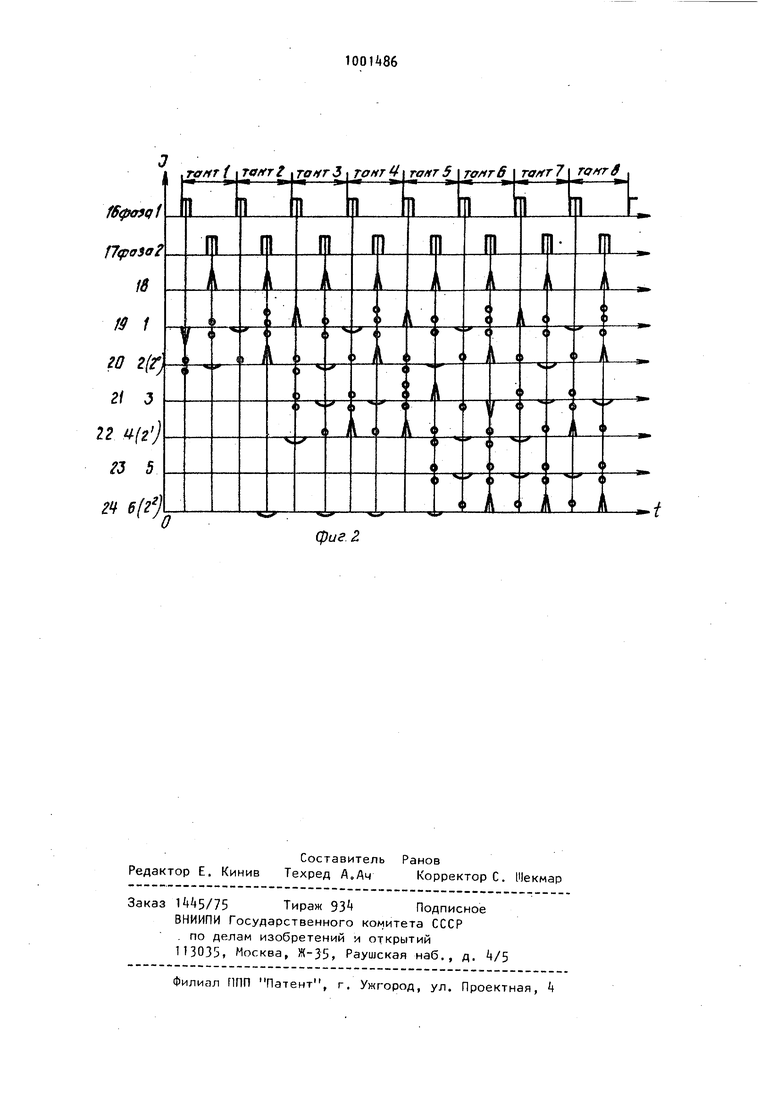

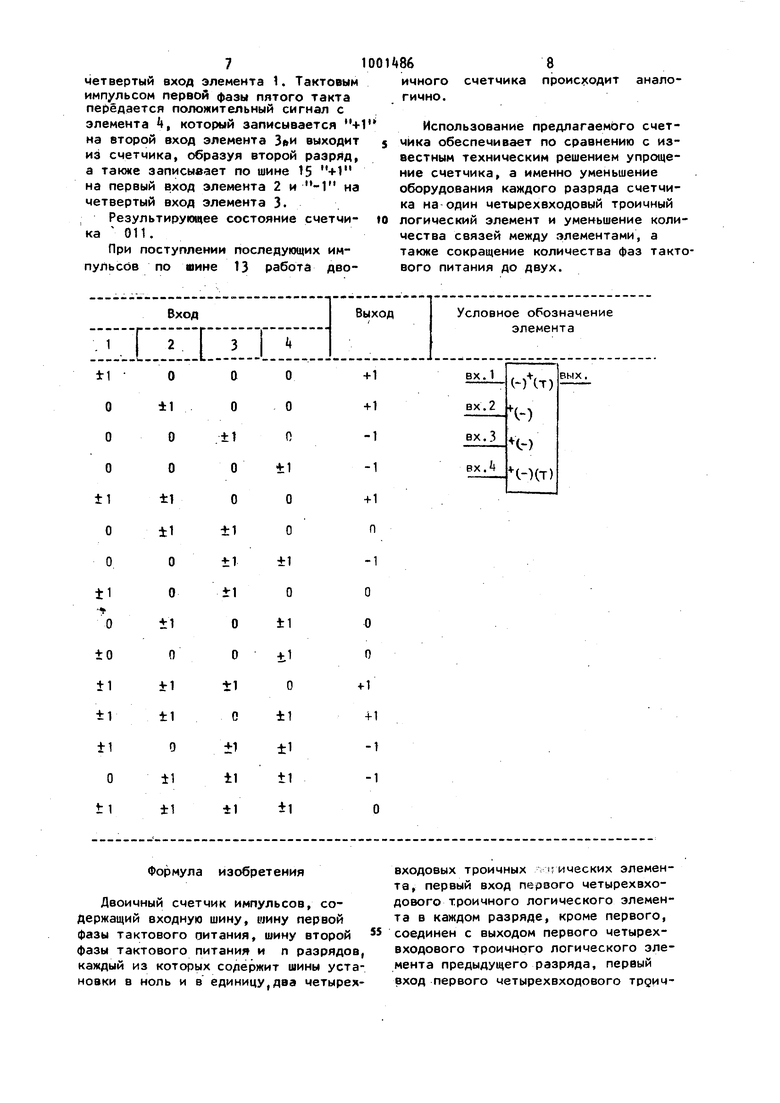

Известен двоичный счетчик импульсов, содержащий входную шину, шину .первой фазы тактового питания, шину второй фазы тактового питания и п разрядов, каждый из которых содержит шины установки в ноль и в единицу, три четырехвходовых троичных логических элемента, первый вход первого четырехвходового троичного логического элемента в каждом разряде, кроме первого, соединен с выходом первого четырехвходового троич ного логического элемента предыдуще-го разряда, первый вход первого четырехвходового троичного логического элемента первого разряда соединен с входной шиной, выход второго четырехвходового троичного логического элемента в каждом разряде соединен с вторым входом первого четырехвходового троичного логического элемента, четвертый вход которого в нечетных и четных разрядах соединен соответственно с шинами второй и первой фаз тактового питания, в каждом разряде выход второго четырехвходового троичного логического эле-. мента соединен с первым входом третьего четырехвходсвого троичного логического элемента, выход которого соединен с первым и вторым входами второго четырехвходового троичного логического элемента, четвертый вход которого соединен с шиной установки в ноль, первый вход первого четырехвходового троичного логического элемента соединен с четвертым входом третьего четырехвходового троичного логического элемента, второй вход которого соединен с шиной установки в единицу. Разряд известного двоичного счетчика импульсов выполнен на трех элементах, каждый из которых выполняет троичные операции, представленные в таблице. Указанные операции образуют функционально полную систему логических функций и могут быть реализованы на основе троичных элементов, например, на ферритовых логических элементах| 2 Однако известныйдвоичный счетчик .импульсов имеет сложную реализацию, так как каждый разряд счетчика выпол нен на трех троичных логических элементах. Цель изобретения -упрощение счет .чи ка. Указанная цель достигается тем, что двоичный счетчик импульсов, содержащий входную шину, шину первой фазы тактового питания, шину второй фазы тактового питания и п разрядов. каждый из которых содержит шину уста новки в ноль и в единицу, два четыре входовых троичных логических элемента, первый вход первого четырехвходового троичного логического элемента в каждом разряде, кроме первог соединен с выходом первого четырехвходового троичного логического элемента предыдущего разряда, первый вход первого четырехвходового троичного логического элемента первого ра ряда соединен с входной шиной, выход второго четырехвходового троичного логического элемента в каждом разряде соединен с вторым входом первого четырехвходового троичного логического элемента, четвертый вход которо го в нечетных и четных разрядах соединён соответственно с шинами второй и первой фаз тактового питания, первый вход второго четырехвходового троичного логического элемента в нечетных и четных разрядах соединен со ответственно с шинами первой и второй фаз тактового питания, в каждом разряде третий вход первого и второй вход второго четырехвходовых троичных логических элементов соединены с ответственно с шинами установки в ноль и в единицу, выход первого четырехвходового троичного логического элемента соединен с третьим и четвертым входами второго четырехвходового троичного логического элемента. На фиг. 1 приведена схема трехразрядного двоичного счетчика импульсов; на фиг. 2 - временная диаграмма работы трехразрядного двоичного счетчика импульсов, Устройство содержит троичные логические элементы 1-6, шины 7-9 установки в единицу соответственно первого разряда на троичных логических элементах 1 и 2, второго разряда на троичных логических элементах 3 и 4 и третьего разряда на троичных логических элементах 5 и 6, шины 10-12 установки в нуль соответственно первого, второго и третьего разрядов, входную шину 13, шины I и 15 соответственно второй и первой фазы тактового питания. Выходы троичных логических элементов 2,А и 6 соединены соответственно с вторыми входами троичных логических элементов 1,3 и 5, третьи входы которых соединены соответственно с шинами 10, 11 и 12 установки в нуль, шины 7, 8 и 9 установки в единицу соединены соответственно с вторыми входами элементов 2, 4 и 6, шина 14 второй фазы тактового питания соединена с четвертым входом элементов 1 и 5 и первым входом элемента k, шина 15 первой фазы тактового питания соединена с первым входом элементов 2 и 6 и четвертым входом элемента 3, входная шина соединена с первым входом элемента 1, выход элемента 1 соединен с третьим четвертым входом элемента 2 и первым входом элемента 3, выход которого соединен с третьим, четвертым входом элемента Ц и первым входом элемента 5, выход которого соединен с третьим, четвертым входом элемента 6. На фиг. 2 обозначены временные диаграммы 16 и 17 соответственно на шинах первой и второй фаз тактового питания; временная диаграмма 18 си|- налов на входной шине 13; временные диаграммы сигналов соответственно на выходах логических элементов 1-6. Устройство работает следующим образом. При поступлении импульса по входной шине 13 первый разряд счетчика на элементах 1 и 2 меняет свое внутреннее состояние на обратное. При переходе разряда счетчика из состояния 1 в соответствие О на выходе элемента 1 появляется импульс переноса в следующий разряд счетчика. Наличие обратной связи позволяет хранить результат 5 сложения. Состояние (положительный импульс первого разряда счетчика снимается с .выхода элемента 1, второго разряда - с элемента 3, третьего разряда - с элемента 5.

На фиг. 1 у выходов счетчика приведены соответственные в.еса его разрядов: 2°, 2 -Р-,

При Ноступлении импульсов по шинам 10-12 установки в нуль на элементах 2, i и 6 происходит компенсация импульсов состояния разрядов счетчика, т.е. обнуление счетчика.

При необходимости записи кода некоторого числа по шинам 7-9 установки в единицу подаются значения разрядов записываемого числа.

Система тактового питания схемы счетчика двухфазная, при этом каждый следующий входной импульс слагаемого поступает по шине 13 через две фазы (один такт) передачи информации по элементам схемы (Лиг.2, диаграмма 18).

Тактовым импульсом первой фазы считывается информация с элементов 1 , 3° и 5, второй фазы - с эле;ментов 2, 3 и , 6. Импульсы поступают по входной шине 13 во время тактового импульса второй фазы.

Шина Н тактового питания (фаза 2)35 соединена с четвертым входом элементов 1 и 5 и первым входом элемента k , а шина 15 тактового питания (фаза 1)с четвертым входом элемента 3 и первым входом элемента 2 и 6. Это озна- о чает, что на эти входы во время тактовых импульсов первой и второй фазы каждого такта подаются сигналы, т.е. при отсутствии импульсов на первом и втором входах элементов 1,3 и 5, они 5 являются генераторами сигналов отрицательной полярности, а при отсутст-. ВИИ импульсов на третьем и четвертом входах элементов 2, k и 6, они являются генераторами сигналов положитель-50 ной полярности.

П р и м е р 1. Тактовый импульс первой фазы первого такта, согласно логике работы элемента, записанной в таблице истинности, записывает по шине 15 +1 на первый вход элемента 2,отрицательный сигнал с элемента 1 передается на третий вход элемента

2и записывается в него -1. Такто-. вый импульс второй фазы первого такт передает первый (положительный ) импульс по шине 13 на первый вход элемента 1 и записывает в него +1, а также записывает по шине Т -1 на четвертый вход элемента 1. Тактовый импульс первой фазы второго такта записывает по шине 15 +1 на первый вход элемента 2. Тактовый импульс втрой фазы второго такта записывает по шине 1 1-1 I на четвертый вход элемента 1 , положительный сигнал с элемента 2 записывает +1 на второй Вход элемента 1 и выходит из счетчика, образуя первый разряд.

Результирующее состояние счетчика 0,01.

П р им е р 2. Тактовым импульсом второй фазы второго такта передается по шине 13 второй (положительный)импульс на первый вход элемента 1 и за писывается в него +1. Тактовый импульс первой фазы третьего такта передает положительный сигнал с элемента 1 и записывает -1 на четвертый вход элемента 2 и +1 на первый вход элемента 3, а также записывает по шине 15 -1 на четвертый вход элемента 3 и +1 на .первый вход элемента 2, Тактовый импульс второй фазы третьего такта записывает по шине k + на первый вход элемента Ц и -1 на четвертый вход элемента 1. Тактовый импульс первой фазы четвертого такта передает положительный синал с элемента k, который записывается +1 на второй вход элемента

3и выходит из счетчика(Образуя второй разряд.

Результирующее состояние счетчика 010.

П р.и м е р 3. Тактовымимпульсом второй фазы третьего такта передается третий ( положительныр ) импульс по шине 13 на первый вход элемента 1 и записывается ,в него +1. Тактовый импульс первой фазы четвертого такта записывает по шине 15 -1 на четвертый вход элемента 3 и +1 на первый вход элемента 2. Тактовый импульс второй фазы четвертого такта передает положительный сигнал с элемента 2, который записывается +1 на второй вход элемента 1 и выходит из счетчика, образуя первьт разряд, а также записывает по шине }k +1 на первый вход элемента и -1 на

7 1001i 868

четвертый вход элемента 1. Тактовымичного счетчика происходит анагоимпульсом первой фазы пятого тактагично. Передается положительный сигнал с

элемента k, который записывается Ч Использование предлагаемого счетна второй вход элемента Зли выходитs чика обеспечивает по сравнению с изиз счетчика, образуя второй разряд,вестным техническим решением упрощеа также записывает по шине 15 счетчика, а именно уменьшение

на первый вход элемента 2 и -1 наоборудования каждого разряда счетчичетвертый вход элемента 3. .ка на один четырехвходовый троичный

Результирующее состояние счетчи-to логический элемент и уменьшение коли э 011.чества связей между элементами, а

При поступлении последующих им-также сокращение количества фаз тактопульсов по мине 13 работй дво-вого питания до двух.

Формула изобретения

Двоичный счетчик импульсов, содержащий входную шину, шину первой фазы тактового питания, шину второй фазы тактового питания и л разрядов, каждый из которых содержит шины установки в ноль и в единицуJдва четырехвходовых троичных иических элемента, первый вход первого четырехвходового троичного логического элемента в каждом разряде, кроме первого, соединен с выходом первого четырехвходового троичного логического элемента предыдущего разряда, первый вход первого четырехвходового трдичного логического элемента первого разряда соединен с входной шиной, выход второго метырехвходового троичного логического элемента в каждом разряде соединен с вторым входом первого четырехвходового троичного логического элемента, четвертый вход которого в нечетных и четных разрядах соединен соответственно с шинами второй и первой фаз тактового питания, отличаю-щийся тем, что, с целью упрощения сцетчика, первый вход второго четырехвходового троичного логического элемента в нечетных и .четных разрядах соединен соответственно с шинами первой и второй фаз тактового питания, в каждом 10 610 разряде третий вход первого и второй вход второго четырехвходовых троичных логических элементов соединены соответственно с шинами установки в ноль и в единицу, выход первого метырехвходового троичного логического элемента соединен с третьим и четвертым входами второго четырехвходового троичного логического элемента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 692095, кл, Н 03 К 23/10, 1979. 2.Авторское свидетельство СССР .Г 782166, кл. Н 03 К 23/10, 1980 (прототип.

г

/5 /гн

Т

70//0JL

иfUпульсы источника Питания

запись t

запись „4 считывание „о

f

ж

- & считы&(зные,,1 йчитыЬаниг -1

04

.г

8х.

Ж7

9 л x.J

ОгТ

Р

q)us.i

П(роЗо

18 IS 1

(II

б(г)

0

фие2 гамт i fOffr / I TOftr 31 тант 5 таff т 7 TerffrS кУ м ill ll ПУ :, v b У ,

Авторы

Даты

1983-02-28—Публикация

1981-09-15—Подача