Цель иэобретения-расширение функцион 1льных возможностей путем повыения равномерности следования выходных импульсов.

Поставленная цель достигается тем, то в делитель частоты следования мпульсов с переменным дробным коэфициентом деления, содержащий два счетчика импульсов, информационные входы которых подключены к соответствующим установочным шинам, выход первого счетчика импульсов подключен его установочному входу, первому входу формирователя узкого строба и счетному входу второго счетчика импульсов, установочный вход которого соединен с его первым выходом и первым входом формирователя широкого строба, второй вход которого-подключен к выходу дшиифратора, информационный вход которого соединен со вторым выходом первого счетчика импульсов, а стробирукяций вход - с первь9м выходом фазосдвигакяцей цепи, вход которой соединен с вторым входом формирователя узкого строба и первым входом элемента ИЛИ, а второй выход фазосдвигающей цепи и выход формирователя узкого строба соединены соответственно с первым и вторым входами элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого подключен к счетному входу первого счетчика импульсов, введены коммутатор и формирователь переменного строба, первый и второй входы которого соединены соответственно с выходом формирователя широкого строба и выходом первого счетчика импульсов, а первый и второй выходы - с первым и вторым входами коммутатора, третий вход которого соединен с шиной управления, авыход с третьим входом элемента И.

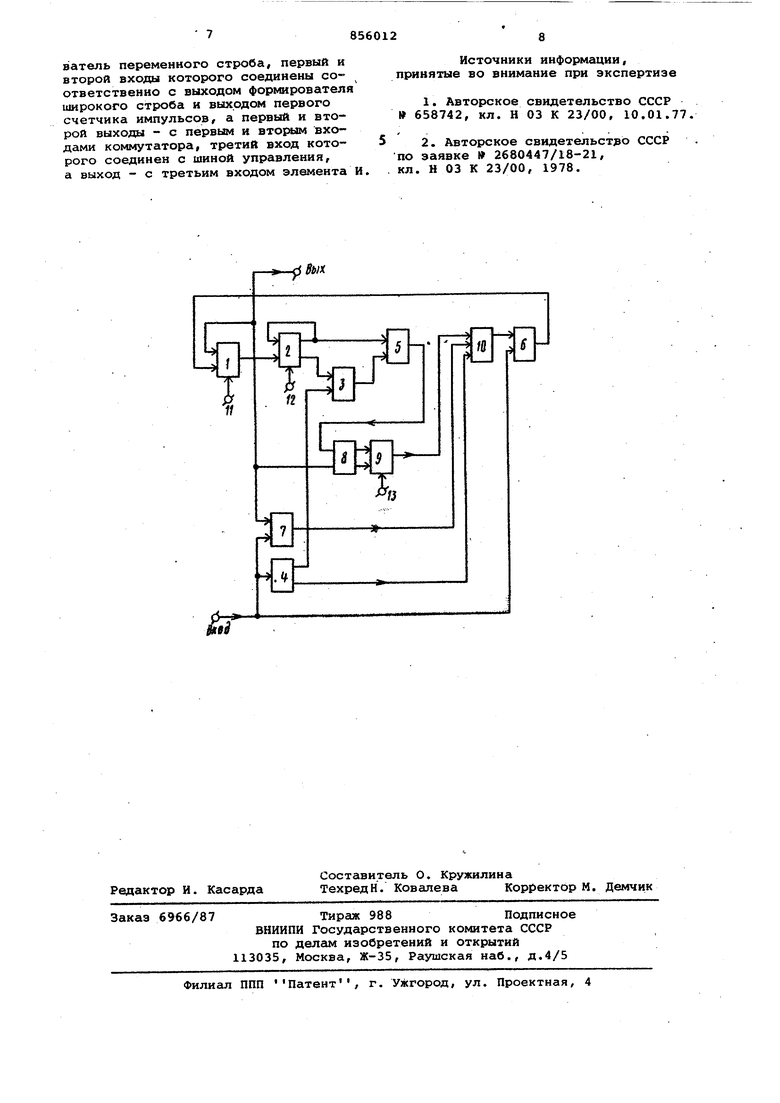

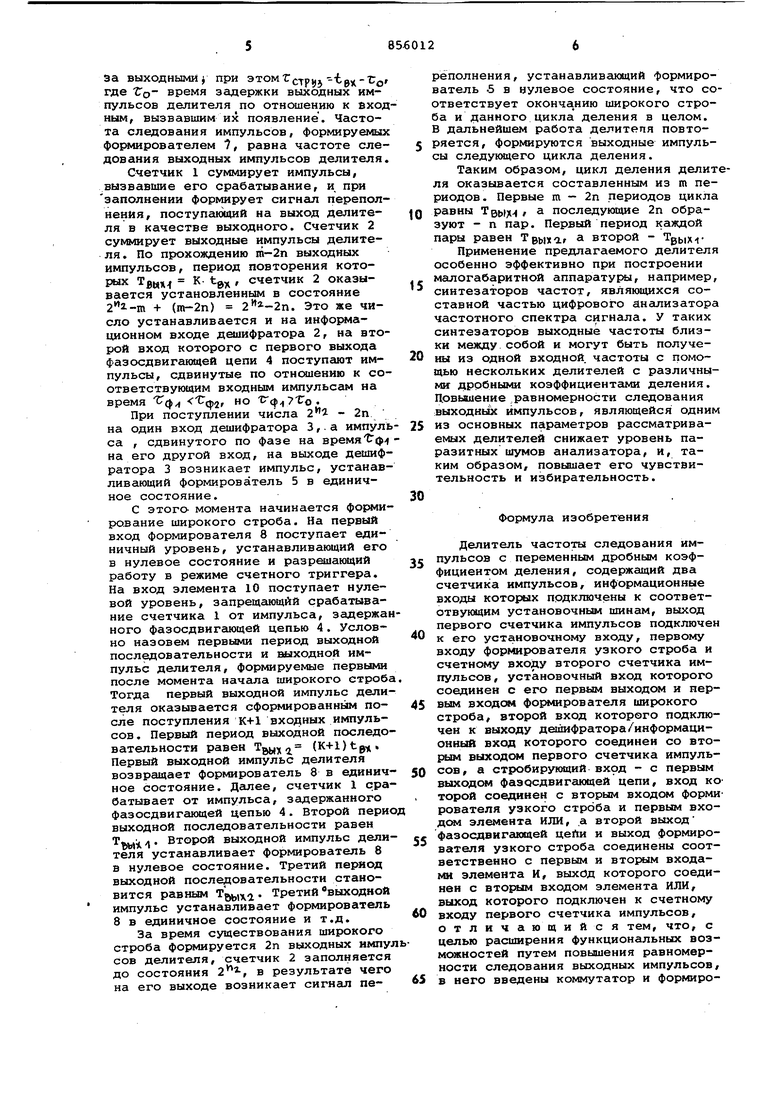

На чертеже представлена структурная схема устройства.

Устройство содержит счетчик 1 входных импульсов, счетчик 2 выходных импульсов, дешифратор 3, фазосдвигающую цепь 4, формирователь 5 ишрокого строба, элемент 6 ИЛИ, формирователь 7 узкого строба, формирователь 8 переменного строба, коммутатор 9, элемент 10 И, установочные шины 11 и 12, шину 13 управления.

Принцип работы делителя, например,

его работа при ,5, заключается в следующем.

На шину 13 поступает сигнаш , устанавливающий коммутатор 9 в положение, при котором третий вход элемента 10 И связан с первым выходом формирователя 8.

В исходном положении которому соответствует окончание предшествующего цикла деления, счётчики 1 и 2 устанавливаются в состояния, определяемые установочными шинами 11 и 12

оответственно, при этом счетчик 1 аходится в состоянии т (К+1) , счетчик 2 - в состоянии mj, 22-m, где п и п,2 - разрядности счетчиков 1 и 2 соответственно, К - коэффициент еления.

Дешифратор 3 настроен на-число - 2п. Формирователи 5 и 7, выполенные, например, на триггерах с разельным запуском, соответственно в нулевом и единичном состояниях. Формирователь 8, выполненный, например, на счетном триггере с возможностью установки его в фиксированное положение, находится в единичном состоянии (на его первом выходе , на втором О ), так как на первый вход формирователя 8 поступает нуле- . вой уровень. На первом и втором входах элемента 10 И - единичный уровень. I

Импульс входной последовательности, вызывающий формирование последнего выходного импульса делителя предшествующего цикла деления и задержанный фазосдвигающей цепью 4 на времяТфз, -tgx f приходит на первый вход элемента 10 и далее, через элемент б ИЛИ поступает на счетный вход счетчика 1, переводя его в состояние к, т.е. увеличивая его предыдущее, исходное состояние на 1. Пришедший импульс входной последовательности через элемент б ИЛИ поступает на счетный вход счетчика 1, переводя его в состояние 2 -К+1, т.е. также увеличивая его предыдущее состояние на единицу. Импульс входной последовательности устанавливает формирователь 7 в нулевое состояние, запрещая тем самьм срабатывание счетчика 1 от импульса, задержанного фазосдвигающей цепью 4.

При поступлении К импульсов входной последовательности счетчик 1 вырабатывает сигнал переполнения, который поступает на выход делителя, на вход установки счетчика 1, устанавливая его в исходное состояние щ, определяемое установочной шиной 11, на счетный вход счетчика 2, переводя его в состояние -m+1, т.е. увеличивая его предыдущее, исходное состояние на единицу, на первый вход формирователя 7, устанавливая его в единичное состояние, и на вход формирователя 8, не изменяя при этом состояния последнего, так как на другой . вход формирователя 8 продолжает по- ступать сигнал нулевого уровня, блокирующий его счетный вход.

Формирователь 7 узкого строба формирует импульсы длительностью fcT N3 передний фронт которых определяется передним фронтом выходных импульсов делителя, а их задний фронт - передним фронтом входных импульсов , следующих непосредственно за выходными j при этомГстру}-tp -tTo где tTcj- время задержки выходных импульсов делителя по отношению к вход ным, вызвавшим их появление . Частота следования импульсов, формируемых формирователем 7, равна частоте еледования выходных импульсов делителя Счетчик 1 суммирует импульсы, вызвавшие его срабатывание, и при заполнении формирует сигнал переполнения, поступающий на выход делителя в качестве выходного. Счетчик 2 суммирует выходные импульсы делителя . По прохождению т-2п выходных импульсов, период повторения которых Твщ К tg , счетчик 2 оказывается установленньш в состояние .-т + (m-2n) . Это же число устанавливается и на информационном входе дешифратора 2, на второй вход которого с первого выхода фазосдвигающей цепи 4 поступают импульсы, сдвинутые по отношению к соответствующим входным импульсам на время (Ji ° f 7Co При поступлении числа 2 - 2п на один вход дешифратора 3,.а импул са , сдвинутого по фазе на времяt( на его другой вход, на выходе дешифратора 3 возникает импульс, устанавливающий формирователь 5 в единичное состояние. С этого момента начинается форми рование широкого строба. На первый вход формирователя 8 поступает единичный уровень, устанавливающий его в нулевое состояние и разрешающий работу в режиме счетного триггера. На вход элемента 10 поступает нулевой уровень, запрещающий срабатывание счетчика 1 от импульса, задержа ного фазосдвигающей цепью 4. Условно назовем первыми период выходной последовательности и выходной импульс делителя, формируемые первьолн после момента начгша широкого строб Тогда первый выходной импульс дели теля оказывается сформированньпч поеле поступления к+1 входных импульсов. Первый период выходной последо вательности равен (а ()р Первый выходной импульс делителя возвращает формирователь 8 в единич ное состояние. Дгшее, счетчик 1 сра батывает от импульса, задержанного фазосдвигающей цепью 4. Второй пери выходной последовательности равен Т 1 Второй выходной импульс дели теля устанавливает формирователь 8 в нулевое состояние. Третий период выходной последовательности становится равным т , . Третий выходной импульс устанавливает формирователь 8 в единичное состояние и т.д. За время существования ширюкого строба формируется 2п выходных импу сов делителя, счетчик 2 заполняется до состояния 2, в результате чего на его выходе возникает сигнгш переполнения, устанавливающий формирователь 5 в нулевое состояние, что соответствует оконча нию широкого строба и данного цикла деления в целом. В дальнейшем работа делитепя повторяется, формируются выходные импульсы следукядего цикла деления. Таким образом, цикл деления делителя оказывается составленным из m периодов. Первые m - 2п периодов цикла равны TBJ,(J( , а последующие 2п образуют - п пар. Первый период каждой пары равен Трыхаг а второй - Tgbix-tПрименение предлагаемого делителя особенно эффективно при построении малогабаритной аппаратуры, например, синтезаторов частот, являющихся составной частью цифрового анализатора частотного спектра сигнала. У таких синтезаторов выходные частоты близки между, собой и могут быть получены из одной входной, частоты с помощью нескольких делителей с различными дробными коэффициентами деления. Повышение равномерности следования выходньбс импульсов, являющейся одним из основных параметров рассматриваемых делителей снижает уровень паразитных шумов анализатора, и, таким образом, повышает его чувствительность и избирательность. Формула изобретения Делитель частоты следования импульсов с переменным дробным коэффициентом деления, содержащий два счетчика импульсов, информационные входы которых подключены к соответствующим установочным шинам, выход первого счетчика импульсов подключен к его установочному входу, первому входу формирователя узкого строба и счетному входу второго счетчика импульсов, установочный вход которого соединен с его первым выходом и первым входом формирователя широкого строба, второй вход которого подключен к выходу дешифратора/информационный вход которого соединен со вторьы выходом первого счетчика импульсов, а стробирующий вход, - с первым выходом фазосдвигающей цепи, вход которой соединен с вторым входом формирователя узкого строба и первым входом элемента ИЛИ, а второй выход фазосдвигающей цейи и выход формирователя узкого строба соединены соответственно с первым и вторым входами элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого подключен к счетному входу первого счетчика импульсов, отличающийся тем, что, с целью расширения функциональных возмсжностей путем повышения равномерности следования выходных импульсов, в него введены коммутатор и формирователь переменного строба, первый и второй входы которого соединены соответственно с выходом формирователя широкого строба и выходом первого счетчика импульсов, а первый и второй выходы - с первым и вторым входами коммутатора, третий вход которого соединен с шиной управления, а выход - с третьим входом элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 658742, кл. Н 03 К 23/00, 10.01.77.

2. Авторское свидетельстро СССР

по заявке 2680447/18-21, кл. Н 03 К 23/00, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по периоду следования | 1980 |

|

SU911717A1 |

| Цифровой умножитель частоты следования периодических импульсов | 1987 |

|

SU1522375A2 |

| Умножитель частоты следования импульсов (его варианты) | 1983 |

|

SU1120483A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Делитель частоты следования импульсовС дРОбНыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819968A1 |

| Селектор импульсов по длительности | 1982 |

|

SU1067596A1 |

| Генератор последовательностей импульсов | 1985 |

|

SU1272479A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU949822A2 |

Авторы

Даты

1981-08-15—Публикация

1979-11-22—Подача