1

Изобретение относится к импульсной технике и может быть использовано в измерительной и вычислительной аппаратуре, где требуется деление импульсов, сгруппированных в пакеты импульсов.

По основному авт. св. № 445162 известен делитель частоты следования импульсов, содержащий счетчик импульсов, к выходам которого через дешифратор подключен коммутатор с двумя выходами, соответствующими целому и половинному коэффициентам деления, а также элемент ИЛИ, элемент И и триггер, первый вход которого соединен с выходом коммутатора целого коэффициента деления, обнуляющим входом счетчика импульсов и первым входом элемента ИЛИ, второй вход - с выходом коммутатора половинного коэффициента деления, а выход через элемент И - с вторым входом элемента ИЛИ 1.

Недостатком известного устройства является низкая надежность работы, так как сброс счетчика в процессе деления может происходить раньше, чем заканчиваются соответствующие входные импульсы, причем возможен неполный сброс счетчика, так как длительность импульса сброса очень мала.

поскольку она определяется временем переходных процессов в счетчике и дещифраторе.

Цель изобретения - повышение надежности работы устройства.

5Для достижения указанной цели в делитель частоты следования импульсов, содержащий счетчик импульсов, к выходам которого через дешифратор подключен коммутатор с двумя выходами соответствующими

Q целому и половинному коэффициентам деления, а также элемент ИЛИ, элемент И и триггер, первый вход которого .соединен непосредственно с выходом коммутатора целого коэффициента деления и с первым входом элемента ИЛИ, второй вход триггера соединен с выходом коммутатора половинного коэффициента деления, а выход через элемент И - с вторым входом элемента ИЛИ, введены элемент запрета и дополнительный триггер, первый вход которого соединен с

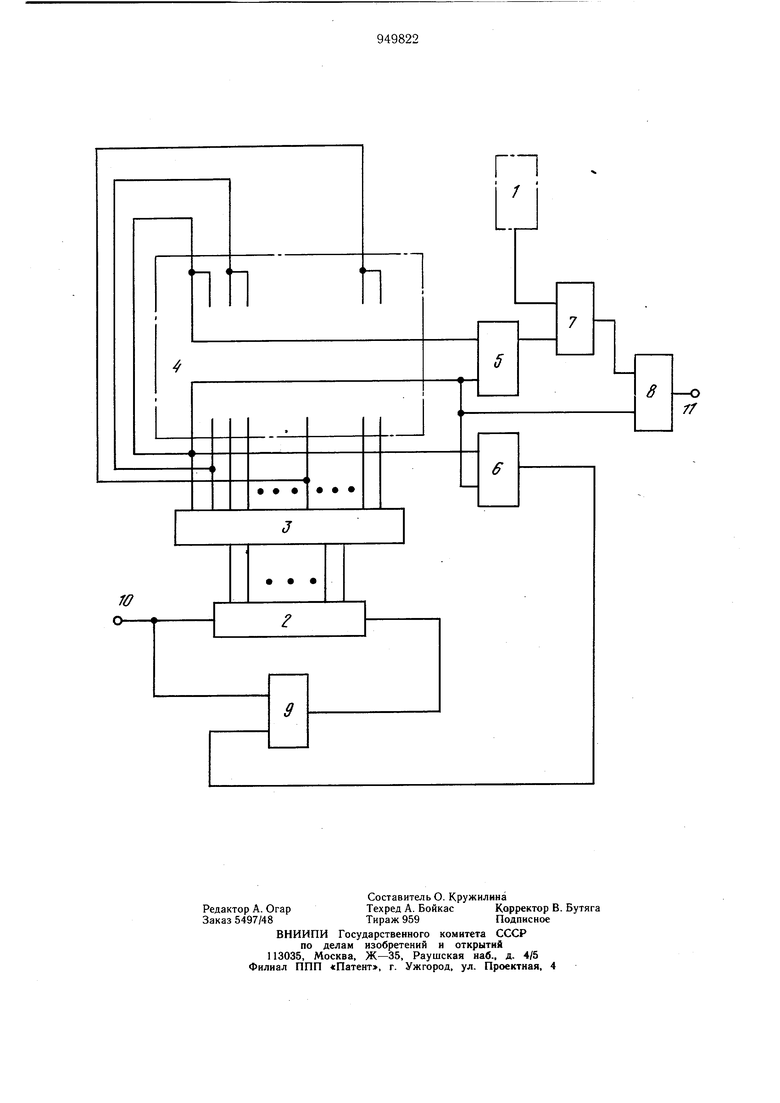

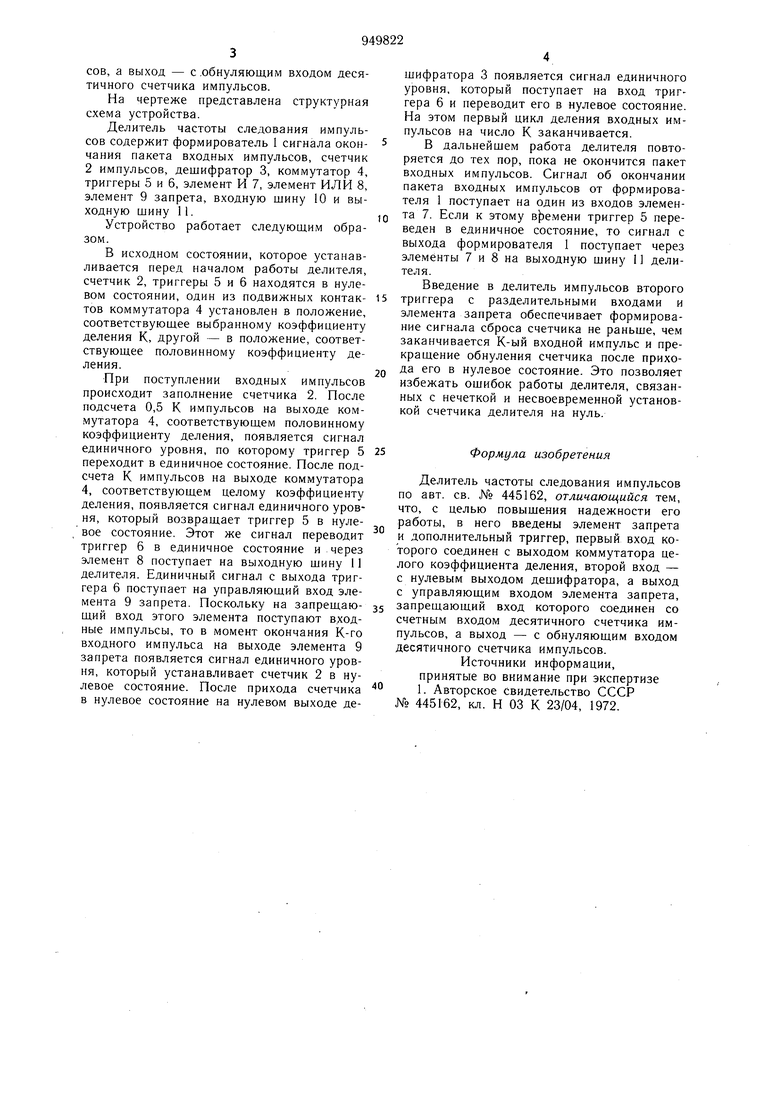

2Q выходом коммутатора целого коэффициента деления, второй вход - с нулевым выходом дешифратора, а выход - с управляющим входом элемента запрета, запрещающий вход которого соединен со счетным входом десятичного счетчика импульсов, а выход - с .обнуляющим входом десятичного счетчика импульсов. На чертеже представлена структурная схема устройства. Делитель частоты следования импульсов содержит формирователь I сигнала окончания пакета входных импульсов, счетчик 2 импульсов, дешифратор 3, коммутатор 4, триггеры 5 и 6, элемент И 7, элемент ИЛИ 8, элемент 9 запрета, входную шину 10 и выходную шину 11. Устройство работает следующим образом. В исходном состоянии, которое устанавливается перед началом работы делителя, счетчик 2, триггеры 5 и б находятся в нулевом состоянии, один из подвижных контактов коммутатора 4 установлен в положение, соответствующее выбранному коэффициенту деления К, другой - в положение, соответствующее половинному коэффициенту деления. При поступлении входных импульсов происходит заполнение счетчика 2. После подсчета 0,5 К импульсов на выходе коммутатора 4, соответствующем половинному коэффициенту деления, появляется сигнал единичного уровня, по которому триггер 5 переходит в единичное состояние. После подсчета К импульсов на выходе коммутатора 4, соответствующем целому коэффициенту деления, появляется сигнал единичного уровня, который возвращает триггер 5 в нулевое состояние. Этот же сигнал переводит триггер 6 в единичное состояние и через элемент 8 поступает на выходную шину 11 делителя. Единичный сигнал с выхода триггера 6 поступает на управляющий вход элемента 9 запрета. Поскольку на запрещающий вход этого элемента поступают входные импульсы, то в момент окончания К-го входного импульса на выходе элемента 9 запрета появляется сигнал единичного уровня, который устанавливает счетчик 2 в нулевое состояние. После прихода счетчика в нулевое состояние на нулевом выходе дешифратора 3 появляется сигнал единичного уровня, который поступает на вход триггера 6 и переводит его в нулевое состояние. На этом первый цикл деления входных импульсов на число К заканчивается. В дальнейшем работа делителя повторяется до тех пор, пока не окончится пакет входных импульсов. Сигнал об окончании пакета входных импульсов от формирователя 1 поступает на один из входов элемента 7. Если к этому времени триггер 5 переведен в единичное состояние, то сигнал с выхода формирователя 1 поступает через элементы 7 и 8 на выходную шину 11 делителя. Введение в делитель импульсов второго триггера с разделительными входами и элемента запрета обеспечивает формирование сигнала сброса счетчика не раньше, чем заканчивается К-ый входной импульс и прекращение обнуления счетчика после прихода его в нулевое состояние. Это позволяет избежать ошибок работы делителя, связанных с нечеткой и несвоевременной установкой счетчика делителя на нуль. Формула изобретения Делитель частоты следования импульсов по авт. св. № 445162, отличающийся тем, что, с целью повышения надежности его работы, в него введены элемент запрета и дополнительный триггер, первый вход которого соединен с выходом коммутатора целого коэффициента деления, второй вход - с нулевым выходом дешифратора, а выход с управляющим входом элемента запрета, запрещающий вход которого соединен со счетным входом десятичного счетчика импульсов, а выход - с обнуляющим входом десятичного счетчика импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 445162, кл. Н 03 К 23/04, 1972.

1П

п

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1983 |

|

SU1162037A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

| Делитель импульсов | 1983 |

|

SU1132369A2 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты следования импульсов | 1976 |

|

SU587628A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1175031A1 |

ю

/

о-

Авторы

Даты

1982-08-07—Публикация

1980-12-29—Подача