Изобретение относится к измерительной и вычислительной технике и может использоваться для измерения с высокой точностью серии временных интервалов между непрерывно следующими импульсами.

Известно устройство для измерения временных интервалов, которое содержит опорный генератор, два нониусных генератора с фазовой автоподстройкой частоты, входное устройство, основной и нониусные счетчики, микропроцессорный блок и обладает высокой точностью [1]. Однако известное устройство обладает недостаточными функциональными возможностями и не может измерять серии временных интервалов между непрерывно следующими импульсами.

Наиболее близким по технической сущности к заявляемому измерителю является нониусный измеритель серии временных интервалов [2], содержащий распределитель, опорный генератор, n схем И, n каналов преобразования, основной счетчик, первое и второе запоминающие устройства, схему ИЛИ, вычислительный блок. Известное устройство может измерять серии временных интервалов между непрерывно следующими импульсами, однако оно имеет ограниченное быстродействие, вызванное тем, что очередной импульс в канал преобразования не может прийти раньше, чем в этом канале закончится текущее преобразование.

Изобретение направлено на повышение быстродействия путем обеспечения возможности измерения временных интервалов между импульсами, поступающими с высокой интенсивностью.

Это достигается тем, что в нониусный измеритель временных интервалов, содержащий n каналов преобразования, n схем И, выходы которых соединены с первыми входами каналов преобразования, опорный генератор, выход которого подключен к вторым входам каналов преобразования, распределитель, выходы которого соединены с первыми входами схем И, усилитель, вход которого является входом измерителя, а выход которого соединен с вторыми входами схем И, основной счетчик, первое запоминающее устройство, информационные входы которого подсоединены к первым выходам каналов преобразования, второе запоминающее устройство, информационный вход которого подключен к выходу основного счетчика, схема ИЛИ, входы которой подсоединены к первым выходам каналов преобразования, вычислительный блок, входы которого подключены к вторым выходам каналов преобразования, а также к выходам первого и второго запоминающих устройств, введены делитель, формирователь, коммутатор, первый и второй переключатели, причем выход формирователя подключен к входу записи распределителя, а также к третьим входам схем И и к входу управления коммутатора, выход которого подключен к входу сдвига распределителя, первый вход коммутатора подключен к выходу усилителя, второй вход коммутатора подключен к выходу делителя, вход которого подсоединен к выходу опорного генератора и объединен с первым входом первого переключателя, второй вход которого подключен к первому выходу первого канала преобразования, а выход которого соединен с входом основного счетчика, первый вход второго переключателя подсоединен к выходу схемы ИЛИ, второй вход второго переключателя подключен к выходу усилителя, а его выход подключен к входам записи первого и второго запоминающих устройств, третьи входы каналов преобразования подсоединены к выходам распределителя, а их четвертые входы подключены к выходу формирователя.

Кроме того, в каждый канал преобразования введен переключатель, первый и второй входы которого подключены соответственно к третьему и второму выходам нониусного генератора, а выход которого является первым выходом канала преобразования.

Кроме того, в нониусный генератор введены смеситель, триггер, формирователь, фазовый детектор, подстраиваемый генератор и ключ, причем вход установки триггера, вход установки смесителя и вход запуска подстраиваемого генератора объединены с первым входом нониусного генератора, первый вход смесителя является вторым входом нониусного генератора, а выход смесителя соединен с первым входом фазового детектора и с синхронизирующим входом триггера, выход которого соединен с управляющим входом ключа, выход которого является первым выходом нониусного генератора, а также с входом формирователя, выход которого является третьим выходом нониусного генератора, второй вход фазового детектора является третьим входом нониусного генератора, управляющий вход фазового детектора является четвертым входом нониусного генератора, а его выход соединен с управляющим входом подстраиваемого генератора, выход которого является вторым выходом нониусного генератора, а также соединен с вторым входом смесителя и информационным входом ключа.

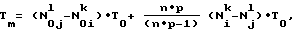

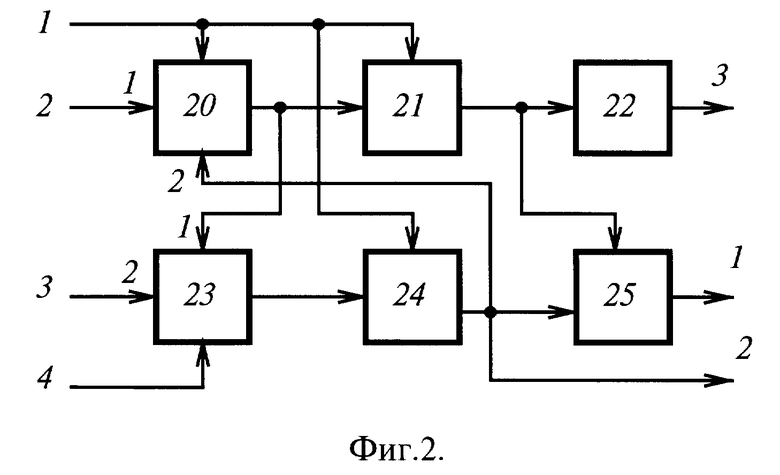

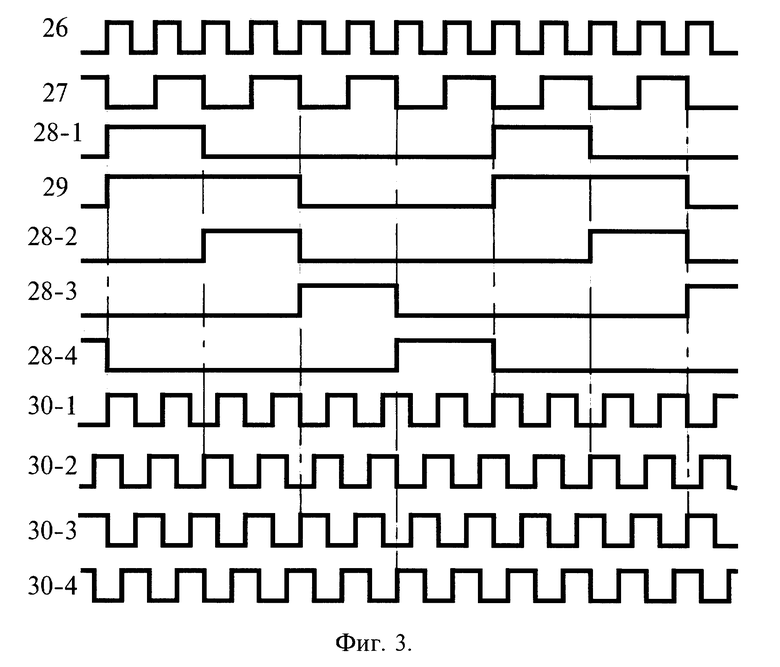

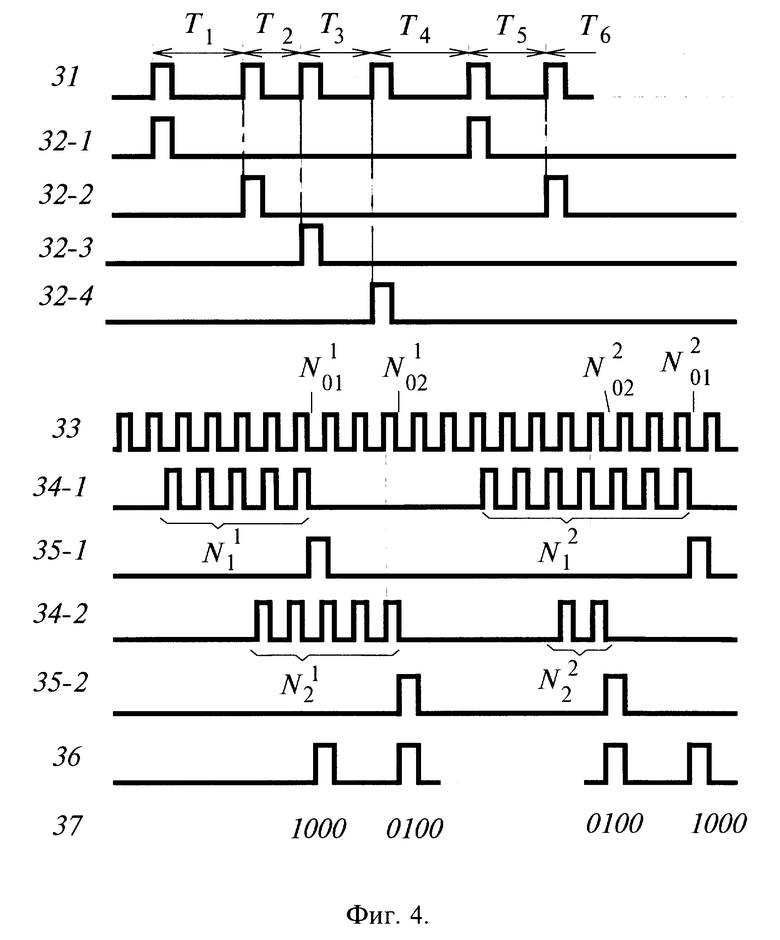

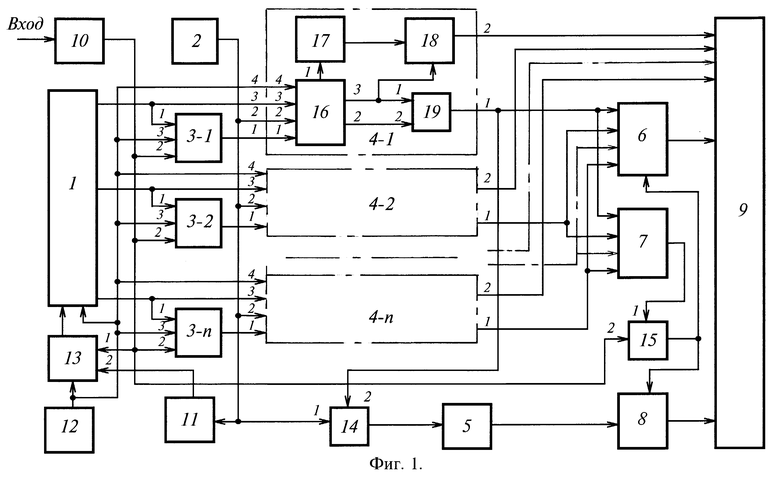

На фиг. 1 приведена структурная схема заявляемого измерителя, на фиг. 2 - схема нониусного генератора, на фиг. 3 и 4 - временные диаграммы работы измерителя, содержащего 4 канала преобразования (n = 4).

Измеритель (см. фиг. 1) содержит распределитель 1, опорный генератор 2, n схем И 3-1, 3-2 ... 3-n, n каналов преобразования 4-1, 4-2 ... 4-n, основной счетчик 5, первое запоминающее устройство 6, схему ИЛИ 7, второе запоминающее устройство 8, вычислительный блок 9, усилитель 10, делитель 11, формирователь 12, коммутатор 13, первый переключатель 14, второй переключатель 15.

Все каналы преобразования 4-1, 4-2 ... 4-n выполнены одинаково и каждый из них содержит нониусный генератор 16, нониусный счетчик 17, запоминающее устройство 18, переключатель 19.

В состав нониусного генератора (см. фиг. 2) входят смеситель 20, триггер 21, формирователь 22, фазовый детектор 23, подстраиваемый генератор 24, ключ 25.

Первые входы каналов преобразования 4-1, 4-2 ... 4-n подключены к выходам схем И 3-1, 3-2 ... 3-n, вторые входы каналов преобразования 4-1, 4-2 .. . 4-n подключены к выходу опорного генератора 2, выходы распределителя 1 соединены с первыми входами схем И 3-1, 3-2 ... 3-n, вход усилителя 10 является входом измерителя, а его выход соединен с вторыми входами схем И 3-1, 3-2 ... 3-n, информационные входы первого запоминающего устройства 6 подсоединены к первым выходам каналов преобразования 4-1, 4-2 ... 4-n, информационный вход второго запоминающего 8 устройства подключен к выходу основного счетчика 5, входы схемы ИЛИ 7 подсоединены к первым выходам каналов преобразования 4-1, 4-2 ... 4-n, входы вычислительного блока 8 подключены к вторым выходам каналов преобразования 4-1, 4-2 ... 4-n, а также к выходам первого 6 и второго 8 запоминающих устройств, выход формирователя 12 подключен к входу записи распределителя 1, а также к третьим входам схем И 3-1, 3-2 ... 3-n и к входу управления коммутатора 13, выход которого подключен к входу сдвига распределителя 1, первый вход коммутатора 13 подключен к выходу усилителя 10, второй вход коммутатора 13 подключен к выходу делителя 11, вход которого подсоединен к выходу опорного генератора 2 и объединен с первым входом первого переключателя 14, второй вход которого подключен к первому выходу первого канала преобразования 4-1, а выход первого переключателя 14 соединен с входом основного счетчика 5, первый вход второго переключателя 15 подсоединен к выходу схемы ИЛИ 7, второй вход второго переключателя 15 подключен к выходу усилителя 10, а его выход подключен к входам записи первого 6 и второго 8 запоминающих устройств, третьи входы каналов преобразования 4-1, 4-2 . .. 4-n подсоединены к выходам распределителя 1, а их четвертые входы подключены к выходу формирователя 12.

В каждом из каналов преобразования 4-i входы с первого по четвертый нониусных генераторов 16 являются входами с первого по четвертый каналов преобразования, первые выходы нониусных генераторов 16 подключены к входам нониусных счетчиков 17, выходы которых подсоединены к информационным входам запоминающих устройств 18, вторые выходы нониусных генераторов 16 подключены к вторым входам переключателей 19, выходы которых являются первыми выходами каналов преобразования, третьи выходы нониусных генераторов 16 подключены к первым входам переключателей 19, а также к входам записи запоминающих устройств 18, выходы которых являются вторыми выходами каналов преобразования.

В каждом из нониусных генераторов 16 вход установки триггера 21, вход установки смесителя 20 и вход запуска подстраиваемого генератора 24 объединены с первым входом нониусного генератора, первый вход смесителя 20 является вторым входом нониусного генератора, а выход смесителя 20 соединен с первым входом фазового детектора 23 и с синхронизирующим входом триггера 21, выход которого соединен с входом формирователя 22 и управляющим входом ключа 25, выход которого является первым выходом нониусного генератора, второй вход фазового детектора 23 является третьим входом нониусного генератора, управляющий вход фазового детектора 23 является четвертым входом нониусного генератора, а его выход соединен с управляющим входом подстраиваемого генератора 24, выход которого является вторым выходом нониусного генератора, а также соединен с вторым входом смесителя 20 и информационным входом ключа 25, выход формирователя 22 является третьим выходом нониусного генератора.

Измеритель работает в двух режимах: 1) в режиме многоканального нониусного измерителя (обычный режим); 2) в режиме считывания непрерывно генерируемых нониусных сигналов.

В первом режиме первый и второй переключатели 14 и 15, а также переключатели 19 в каналах преобразования находятся в первом положении, при котором на выход переключателей проходят сигналы с их первых входов. Такое включение обеспечивает синхронизацию работы основного счетчика 5 от опорного генератора 2 через первый переключатель 14; запись в первое 6 и второе 8 запоминающие устройства по сигналу с первого выхода любого из каналов преобразования 4-1, 4-2 ... 4-n через схему ИЛИ 7 и второй переключатель 15; прохождение на первый выход каждого из каналов преобразования сигнала с третьего выхода нониусного генератора 16 через переключатели 19.

Перед началом работы в распределитель 1, выполненный на основе кольцевого сдвигающего регистра, заносится код, содержащий единицу в первом разряде, а в остальных - нули. Когда импульсы, задающие границы измеряемых интервалов на вход не поступают, производится регулировка частоты нониусных генераторов. На выходе формирователя 12 вырабатывается уровень логического нуля, который разрешает прохождение через коммутатор 13 на вход сдвига распределителя 1 импульсов с выхода делителя 11. Работа измерителя при этом для коэффициента пересчета делителя, равного двум, поясняется временной диаграммой на фиг. 3, где изображено: 26 - сигнал опорного генератора 2; 27 - сигнал на выходе делителя 11; 28-1, .. 28-4 - сигналы на выходах распределителя 1; 29 - сигнал смесителя 20 в первом нониусном генераторе 16; 30-1, . . 30-4 - сигналы на вторых выходах нониусных генераторов 16 в каналах преобразования 4-1, 4-2 ... 4-n.

Распределитель 1 обеспечивает сдвиг информации по заднему фронту сигнала на выходе коммутатора 13 и вырабатывает на своих выходах сигналы синхронизации 28-1, 28-2 ... 28-n для подстройки частоты нониусных генераторов 16 с частотой fp = fo/(n•p), где fo - частота сигнала на выходе опорного генератора 2, n - количество нониусных блоков, p - коэффициент пересчета делителя 11. Система ФАПЧ в нониусных генераторах 16 поддерживает частоту сигнала на выходе подстраиваемого генератора 24

fн = (n•p-1) • fo/(n•p), (1)

При этом сигналы в нониусных генераторах будут сдвинуты друг относительно друга на величину Tф = 1/(n•fo) = To/n, где To = 1/fo - период сигнала опорного генератора 2 (см. фиг. 3).

Стабилизация сигналов в нониусных генераторах 16 (см. фиг. 2) осуществляется следующим образом. В качестве смесителя 20 используется D-триггер с динамическим запуском. Информационный вход D-триггера является первым входом смесителя, синхронизирующий вход D-триггера - вторым входом смесителя, а вход установки в единичное состояние S - управляющим входом. На выходе смесителя 20 вырабатывается сигнал разностной частоты fсм = fо - fн (см. , например, сигнал 29 на фиг. 3), причем в момент совпадения передних фронтов сигналов на входах смесителя сигнал на его выходе переходит из нулевого состояния в единичное. На фазовом детекторе 23 происходит сравнение передних фронтов сигналов, поступающих на его первый и второй входы. Если эти фронты не совпадают, то на выходе фазового детектора 23 вырабатывается сигнал, который так изменяет частоту сигнала подстраиваемого генератора 24, чтобы устранить расхождение передних фронтов. Таким образом, система фазовой автоподстройкой частоты (ФАПЧ) поддерживает равенство частот fсм = fр и совпадение передних фронтов сигналов на выходе смесителя 20 и соответствующем выходе распределителя 1. Это обеспечивает величину fн в соответствии с формулой (1) и совпадение передних фронтов сигналов подстраиваемого генератора 24 и опорного генератора 2 в момент переднего фронта сигнала на соответствующем выходе распределителя 1, что в свою очередь обеспечивает сдвиг сигналов в нониусных генераторах на величину Tф. При этом, поскольку для синхронизации используются сигналы распределителя 1, то из схем нониусных генераторов исключаются счетчики, которые должны присутствовать в известных устройствах [1] . Кроме того, при необходимости достаточно просто можно регулировать частоту fн для того, чтобы в зависимости от требуемой точности и быстродействия устанавливать оптимальные параметры измерителя. Последнее осуществляется изменением коэффициента пересчета делителя 11.

В момент начала цикла измерения до поступления первого импульса, отмечающего начало первого временного интервала, формирователь 12 переходит из нулевого состояния в единичное. Сигнал логической единицы на его выходе сохраняется на весь цикл измерений и заканчивается после прихода последнего временного интервала. При этом передним фронтом этого сигнала в распределитель 1 заносится код, содержащий единицу в первом разряде, а в остальных - нули. Единичный сигнал на выходе формирователя 12 переключает коммутатор 13 и разрешает прохождение входных импульсов с выхода усилителя 10 через первый вход коммутатора 13 на вход сдвига распределителя 1, после чего начинается цикл измерения.

Временная диаграмма работы измерителя в первом режиме при измерении временных интервалов показана на фиг. 4, где изображено: 31 - входной сигнал; 32-1, .. 32-4 - сигналы на выходах схем И 3-1, .. 3-4; 33 - сигнал на выходе опорного генератора 2; 34-1, 34-2 - сигналы на первых выходах нониусных генераторов 16 в первом и втором каналах преобразования 4-1, 4-2; 35-1, 35-2 - сигналы на третьих выходах нониусных генераторв 16 в первом и втором каналах преобразования 4-1, 4-2; 36 - сигнал на выходе схемы ИЛИ 7; 37 - информация, записываемая в первое запоминающее устройство 6.

Первый импульс измеряемой серии, проходя через усилитель 10 и схему И 3-1, запускает первый нониусный генератор 4-1, второй импульс запускает второй нониусный генератор 4-2 и т.д. После прихода входного импульса, запускающего i-й канал, единица из i-го разряда распределителя сдвигается в i+1-й разряд и разрешает запуск i+1-го канала (если i = n, то единица сдвигается в первый разряд). В результате распределитель 1 обеспечивает прохождение входных импульсов через элементы И 3-1, 3-2 ... 3-n на входы запуска каналов преобразования 4-1, 4-2 ... 4-n, в первый канал поступают импульсы с номерами 1, n+1, 2n+1 и т.д., во второй - 2, n+2, 2n+2 и т.д.

При поступлении запускающего импульса на первый вход нониусного генератора 16 в i-м канале преобразования на первом выходе нониусного генератора вырабатываются импульсы с частотой fн от момента запуска до совпадения передних фронтов сигналов опорного 2 и подстраиваемого 24 генераторов (для первого и второго каналов см. сигналы 34-1 и 34-2), которые подсчитываются на нониусном счетчике 17. В момент окончания преобразования на третьем выходе нониусного генератора 16 вырабатывается импульс (для первого и второго каналов см. сигналы 35-1 и 35-2) длительностью в один такт сигнала опорного генератора 2, по которому содержимое нониусного счетчика 17 записывается в запоминающее устройство 18. Этот импульс дублируется на первом выходе нониусного блока 4-i, и в результате по сигналу с выхода схемы ИЛИ 7 происходит запись информации в первое 6 и второе 8 запоминающие устройства. В первое запоминающее устройство 6 записывается информация о том, какой из каналов преобразования закончил измерение, во второе запоминающее устройство 8 записывается состояние основного счетчика 5. После окончания цикла измерений информация из нониусных каналов преобразования 4-1, 4-2 ... 4-n, из первого 6 и второго 8 запоминающих устройств передается в вычислительный блок 9, где величина временного интервала Tm определяется по формуле:

где i и j - номера каналов, запускаемых начальной и конечной границами m-го интервала, при этом j = i+1 при i < n и j = 1 при i = n;

k и l - номера запуска i-го j-го каналов при этом l = k, если i < n и l = k+1, если i = n (m = (k-1)•n+1);

N

N

Нониусный генератор 16 работает следующим образом. При поступлении запускающего импульса на первый вход нониусного генератора смеситель 20, реализованный на D-триггере, устанавливается в единичное состояние. Одновременно в единицу устанавливается триггер 21, разрешая прохождение через ключ 25 на выход импульсов с выхода подстраиваемого генератора 24. Триггер 21 реализован на D-триггере, вход асинхронной установки S которого является первым входом нониусного генератора, синхронизирующий вход триггера 21 реагирует на положительные перепады, а вход D триггера 21 подключен к уровню логического нуля. В момент совпадения фаз (передних фронтов) опорного сигнала и нониусного сигнала на выходе подстраиваемого генератора 24 смеситель 20 переключается в единичное состояние, что вызывает сброс триггера 21. В этот момент по заднему фронту сигнала триггера на выходе формирователя 22 вырабатывается импульс, свидетельствующий об окончании преобразования, одновременно прекращается прохождение импульсов подстраиваемого генератора 24 через ключ 25 на первый выход нониусного генератора.

Работа схемы ФАПЧ на время измерения блокируется единичным уровнем сигнала, поступающего на управляющий вход фазового детектора, вследствие чего частота сигнала на выходе подстраиваемого генератора 24 не изменяется.

Во втором режиме (режиме считывания), обеспечивающем повышенное быстродействие, первый 14 и второй 15 переключатели находятся во втором положении. Переключатели 19 в каналах преобразования 4-1, 4-2 ... 4-n находятся во втором положении, вследствие чего импульсы со вторых выходов нониусных генераторов 16 через переключатели 19 проходят на первые выходы каналов преобразования. Это обеспечивает прохождение на основной счетчик 5 импульсов с первого выхода первого канала преобразования 4-1 через первый переключатель 14, а также поступление импульсов с вторых выходов нониусных генераторов 16 всех каналов преобразования 4-1, 4-2 .. 4-n на входы первого запоминающего устройства 6. В качестве основной шкалы выступают импульсы с выхода первого канала 4-1. Интерполяция производится с помощью сдвинутых друг относительно друга на величину Tф непрерывно генерируемых нониусных сигналов 30-1, .. 30-4 (см. фиг. 3) с первых выходом каналов преобразования 4-1, 4-2 ... 4-n. Запись кодов интерполирующих сигналов в первое 6 и основного сигнала во второе 8 запоминающие устройства происходит по передним фронтам импульсов, отмечающих границы измеряемых временных интервалов и проходящих через усилитель 10, второй переключатель 15 и схему ИЛИ 7 на выходы записи запоминающих устройств 6 и 8.

После окончания цикла измерений информация из первого 6 и второго 8 запоминающих устройств передается в вычислительный блок 9, где вычисляются значения временных интервалов.

Таким образом, в заявляемом устройстве по сравнению с известными повышается быстродействие за счет введения режима считывания непрерывно генерируемых нониусных сигналов, в котором используются узлы измерителя, применяемые в обычном режиме. Кроме того, введение дополнительных элементов и связей позволяет использовать в обычном режиме распределитель для стабилизации частоты нониусных сигналов, что упрощает схему нониусных генераторов. Это позволяет также, при необходимости, легко регулировать частоту нониусных генераторов и соответственно разрешение и быстродействие нониусного метода путем изменения коэффициента пересчета делителя.

Источники информации

1. "Электроника", 1977, N 23, с. 25 - 34.

2. Авторское свидетельство СССР N 930213, кл. G 04 F 10/00, 1982.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2127445C1 |

| СПОСОБ НОНИУСНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ С ОПРЕДЕЛЯЕМЫМ КОЭФФИЦИЕНТОМ ИНТЕРПОЛЯЦИИ (ВАРИАНТЫ) | 1998 |

|

RU2138839C1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2128853C1 |

| СПОСОБ УСКОРЕННОЙ НОНИУСНОЙ ИНТЕРПОЛЯЦИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2133053C1 |

| Измеритель серии временных интервалов | 1980 |

|

SU935869A1 |

| ФОРМИРОВАТЕЛЬ МЕТОК ВРЕМЕНИ | 2018 |

|

RU2665283C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СЕРИЙ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2004 |

|

RU2255366C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ ОБЪЕКТА | 1991 |

|

RU2100775C1 |

| Измеритель серии временных интервалов | 1980 |

|

SU930213A1 |

Измеритель относится к хронометрической технике и предназначен для измерения с высокой точностью и высоким быстродействием серии временных интервалов между непрерывно следующими импульсами. Измеритель может использоваться для контроля устройств вычислительной техники и систем передачи данных. Устройство содержит распределитель, опорный генератор, n каналов преобразования, n схем И, основной счетчик, первое и второе запоминающие устройства, схему ИЛИ, делитель, формирователь, коммутатор, первый и второй переключатели и вычислительный блок. Измеритель имеет более высокое быстродействие по сравнению с известными устройствами. Повышение быстродействия достигается за счет введения дополнительных узлов и связей, позволяющих считывать непрерывно генерируемые нониусные сигналы в моменты поступления границ временных интервалов. 2 з.п. ф-лы, 4 ил.

| Измеритель серии временных интервалов | 1980 |

|

SU930213A1 |

| Чу Д., Фергюссон К | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| -с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| SU 913328 A, 15.03.82. | |||

Авторы

Даты

1999-01-27—Публикация

1997-04-22—Подача