(54) РЕЛЕ ВРЕМЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1981 |

|

SU1073818A1 |

| Реле времени с выдержкой на возврат после отключения напряжения питания | 1982 |

|

SU1160480A2 |

| ОСВЕТИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2031554C1 |

| Импульсный регулятор | 1990 |

|

SU1829026A1 |

| Реле времени с выдержкой времени на возврат после отключения напряжения питания | 1978 |

|

SU750608A1 |

| Реле времени | 1984 |

|

SU1265877A1 |

| Устройство задержки | 1981 |

|

SU970689A1 |

| Программное реле времени | 1978 |

|

SU790311A1 |

| Устройство защитного отключенияэлЕКТРОуСТАНОВКи | 1978 |

|

SU847422A1 |

| Полупроводниковое счетно-импульсное реле времени | 1974 |

|

SU527823A1 |

I

Изобретение относится к электротехнике и может найти применение в устройствах защиты на переменном оперативном токе и в схемах автоматического ввода резервного питания (АВР).

Известны реле с выдержкой времени на возврат после отключения напряжения питания, в которых для приведения в действие выходного реле с магнитной памятью используется энергия, предварительно накопленная в конденсаторе, подключаемом к обмотке реле полупроводниковым ключевым элементом (например тиристором), импульс на включение которого поступает с выхода времязадающего элемента. При этом в качестве такого времязадающего элемента используется мостовая схема, состоящая из времязадающего конденсатора, защунтированного регулируемым резистором и подключенного к источнику опорного напряжения через разделительный диод, конденсатора памяти, подключенного к делителю опорного напряжения через разделительный диод, и порогового элемента в виде программируемого однопереходного транзистора (ПОПТ), или его двухтранзисторного аналога, включенного выводами

эмиттера и первой базы между указанными конденсаторами, а выводом второй базы через токоограничивающий резистор - к цепи управления выходным ключевым элементом 1.

Однако устройство имеет недостаточную точность выдержек времени из-за возможного различного уровня заряда конденсатора памяти.

Для ликвидации этого недостатка требуется, чтобы при наличии напряжения питания разделительный диод в цепи заряда конденсатора памяти был открыт. Для достижения этой цели предлагается параллельно конденсатору памяти включить высокоомный разрядный резистор через диодный ключ, управляемый коммутацией цепи питания реле.

От схемы указанного реле схема данного реле отличается наличием диода в цепи питания реле и разрядного резистора, подключенного, с одной стороны к конденсатору памяти, а с-другой через диод - к клемме питания 2.

Однако данное реле может функционировать только при контактном управлении и имеет в связи с этим ограниченную область прнм.нения. Кроме того, требуется обеспечение надежного функционирования не только при скачкообразном снижении напряжения питания до нуля, но и при плавном его снижении до какого-либо уровня. В некоторых устройствах защиты .требуется получение более одной выдержки времени при обпдем пуске отключением питания. В этом случае более экономичным является многоцепное реле времени с общими цепями питания и управления.

Цель изобретения - повыщение точности и стабильности и расширение функциональных возможностей реле.

Поставленная цель достигается тем, что в реле времени с задержкой на возврат после отключения напряжения питания или снижения его ниже определенной величины, содержащем времязадающие RC-цепи, соединенные с пороговыми элементами, например, на программируемых однопереходных транзисторах, и через разделительные диоды с источником стабилизированного напряжения, конденсаторы памяти, соединенные эмиттерами указанных программируемых однопереходных транзисторов и с разрядными цепочками из последоватеЯьно соединенных резисторов и разделительных диодов, а также через разделительные диоды с делителями стабилизированного напряжения, ключевые элементы, выходные реле с магнитной памятью, накопительные конденсаторы, трансформатор, выпрямительный мост и стабилитрон, последовательно со стабилитроно.м включен переход база - эмиттер дополнительного транзистора, зашунтированный резистором, резисторнодиодные разрядные цепочки подключены к ко.1лектору указанного транзистора, а между точкой соединения времязадающих RCцепей с разделительными диодами и выводами первой базы программируемых однопереходных транзисторов включены допол-, нительно балластные резисторы.

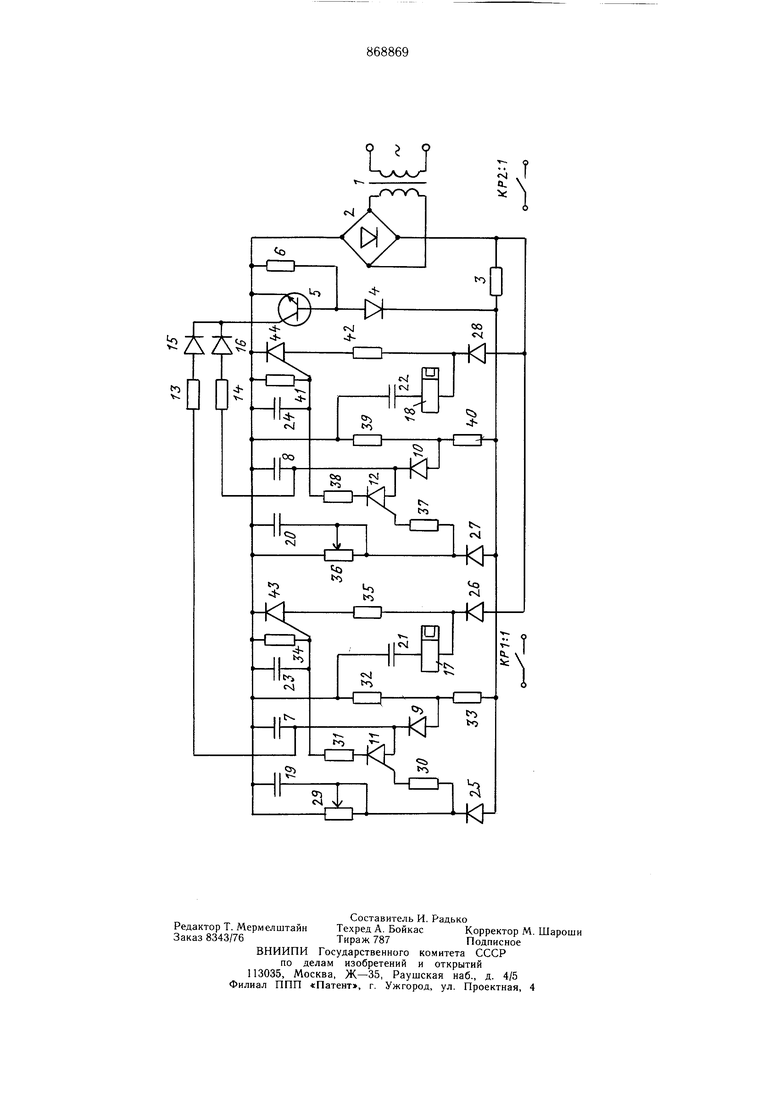

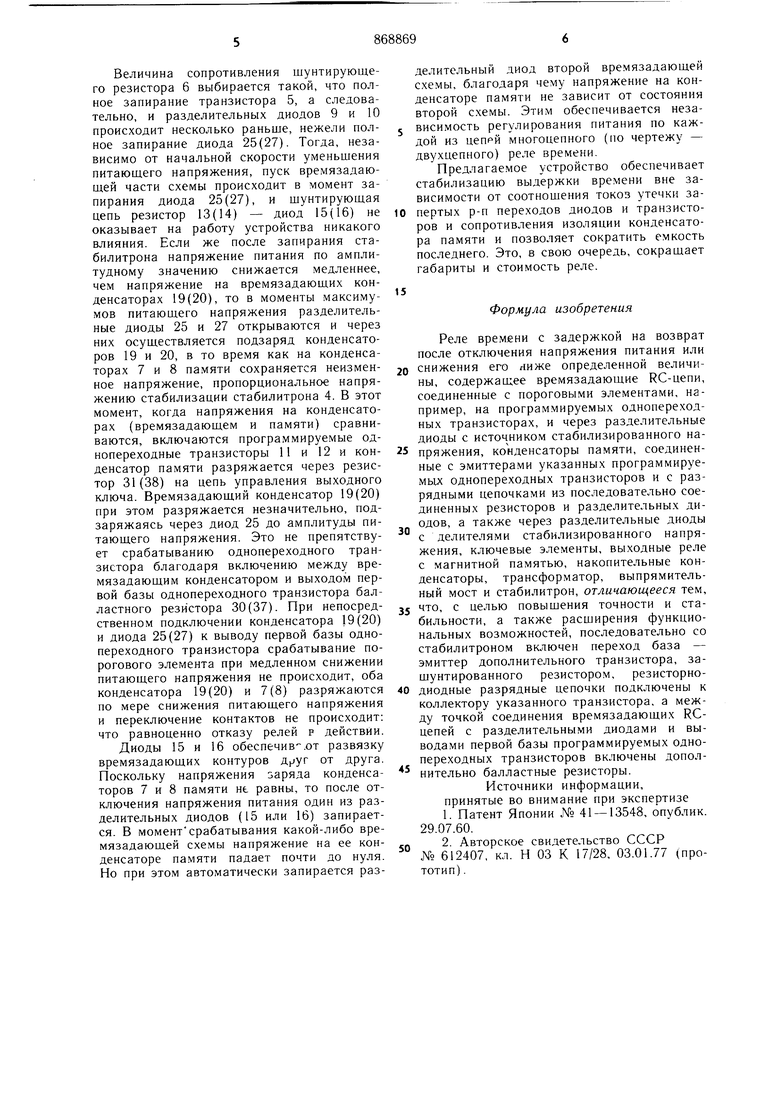

На чертеже представлена принципиальная электрическая схема двухцепного реле времени с общей цепью питания и управления.

Схема состоит из двух одинаковых элементов задержки на возврат, близких по схеме известному реле, но имеющих общий блок питания, состоящий из трансформатора 1, выпрямительного моста 2, балластного резистора 3 и стабилитрона 4. Последовательно со стабилитроном включен переход база - эмиттер дополнительного транзистора 5, зашунтированный резистором 6, причем эмиттер этого транзистора соединен с общей точкой всех конденсаторов устройства и минусовым выводом источника питания (моста 2). Между точками соединения конденсатора 7 (8) памяти с разделительными диодами 9 (10) и эмиттерами программируемых однопереходных транзисторов 11 и 12 включены разрядные резисторы 13 (14) последовательно с дополнительными разделительными диодами 15 и 16. Катоды диодов 15 и 16 подключены к коллектору транзистора 5. Устройство содержит также реле 17 и

18с магнитной памятью, конденсаторы 19- 24, разделительные диоды 25-28, резисторы 29-42, выходные ключи, например на тиристврах 43 и 44.

Устройство работает следующим обра0 зом.

При подаче напряжения питания скачком реле 17 и 18 с магнитной памятью срабатывают и самоудерживаются, конденсаторы 19(20), 7(8), 21(22) заряжаются, а транзистор 5 переходит в режим переключения: если ток стабилизации стабилитрона 4 больще тока щунта (резистор 6), появляющийся ток базы переводит транзистор в режим насыщения, в те же моменты времени, когда .мгновенные значения напряжения на выходе моста ниже уровня стабилизации, ток через стабилитрон прерывается, транзистор переходит в режим отсечки. При номинальном напряжении питания транзистор 5 больщую часть периода насыщен и подключает через диоды 15 и 16 резисторы 13 и 14 параллельно конденсаторам 7 и 8 памяти, обеспечивая открытое состояние разделительных диодов 9 и 10, что исключает возможность неконтролируемого заряда конденсатора 7 и 8 памяти токами утечки переходов э.мит0 -rep - база программируемых однопереходных транзисторов в длительном режиме при поданном напряжении питания и тем самым стабилизирует выдержки времени на возврат после отключения напряжения питания.

При отключении напряжения питания или снижении его со скоростью, превыщающей скорость разряда конденсаторов 19 и 20 на времязадающие резисторы 29(30), ниже порога стабилизации стабилитрона

0 4 транзистора 5 запирается, отключая разрядные цепочки резистор 13 - диод 15 и резистор 14 - диод 16 от конденсаторов 7 и 8 памяти, при это.м одновре.менно запираются разделительные диоды 25, 27, 9 и 10. В момент уравнивания напряжений

на времязадающем конденсаторе 19(20) и конденсаторе 7(8) памяти включается однопереходный транзистор 11 и происходит разряд конденсаторов на цепь управления выходного ключа 44 через резисторы 30(37)

Q и 31(38). Ключ, например тиристор, включается и разряжает накопительный конденсатор 21(22) на обмотку реле 17(18). возвращая его в исходное состояние. Поскольку к этому времени напряжение питания либо отсутствует, либо мало, повторное срабатывание выходного реле не происходит. Срабатывание его происходит лищь за счет последующей подачи номинального напряжения питания.

Величина сопротивления шунтирующего резистора 6 выбирается такой, что полное запирание транзистора 5, а следовательно, и разделительных диодов 9 и 10 происходит несколько раньше, нежели полное запирание диода 25(27). Тогда, независимо от начальной скорости уменьшения питающего напряжения, пуск времязадающей части схемы происходит в момент запирания диода 25(27), и шунтирующая цепь резистор 13(14) - диод 15(16) не оказывает на работу устройства никакого влияния. Если же после запирания стабилитрона напряжение питания по амплитудному значению снижается медленнее, чем напряжение на времязадающих конденсаторах 19(20), то в моменты максимумов питающего напряжения разделительные диоды 25 и 27 открываются и через них осуществляется подзаряд конденсаторов 19 и 20, в то время как на конденсаторах 7 и 8 памяти сохраняется неизменное напряжение, пропорциональное напряжению стабилизации стабилитрона 4. В этот момент, когда напряжения на конденсаторах (времязадающем и памяти) сравниваются, включаются программируемые однопереходные транзисторы 11 и 12 и конденсатор памяти разряжается через резистор 31 (38) на цепь управления выходного ключа. Времязадающий конденсатор 19(20) при этом разряжается незначительно, подзаряжаясь через диод 25 до амплитуды питающего напряжения. Это не препятствует срабатыванию однопереходного транзистора благодаря включению между времязадающим конденсатором и выходом первой базы однопереходного транзистора балластного резистора 30(37). При непосредственном подключении конденсатора }9(20) и диода 25(27) к выводу первой базы однопереходного транзистора срабатывание порогового элемента при медленном снижении питающего напряжения не происходит, оба конденсатора 19(20) и 7(8) разряжаются по мере снижения питающего напряжения и переключение контактов не происходит: что равноценно отказу релей р действии. Диоды 15 и 16 обеспечив-.от развязку времязадающих контуров друг от друга. Поскольку напряжения заряда конденсаторов 7 и 8 памяти не равны, то после отключения напряжения питания один из разделительных диодов (15 или 16) запирается. В моментсрабатывания какой-либо времязадающей схемы напряжение на ее конденсаторе памяти падает почти до нуля. Но при этом автоматически запирается разделительный диод второй времязадающеи схемы, благодаря чему напряжение на конденсаторе памяти не зависит от состояния второй схемы. Этим обеспечивается независимость регулирования питания но каждой из цепрй многоцепного (по чертежу - двухцепного) реле времени.

Предлагаемое устройство обеспечивает стабилизацию выдержки времени вне зависимости от соотношения токоз утечки запертых р-п переходов диодов и транзисторов и сопротивления изоляции конденсатора памяти и позволяет сократить емкость последнего. Это, в свою очередь, сокращает габариты и стоимость реле.

15

Формула изобретения

Реле времени с задержкой на возврат после отключения напряжения питания или

0 снижения его ниже определенной величины, содержащее времязадающие RC-цепи, соединенные с пороговыми элементами, например, на программируемых однопереходных транзисторах, и через разделительные диоды с источником стабилизированного напряжения, конденсаторы памяти, соединенные с эмиттерами указанных программируемых однопереходных транзисторов и с разрядными цепочками из последовательно соединенных резисторов и разделительных диодов, а также через разделительные диоды

0 с делителями стабилизированного напряжения, ключевые элементы, выходные реле с магнитной памятью, накопительные конденсаторы, трансформатор, выпрямительный мост и стабилитрон, отличающееся тем,

5 что, с целью повыщения точности и стабильности, а также расширения функциональных возможностей, последовательно со стабилитроном включен переход база - эмиттер дополнительного транзистора, защунтированного резистором, резисторно0 диодные разрядные цепочки подключены к коллектору указанного транзистора, а между точкой соединения времязадающих RCцепей с разделительными диодами и выводами первой базы программируемых однопереходных транзисторов включены допол5нительно балластные резисторы.

Источники информации, принятые во внимание при экспертизе 1. Патент Японии № 41 -13548, опублик. 29.07.60.

№ 612407, кл. Н 03 К 17/28, 03.01.77 (прототип) .

Авторы

Даты

1981-09-30—Публикация

1980-01-04—Подача