(54) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1980 |

|

SU875629A1 |

| УСТРОЙСТВО КОМПЛЕКСНОЙ ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1996 |

|

RU2117372C1 |

| Стабилизирующий источник напряжения постоянного тока | 1986 |

|

SU1347136A1 |

| Устройство для контроля состояния распределенных объектов | 1985 |

|

SU1285509A1 |

| Устройство для контроля пробоя последовательно соединенных тиристоров высоковольтных вентилей в управляемом вентильном преобразователе | 1990 |

|

SU1760595A1 |

| Устройство задержки импульсов | 1979 |

|

SU856000A1 |

| УСТРОЙСТВО ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1996 |

|

RU2118029C1 |

| ПЕРЕКЛЮЧАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 1996 |

|

RU2127479C1 |

| Стабилизированный преобразователь напряжения | 1973 |

|

SU586532A1 |

| Стабилизированный преобразователь постоянного напряжения | 1985 |

|

SU1325636A1 |

Изобретение относится к устройствам автоматики и может быть использовано для формирования соответствующи х задержек подключения под ток различных разветвленных нагрузок, запитываемых от одного общего источника питания при запуске подаЧей питающего напряжения с индикацией состояния каждого из устройств (включено - выключено) , с защитой устройства от короткого замыкания нагрузки и с индикацией кратковременного пропадания тока в нагрузке.

Известно реле времени, содержащее времязадающую КС-цепь, выход которой подключен к входу порогового элемента в виде двухтранэисторного аналога однопереходного транзистора, конденсатор памяти, соединенный с Делителем опорного напряжения через разделительный диод и связанный с эмиттером указанного аналога однопереходного транзистора и выходного реле с магнитной памятью, обмотка которого включена последовательно с накопительным конденсатором, стабилитрон, бсшластные резисторы, разделительные диоды, при этом между дочкой соединения.конденсатора пзмя ти с эмиттером аналога однопереходго транзистора и разделительным диодом, с одной стороны, и отрицательной клеммой источника питания, с другой стороны, включены последовательно соединенные резистор и йиод, а между общей точкой соединения всех конденсаторов устройства и указ анной клеммой питания включен второй диод

10

Известно -устройство задержки, содержащее соединенные последовательно времязадающую цепь, компаратор, выполненный, например, на транзисторе с резистором и переключающем дибДе в

15 эмиттерной цепи, выходной транзистор с нагрузкой в коллекторной цепи, инвертор, включенный между компаратором и выходным транзистором, синхронные разрядный ключ и управляемый ис20точник напряжения, запускающий ключ и развязывающее устройство, разрядный ключ подсоединенfпараллельно конденсатору времязадающей цепи, а вход разрядного ключа совместно со

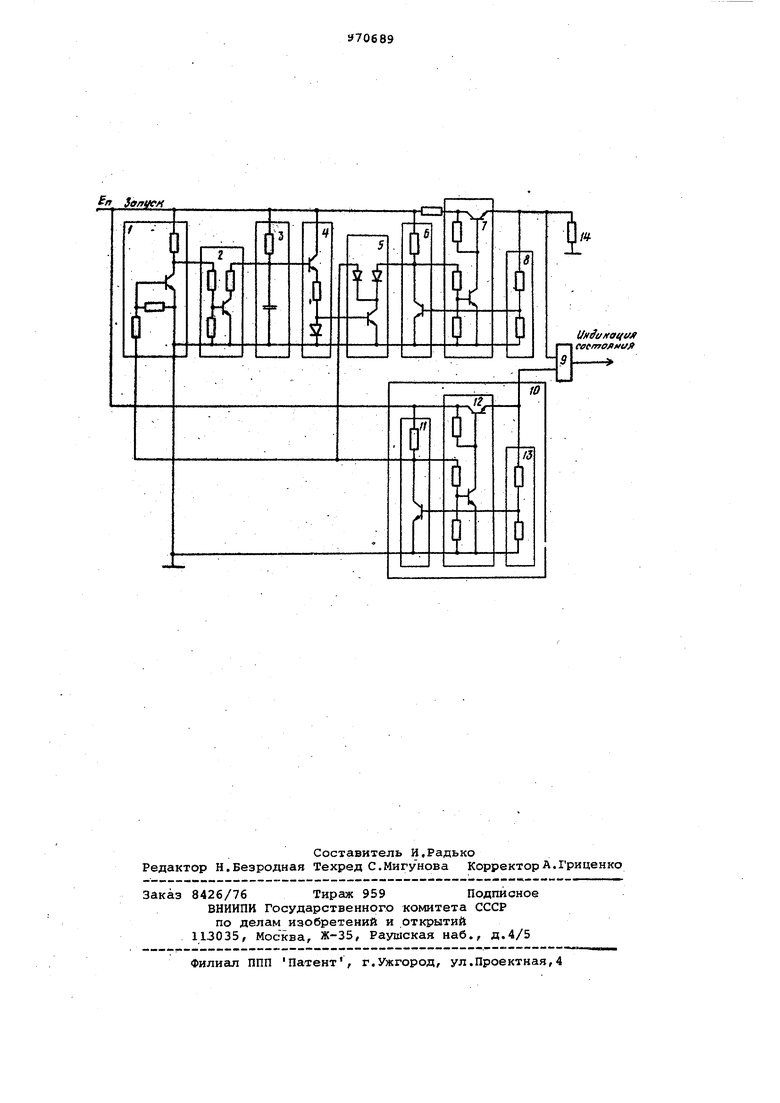

25 входом управляемого источника напряжения подключены к общей точке соединения выходов развязывающего устройства и запускающего ключа, выход управляемого источника напряжения под30Jключeн к времязадающей цепи и инвентору, вход развязывающего устройства подключен к общей точке выхрдного транзистора и нагрузки, а вход запускающего ключа - к источнику запус ;ка 2 . В указанном устройстве задержки отсутствует защита от короткого замыкания .нагрузки, нагрузка в общем случае включена не относительно корпуса, отсутствует инднкация состояния устройства, что снижает его показатель надежности, Кроме этого , от сутствует возможность формирования соответствующих задержек подачи напряжения Б разветвленные нагрузки, за питываемые от общего источника питания. Цель изобретения - повышение надежности. Указанная дель достигается тем, что в устройство задержки, содержащее соединенные последовательно времязадающую цепь и компаратор, разрядный ключ, подключенный параллельн конденсатору времязадающей цепи,узе развязки, управляемый источник напряжения, нагрузку, введены управляемый делитель, блокирующая цепь обратной связи, ключ исходного состояния и узел памяти, при этом узелра вязки включен между выходом компараторами выходом управляемого делителя подключенного к входу управляемого источника напряжения, вход блокирующей цепи обратной связи подключен к входу управляемого источника и нагру ке, а выход-- ко входу управляемого делителя, выход ключа исходного состояния подключен к входу управления разрядного ключа, а вход его - ко второму выходу узла развязки, вход у ла памяти соединен с входом ключа ис ходного состояния,общая точка соединения ключа исходного состояния,времязадающей цепи,компаратора.,управляемого делителя и управляемого источника напряжения подключена к шине запуска. В предлагаемом устройстве задержки узел памяти выполнен состоящим из соединенных последовательно управляемого делителя, управляемого источни ка и блокирующей цепи обратной связи выход которой соединен с входом упра ляемого узла памяти. С целью индикации состояния нагрузки в устройство может быть введен элемент И, через который выход управ ляемого источника устройства и выход управляемого источника узла памяти соединены с выходом индикации состоя ния устройства. Для обеспечения индикации (регист рации) пропадания тока в нагрузке узел памяти должен подключаться к дополнительному источнику питания. На чертеже представлена принципиальная электрическая схема предлагае мого .устройства задержки. Устройство содержит ключ 1 исходного состояния, разрядный ключ 2, времязадающую цепь 3, компаратор 4, узел 5 развязки, управляемый делитель б, управляемый источник 7 напряжения, блокирующую цепь 8 обратной связи, узел 9 выдачи сигнала, свидетельствующего о состоянии устройства, (представляющей собой, например, элемент И) и узел 10 памяти, содержащий, например, управляемый делитель И, управляемый источник 12 и блокирующую цепь 13 обратной связи, нагрузку 14. Устройство работает следующим образом. При подаче питающего напряжения по шине Запуск конденсатор времязадающей цепи 3 разряжен, выходной уровень компаратора 4 низкий, транзистор узла 5 развязки заперт и. напряжение питания Ef через резистор управляемого делителя 6 подается на вход управляемого источника 7, формируя на выходе его и на нагрузке 14 нулевой ВЫХОДНОЙ уровень, который через блокирующую цепь 8 обратной связи подается на транзистор управляемого делителя б, обеспечивая запертое его состояние. Аналогично формируется нулевой выходной уровень на выходе управляемого источника 12. Высокий выходной уровень с управляемого делителя 11 открывает ключ 1 Я исходного состояния, что приводит к запиранию разрядного ключа 2 и началу заряда конденсатора времязадающей цепи 3. При достижении на зарядном конденсаторе некоторого уровня (формирование интервала задержки) на выходе компаратора 4 формируется высокий уровень, что приводит к отпиранию транзистора узла 5 развязки, подаче низкого входного уровня на вход управляемого источника 7 и формированию на выходе его высокого уровня, подача которого через блокирующую цепь 8 обратной связи на транзистор управляемого делителя б приводит к блокировке низкого уровня на входе управляемого источника 7. Нагрузка 14 подключается под ток с соответствующей задержкой. Аналогично формируется высокий выходной уровень на выходе.управляемого источника 12. Низкий уровень на коллекторе управляемого делителя 11 запирает ключ 1 .исходного состояния, при этом открывается разрядный ключ 2 и разряжает зарядный конденсатор времязадающей цепи 3, при этом на выходе компаратора 4 формируется низкий уровень и транзистор узла 5 развязки запирается. Устройство приходит в исходное состояние. Сигнал о состоянии устройства задержки выдается для индикации или автоматической обработки с узла 9 выдачи сигнала.

При коротком замыка11ии нагрузки 14 на выходе управляемого источника 7 высокий уровень не формируется и происходит блокировки его низкого входного уровня, поэтому после приведения устройства формирования временного интервала, состоящего из ключа исходного состояния, разрядного ключа, времяэадающей цепи, компаратора, в исходное состояние нагрузка 14 не подключаете под ток, о чем свидетельствует состояние выходного уровня узла 9 выдачи сигнала-.

При запитке узла 10 памяти от другого источника питающего напряжения, поданного до или совместно с подачей Ер по шине Запуск, устройство може фиксировать кратковременное пропадание Е(1 , так как происходит разблокировка части устройства из узлов ( управляемый делитель, управляемый источник напряжения, блокирующая цеп обратной с.вязи, а устройство формирования временного интервала блокировано низким уровнем на коллекторе транзистора управляемого делителя 11 т.е. повторное включение нагрузки 14 под ток невозможно без разблокировки узла 10 памяти.

Предлагаемое устройство и источник его питания защищены от короткого замыкания нагрузки, причем включение балластного резистора Р g может повысить эффективность защиты. Кроме того обеспечивается возможность подключения нагрузки под ток без электромагнитного исполнительного элмента, возможность контроля состояния нагрузки, а также возможность подключения под ток разветвленных нагрузок к общему источнику напряжения с соответствующей задержкой при запуске подачей напряжения питания.

При выполнении управляемого источника устройства в виде транзисторного ключа с обмоткой нейтрального электромагнитного реле в коллекторной цепи устройство работает как реле времени, причем обмотка реле находится под током только во время формирования временного интервала.

При запитке узла памяти от дополнительного источника обеспечивается возможность фиксации (контроля) режима кратковременного пропадания тока в нагрузке.

Большая часть устройства может Ьыть выполнена как в модульном, так и интегральном исполнении.

Все это позволяет сделать вывод, что предлагаемое устройство задержки обладает достаточно высоким показателем надежности по сравнению с известньп м и обладает достаточно широкими функциональными возможностями.

Формула изобретения

и управляемого источника напряжения подключена к шине запуска.

Источники информации, принятые во внимание при экспертизе

612407, кл. Н 03 К 17/28, 03.01.7

по заявке 1 2883697, кл. Н 03 К 17/2 20.02.80.(прототип). ftt $oni/ef Un t/ftai(M ceemoj ftu/

Авторы

Даты

1982-10-30—Публикация

1981-04-22—Подача