(54) ПРЕОБРАЗОВАТЕЛЬ УРОВНЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор напряжения для электромашинного генератора | 1981 |

|

SU1005264A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Коммутатор | 1979 |

|

SU788381A1 |

| Генератор стробирующих импульсов для стробоскопического осциллографа | 1982 |

|

SU1072256A1 |

| Переносной шахтный сигнализатор метана | 1990 |

|

SU1749486A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1444921A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Устройство формирования импульсов | 1986 |

|

SU1347170A1 |

| Многофазный мультивибратор | 1979 |

|

SU834836A2 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

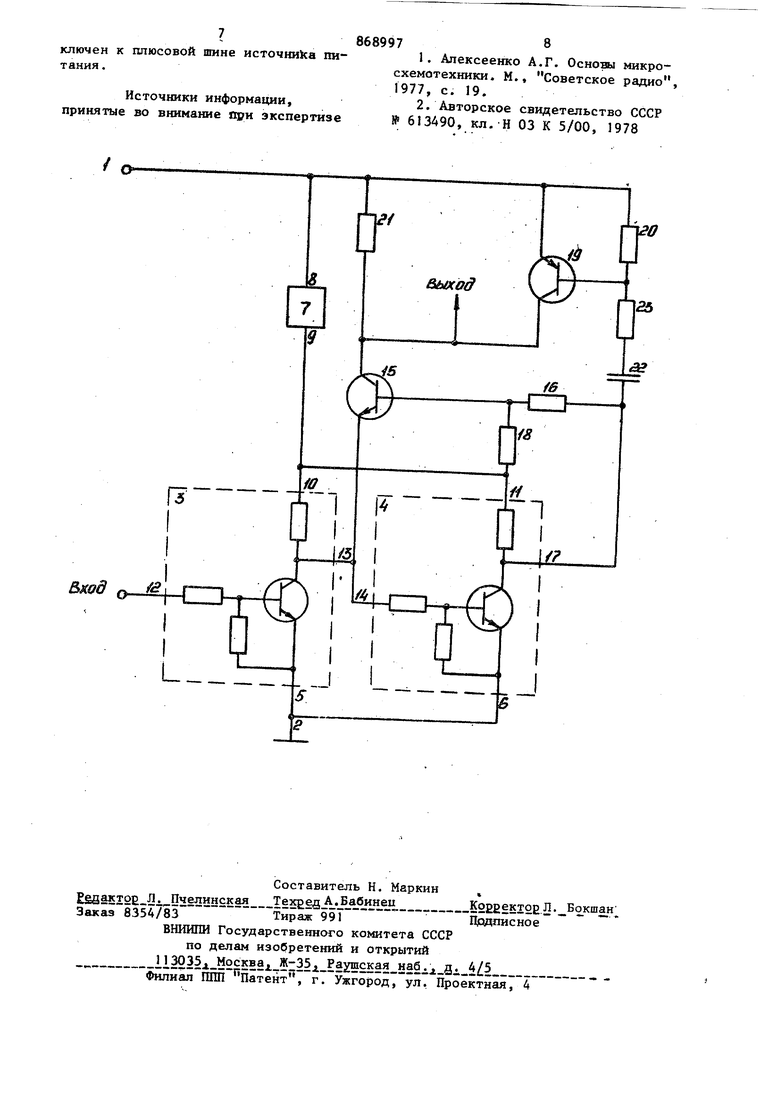

Изобретение относится к измерител ной технике и может быть использовано, например, в оконечных каскадах устройств импульсной техники для фор мирования управляющих сигналов необх димой амплитуды. Известны схемы формирования сигна лов требуемой амплитуды, выполненные в виде биполярных транзисторно-резис тивных инверторов fl . Недостатком такого устройства явл ется снижение его быстродействия изза переходного процесса при запирании схемы, причем увеличение номинал сопротивления коллекторного резистора приводит к ухудшению быстродействия устройства, а его уменьшение к повьшению энергопотребления вследствие увеличения тока коллектора открытого транзистора. Наиболее близок к предлагаемому по технической сущности преобразователь уровней, содержащий первый инвертор, вход которого соединен с шиной входных сигналов, а первый вход питания - с шиной нулевого потенциала и транзистор с Проводимостью р-п-р-типа, коллектором подключенный к выходной шине, эмиттером - к шине источника питания, а базой через первый и второй резисторы - к первой обкладке конденсатора и шине источника питания соответственно 2. Недостатком данного преобразователя уровней является то, что во время прохождения заднего фронта входного сигнала возникает сквозной ток между плюсовой и минусовой шинами питания, протекакиций через открытые переходы коллектор-эмиттер транзистора и транзистора, входящего в состав инвертора, в момент, когда произошло отпирание транзистора, а транзистор инвертора еще не заперт. Задержка запирания транзистора инвертора связана с рассасыванием неосновных носителей в активной и пассивной областях его базы. Цель изобретения - повышение надежности за счет исключения появления сквозного тока работы преобразователя уровней. Поставленная цель достигается тем что в гфеобразователь уровней, содержащий первый инвертор, вход которого соединен с шиной входных сигналов, а первый вход питания - с шиной нулевого потенциала, и транзистор с проводимостью р-п-р-типа, коллекто ром подключенный к выходной шине, эмиттером - к шине источника питания а базой через первый и второй резист ры - к первой обкладке конденсатора ,и шине источника питания соответственно, введены преобразователь напря жения, дополнительный транзистор, тр тий, четвертый и пятый резисторы и второй инвертор, первый вход питания которого соединен с шиной нулевого п тенциала, второй вход питания - с вы гсодом преобразователя напряжения и вторым входом питания первого инвертора, выход - со второй обкладкой ко денсатора, а вход - с выходом первог инвертора и эмиттером дополнительног транзистора, коллектор которого соединен с выходной шиной и через третий резистор с плюсовой шиной источника питания, а база через четвертый и пятый резисторы соединена соответственно со второй обкладкой конденса тора и с выходом преобразователя напряжения, вход которого подключен к плюсовой шине источника питания. На чертеже представлена принципиальная схема преобразователя уровней Преобразователь уровней содержит шины 1 и 2 подключения источника питания, последовательно соединенные инверторы 3 и 4, первые входы питания которых 5 и 6 подключены к шине нулевого потенциала, при этом преобразователь 7 напряжения входом 8 под ключен к. шине 1 источника питания, а- выходом 9 - ко вторым входам питания 10 и 11 ийверторов 3 и 4, причем первый инвертор 3 подключен входом 1 ко входу устройства, а выходом 13 ко входу 14 второго инвертора 4 и к эмиттеру дополнительного транзистора 15 с проводимостью п-р-п-типа, эмиттером соединенного с выходом 13 первого инвертора 3, базой через резистор 16 - с выходом J7 второго нивертора 4 и через резистор 18 - с выходом преобразователя 7 напряжения а коллектором - с коллектором тран74зистора 19 с проводимостью р-п-р-типа, подключенного к шине 1 источника питания эмиттером непосредственно, а базой и коллектором через резисторы 20 и 2 соответственно. Кроме того, к базе транзистора 19 с-проводимостью р-п-р-типа подключен через конденсатор 22 и резистор 23 выход 17 второго инвертора 4. Преобразователь уровней работает следующим образом. На вход преобразователя уровней подается сигнал положительной полярности, который на выходе устройства преобразуется по амплитуде и инвертируется. Логической единице входного сигнала соответствует низкий уровень выходного напряжения, а логическому нулю - верхний уровень выходного напряжения, снимаемого с шины 1 источника питания относительно шины 2 нулевого потенциала. Первый и второй инверторы 3 и 4 запитываются от шины 2 нулевого потенциала, соединенной с первыми входами 5 и 6 питания инверторов 3 и 4, и от преобразователя 7 напряжения, на вход 8 которого подается напряжение шины 1 источника питания, а к выходу 9 подключены вторые входы 10 и 11 питания инверторов 3 и 4. Преобразователь 7 напряжения обеспечивает питание инвертора 3 и 4 требуемым напряжением. В исходном статическом режиме сигнал на входе преобразователя уровней отсутствует, и на вход 12 первого инвертора 3 подается низкий нулевой потенциал. Тогда высокий потенциал с выхода 13 первого инвертора 3 поступа т на вход 14 второго инвертора 4 и на эмиттер транзистора 15 с проводимостью п-р-п-типа, на базу которого через резистор 16 подается низкий потенциал с выхода 17 второго инвертора 4, а следовательно, дополнительный транзистор 15с проводимостью п-р-п-типа находится в запертом состоянии. Резистор 18, через который база дополнительного транзистора 15 подключена к выходу 9 преобразователя 7 напряжения, обеспечивает величину обратного напряжения между эмиттером и базой запертого дополнительного транзистора 15, не превьвпающую максимально допустимого для применяемого типа транзистора значения. Транзистор 19 с проводимостью р-р-р-типа в исходном состоянии заперт положительным потенциалом, поступаклцим на его базу через резистор 20. На выход преобразователя уровней в этом случае подается через резистор 21 высокий потенциал с шины 1 источника п тания, что соответствует отсутствию выходного сигнала. При подаче на вход преобразователя уровней, а следовательно, на вход 12 первого инвертора 3 высокого потенциала, соответствующего входном уровню логической единицы, сигнал, п ступающий с выхода 13 первого инвертора 3 на эмиттер дополнительного транзистора 15 с проводимостью п-р-п типа и на вход 14 второго инвертора 4, принимает низкое нулевое значе ние , Сигнал положительной полярности с выхода 17 второго инвертора 4 пост пает через резистор 16 на базу допол нительного транзистора 15 с проводимостью п-р-п-типа, отпирая его, и че рез конденсатор 22 и резистор 23 - н базу транзистора 19 с проводимостью р-п-р-типа, который продолжает оставаться в запертом состоянии. При отпирании дополнительного транзистора с проводимостью п-р-п-типа на выходе преобразователя уровней, к которому подключен коллектор этого транзистора, устанавливается низкий нулевой потенциал, что соответствует появлению выходного сигнала. По окончании входного сигнала на выходе 13 первого инвертора 3 устанавливается высокий потенциал, поступакщий на эмиттер транзистора 15 с проводимостью п-р-п-типа и на вход 14 второго инвертора 4. Низким потенциалом с выхода 17 второго инвертора 4 через резистор 16 запирает ся дополнительный транзистор с. проводимостью п-р-п-типа и преобразователь уровней переходит в исходно положение. Транзистор 19 с проводимостью р-п-р-типа отпирается только на время прохождения заднего фронта входного сигнала отрицательным перепадом напряжения, поступаклцим на его базу с выхода 17 второго инвертора 4 через ковденсатор 22 и резистор 23. Шунтируя резист9Р 21 во время формирования заднего фронта выход ного сигнала, транзистор 19 с проводимостью р-п-р-,типа увеличивает крутизну этого фронта. Таким образом, транзистор 19 с проводимостью р-п-р-типа отпирается тем же сигналом с выхода 17 второго инвертора 4, которым запирается дополнительный транзистор 15 с проводимостью п-р-п-типа. Однако к этому моменту времени на выхрде 13 первого инвертора 3, к которому подключен эмиттер дополнительного аранзистора 15 с проводимостью п-р-п-типа, уже устанавливается высокий потенциал. При использовании, например, инверторов, построенных по приведьнной на чертеже схеме, входящий в состав первого инвертора 3 транзистор с проводимостью rt-p-n-тига в этот момент времени уже заперт. Следовательно, как в статическом исходном состоянии, так и в моменты прохождения входного сиглала в предлагаемом устройстве не возникает сквозного тока между плюсовой и минусовой шинами питания, что повышает надежность преобразования уровней. Формула изобретения Преобразователь уровней, содержащий первый инвертор, вход которого соединен с шиной входных сигналов, а первый вход питания - с шиной нулевого потенциала, и транзистор с проводимостью р-п-р-типа, коллекторном подключенный к выходной шине, эмиттером - к шине источника питания, а базой через первый и второй резисторы - к первой обкладке конденсатора и шине источника питания соответстйенно, отличающийся тем, что, с целью повьпиения надежности засчет исключения появлений сквозного тока, в него введены преобразователь напряжения, дополнительный транзистор, третий, четвертьй и пятый резисторы и второй инвертор, первый вход питания которого соединен с шиной нулевого потенциала, второй вход питания - с выходом преобразователя напряжения и вторым входом питания первого инвертора, выход - с второй обкладкой конденсатора, а вход - с выходом первого инвертора и эмиттером ополнительного транзистора, коллектор которого соединен с выходной и ерез третий резистор с ш.дасовой шинаи источника питания, а база через етвертый и пятый резисторы подклюена соответственно к второй обклад- е конденсатора и выходу преобразоваеля напряжения. вход которого ключей к плюсовой шине источника питания. Источники информации, принятые во внимание при экспертизе 868997® 1. Алексеенко А.Г. Основы микросхемотехники. М., Советское радио, 1977, с. 19. 2. Авторское свидетельство СССР № 613490, кл.-Н 03 К 5/00, 1978

Авторы

Даты

1981-09-30—Публикация

1980-01-02—Подача