11

Изобретение относится к промышленности средств связи и может быть использовано в качестве передатчика электрических сигналов через кабель- нуга магистраль.

Целью изобретения является увеличение быстродействия, увеличение функциональных возможностей за счет обеспечения четырех режимов работы, улучшение энергетических характеристик за счет уменьшения сквозного тока.

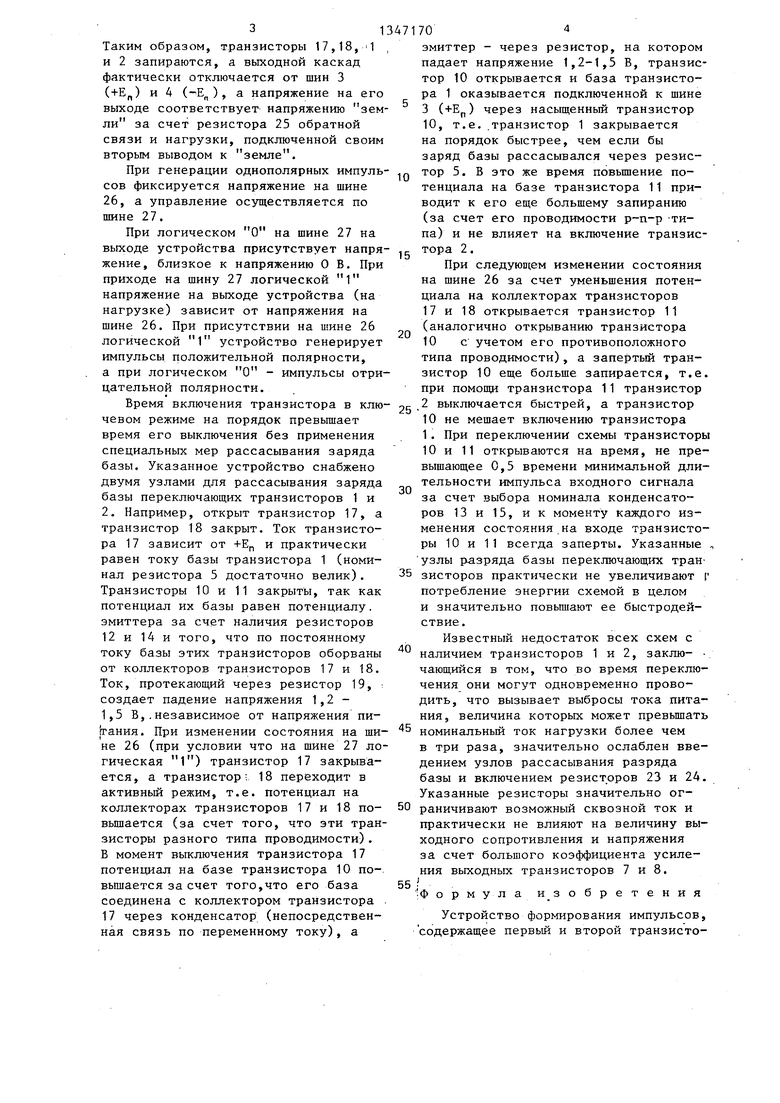

На чертеже приведена электрическая принципиальная схема устройства,

Устройство формирования импульсов содержит транзисторы 1 и 2 разных типов проводимости, эмиттеры которых соединены соответственно с положительной 3 и отрицательной 4 шинами источника питания, а базы подключены к первым выводам соответствующего первого 5 и в торого 6 резисторов, третий 7 и четвертый 8 транзисторы выходного каскада разного типа прово димости, коллекторы которых соединен соответственно с положительной 3 и отрицательной 4 шинами источника питания, базы их соединены между со

бой, эмиттеры их соединены между собой и подключены к выходной шине 9 устройства, пятый 10 и шестой 11 транзисторы разных типов проводимости, база пятого транзистора 10 подключена к первому выводу третьего резистора 12 и первой обкладке пер- вого конденсатора 13, база шестого транзистора 11 подключена к первому выводу четвертого резистора 14 и первой обкладке второго конденсатора 15

Кроме того, устройство содержит логический расширитель 16, седьмой 17 и восьмой 18 транзисторы, пятый 19, шестой 20, седьмой 21, восьмой 22, девятьш 23, десятый 24 и одиннадцатый 25 резисторы, причем первый и второй входы логического расширителя 16 подключены соответственно к первой 26 и второй 27 входной шинам устройства, а первый и второй выходы логического расширителя 16 соединены с базами соответствующего седьмого 17 и восьмого 18 транзисторов, эмиттер седьмого транзистора 17 подключен через шестой резистор 20 к общей шине второго источника питания, кол- лектор седьмого транзистора 17 соединен с второй обкладкой первого конденсатора 13 и с первым выводом пя

Q

ц

5

0

5

0 5

1702

того резистора 19, второй вывод которого подключен к второму выводу третьего резистора 12, первому выводу первого резистора 5 и эмиттеру пятого трднзистора 10, коллектор которог го подключен к второму выводу первого резистора 5 и соединен с эмиттером первого транзистора 1, коллектор которого подключен через девятый резистор 23 к базе третьего транзистора 7 и первому выводу одиннадцатого резистора 25, второй вывод которого соединен с выходной шиной 9 устройства, эмиттер восьмого транзистора 18 подключен через седьмой резистор 21 к положительной шине 26 второго и.сточника питания, коллектор восьмого транзистора 18 соединен с второй обкладкой второго конденсатора 15 и с первым выводом восьмого резистора 22, второй вывод которого подключен квторому выводу четвертого резистора 14, первому выводу второго резистора 6 и эмиттеру шестого транзистора 11, коллектор которого под-г i ключен к второму выводу второго резистора 6 и соединен с эмиттером второго транзистора 2, коллектор которого подключен через десятый резистор 24 к базе четвертого транзистора 8.

Устройство работает следующим образом.

Если на шине 27 логического расширителя 16 присутствует логическая 1, то напряжение на первом и втором выходах соответствует напряжению на шине 26. При присутствии логической 1 на шине 26 управляющей транзистор 17 открывается и переходит в режим стабилизации тока, определяемого напряжением на его базе и номиналом резистора 20. Транзистор 18 закрыт, В этом случае транзистор 1 открывается и переходит в состояние насыщения, а транзистор 2 запирается. На выходе устройства формирования импульсов присутствует напряжение, близкое к +Е. При приходе на шину 26 логического О наоборот в режим генератора тока переходит транзистор 18, а транзистор 17 запи- рается. Транзистор 2 открыт и насыщен, а транзистор 1 заперт. На вкходе устройства напряжение, близкое к ..

При приходе на шину 26 логического О на втором выходе устанавливается напряжение логической 1, а на первом выходе - логического О,

3

Таким образом, транзисторы 17,18, и 2 запираются, а выходной каскад фактически отключается от шин 3 (+Е„) и 4 (Е), а напряжение на выходе соответствует напряжению ли за счет резистора 25 обратной

связи и нагрузки, подключенной своим вторым выводом к земле.

При генерации однополярных импульсов фиксируется напряжение на шине 26, а управление осуществляется по шине 27.

При логическом О на шине 27 на выходе устройства присутствует напряжение, близкое к напряжению О В. При приходе на шину 27 логической Г напряжение на выходе устройства (на нагрузке) зависит от напряжения на шине 26. При присутствии на шине 26 логической 1 устройство генерирует импульсы положительной полярности, а при логическом О - импульсы отрицательной полярности.

Время включения транзистора в ключевом режиме на порядок превьш1ает время его выключения без применения специальных мер рассасывания заряда базы. Указанное устройство снабжено двумя узлами для рассасывания заряда базы переключающих транзисторов 1 и 2. Например, открыт транзистор 17, а транзистор 18 закрыт. Ток транзистора 17 зависит от +Ер и практически равен току базы транзистора 1 (номинал резистора 5 достаточно велик). Транзисторы 10 и 11 закрыты, так как потенциал их базы равен потенциалу. эмиттера за счет наличия резисторов 12 и 14 и того, что по постоянному току базы этих транзисторов оборваны от коллекторов транзисторов 17 и 18. Ток, протекающий через резистор 19, создает падение напряжения 1,2 - 1,5 В,.независимое от напряжения пи- рания. При изменении состояния на ши не 26 (при условии что на шине 27 ло гическая 1) транзистор 17 закрывается, а транзистор; 18 переходит в активньй режим, т.е. потенциал на коллекторах транзисторов 17 и 18 повышается (за счет того, что эти тран зисторы разного типа проводимости). В момент выключения транзистора 17 потенциал на базе транзистора 10 повышается за счет того,что его база соединена с коллектором транзистора 17 через конденсатор (непосредственная связь по переменному току), а

10

15

20

25

30

35

40

45

50

эмиттер - через резистор, на котором падает напряжение 1,2-1,5 В, транзистор 10 открывается и база транзистора 1 оказывается подключенной к шине 3 (+Ер) через насыщенный транзистор

55

10, т.е. .транзистор 1 закрывается на порядок быстрее, чем если бы заряд базы рассасывался через резистор 5. В это же время повьш1ение потенциала на базе транзистора 11 приводит к его еще большему запиранию (за счет его проводимости р-п-р -типа) и не влияет на включение транзистора 2.

При следующем изменении состояния на шине 26 за счет уменьшения потенциала на коллекторах транзисторов 17 и 18 открывается транзистор 11 (аналогично открыванию транзистора 10 с учетом его противоположного типа проводимости), а запертый транзистор 10 еще больше запирается, т.е. при помощи транзистора 11 транзистор 2 выключается быстрей, а транзистор 10 не мешает включению транзистора 1. При переключении схемы транзисторы 10 и 11 открываются на время, не превышающее 0,5 времени минимальной длительности импульса входного сигнала за счет выбора номинала конденсаторов 13 и 15, и к моменту каждого изменения состояния на входе транзисторы 10 и 11 всегда заперты. Указанные , узлы разряда базы переключающих транзисторов практически не увеличивают ( потребление энергии схемой в целом и значительно повьш ают ее быстродействие.

Известный недостаток всех схем с наличием транзисторов 1 и 2, заклю- чающийся в том, что во время переключения они могут одновременно проводить, что вызывает выбросы тока питания, величина которых может превьш1ать номинальный ток нагрузки более чем в три раза, значительно ослаблен введением узлов рассасывания разряда базы и включением резисторов 23 и 24. Указанные резисторы значительно ограничивают возможный сквозной ток и практически не влияют на величину выходного сопротивления и напряжения за счет большого коэффициента усиления выходных транзисторов 7 и 8. J

Формула изобретения

Устройство формирования импульсов, содержащее первый и второй транзисто513

ры разных типов проводимости, эмиттеры которых соединены соответственно с положительной и отрицательной шинами источника питания, а базы подключены к первым выводам соответствующего первого и второго резисторов, третий и четвёртый транзисторы выходного каскада разного типа проводимости, коллекторы которых соединены соответ- .ственно с положительной и отрицательной шинами источника питания, базы их соединены между собой, эмиттеры их соединены между собой и подключены к выходной шине устройства, пятый и ; шестой транзисторы разных типов проводимости, база пятого транзистора подключена к первому выводу третьего резистора и первой обкладке первого конденсатора, база шестого транзистора подключена к первому выводу чет- : вертого резистора и первой обкладке второго конденсатора, отличающееся тем, что, с целью увеличения быстродействия, увеличения функциональных возможностей за счет обеспечения четырех режимов работы, улучшения энергетических характеристик за счет уменьшения сквозного тока, в него введены логический расши

ритель, седьмой и восьмой транзисто- ры, пятый-. И шестой, седьмой и восьмой, девятый и десятый и одиннадцатый резисторы, причем первый и второй входы логического расширителя подключены соответственно к первой и второй входным шинам устройства, а первьш и второй выходы логического расширителя соединены с базами соответствующего седьмого и восьмого транзисторов, эмиттер седьмого транРедактор И. Шулла Заказ 5127/51

Составитель В. Чижиков Техред И,Попович

Корректор

Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

g 5

0

0

5

0

706

зистора подключен через шестой резистор к общей шине второго источника питания, коллектор седьмого транзистора соединен с второй обкладкой первого : конденсатора и с первьм выводом пятого резистора, второй вьтод которого подключен к второму выводу третьего резистора, первому выводу первого резистора и эмиттеру пятого транзистора, коллектор которого подключен к второму выводу первого резистора и соединен с эмиттером первого транзистора, коллектор которого подключен через девятый резистор к базе третьего транзистора и первому выводу одиннадцатого резистора, второй вывод которого соединен с выходной шиной устройства, эмиттер восьмого транзистора подключен через седьмой резистор к положительной шине второго источника питания, коллектор .восьмого транзистора соединен с второй обкладкой второго конденсатора и с первым выводом восьмого резистора, второй вывод которого подключен к второму выводу четвертого резистора,. первому выводу второго резистора и эмиттеру шестого транзистора, коллектор которого подключен к второму выводу второго резистора и с оединен с эмиттером второго транзистора, кол-..к лектор которого подключен через десятый резистор к базе четвертого транзистора, третий, пятый и седьмой транзисторы одного типа проводимости, первьш транзистор другого типа проводимости, при этом второй, третий, пятьм, седьмой транзисторы имеют один тип проводимости.

Корректор М. Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный ключ с защитой от перегрузки | 1986 |

|

SU1398084A1 |

| Двухтактный ключ переменного напряжения | 1987 |

|

SU1448405A1 |

| Усилитель-инвертор | 1987 |

|

SU1429310A1 |

| Транзисторный ключ | 1991 |

|

SU1780179A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ | 2002 |

|

RU2231213C2 |

| Формирователь импульсов | 1990 |

|

SU1746519A1 |

| Транзисторный переключатель | 1984 |

|

SU1167723A1 |

| ТРОИЧНЫЙ ТРИГГЕР | 2003 |

|

RU2237968C1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ С ЗАЩИТОЙ ОТ КОРОТКОГО ЗАМЫКАНИЯ | 2000 |

|

RU2167492C1 |

| Реверсивный мультивибратор | 1984 |

|

SU1202035A1 |

Изобретение относится к средствам связи и может быть использовано в качестве передатчика электрических сигналов через кабельную магистраль. Цель изобретения - увеличение быстродействия и расширение функциональных возможностей - достигается за счет обеспечения четьфех режимов работы устройства. З лучшение энергетических характеристик достигается за счет уменьшения сквозного тока. Для этого в устройство дополнительно введены логический расширитель 16, два транзистора 17 и 18 и резисторы 19 - 25. Кроме того, устройство со держит транзисторы 1 и 2, 7 и 8 и 11 и 12 разного типа проводимости, шины 3 и 4 источника питания,резисторы 5и6и12и14, выходную шину 9, конденсаторы 13 и 15, шину 26. В устройстве значительно ослаблены выбросы тока при переключении транзисторов в результате введения узлов рассасывания тока разряда базы. 1 ил. (Л с: оЗ

| Бол Дж | |||

| и др | |||

| Схема преобразования логических уровней | |||

| - Электроника, т | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Устройство формирования импульсов | 1979 |

|

SU797058A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1986-01-03—Подача