(54) УСТРОЙСТГЗО ПЕРЕСЧЕТА НА ТРИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Троичное счетное устройство | 1986 |

|

SU1338013A1 |

| Троичное счетное устройство | 1986 |

|

SU1415432A1 |

| Троичное счетное устройство | 1975 |

|

SU579690A1 |

| Троичный счетный триггер | 1987 |

|

SU1422405A1 |

| Троичное счетное устройство | 1988 |

|

SU1580535A2 |

| Устройство пересчета на три | 1973 |

|

SU506132A1 |

| Делитель частоты импульсов на пять на потенциальных элементах и-не/ или-не | 1974 |

|

SU525250A1 |

| Троичное счетное устройство | 1988 |

|

SU1506547A1 |

| Распределитель сигналов на десять каналов | 1986 |

|

SU1325683A1 |

| Формирователь импульсов | 1984 |

|

SU1231590A1 |

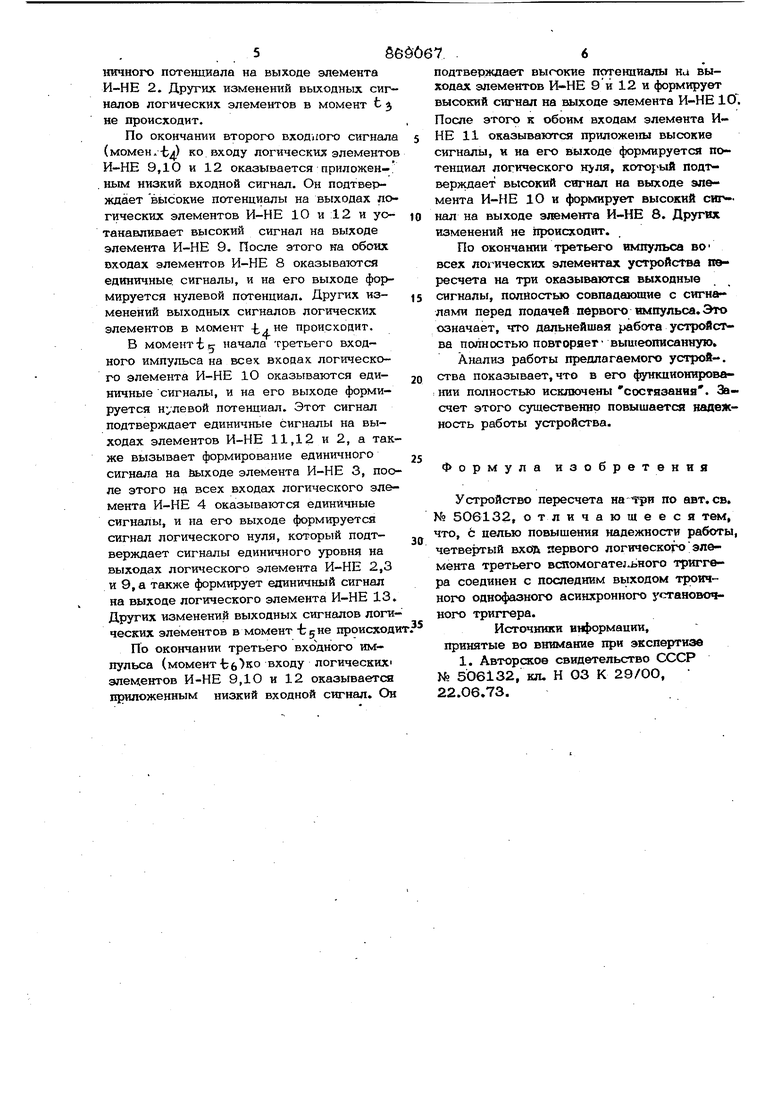

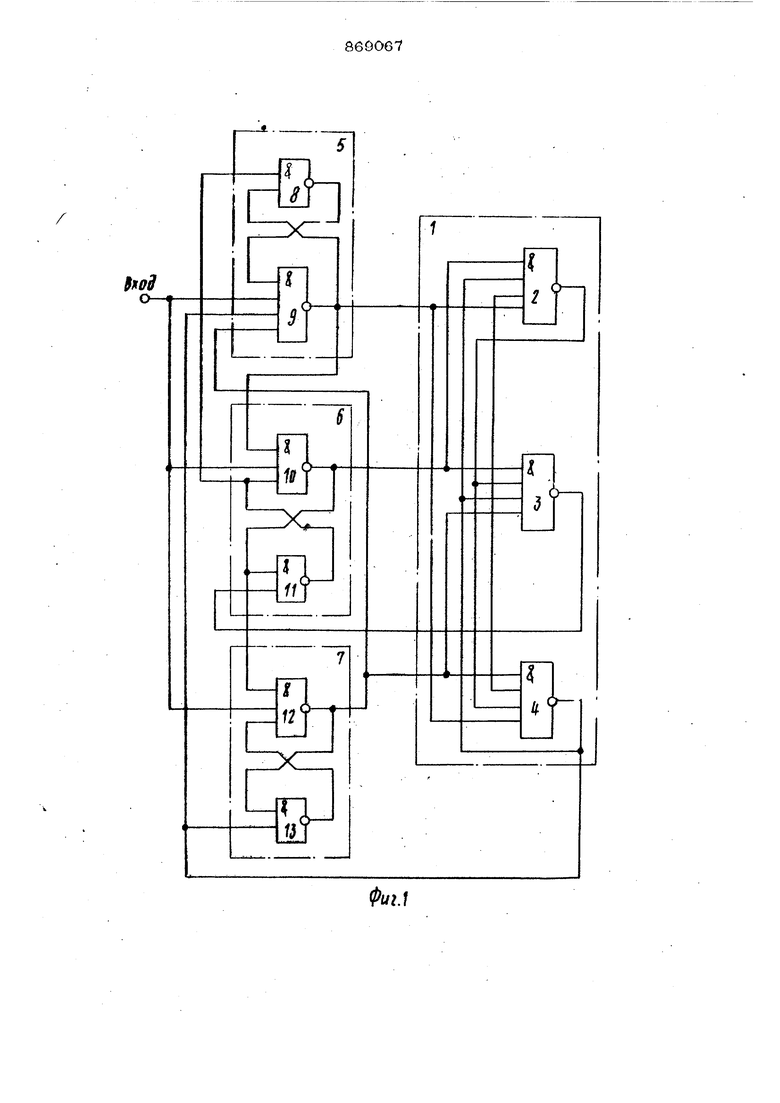

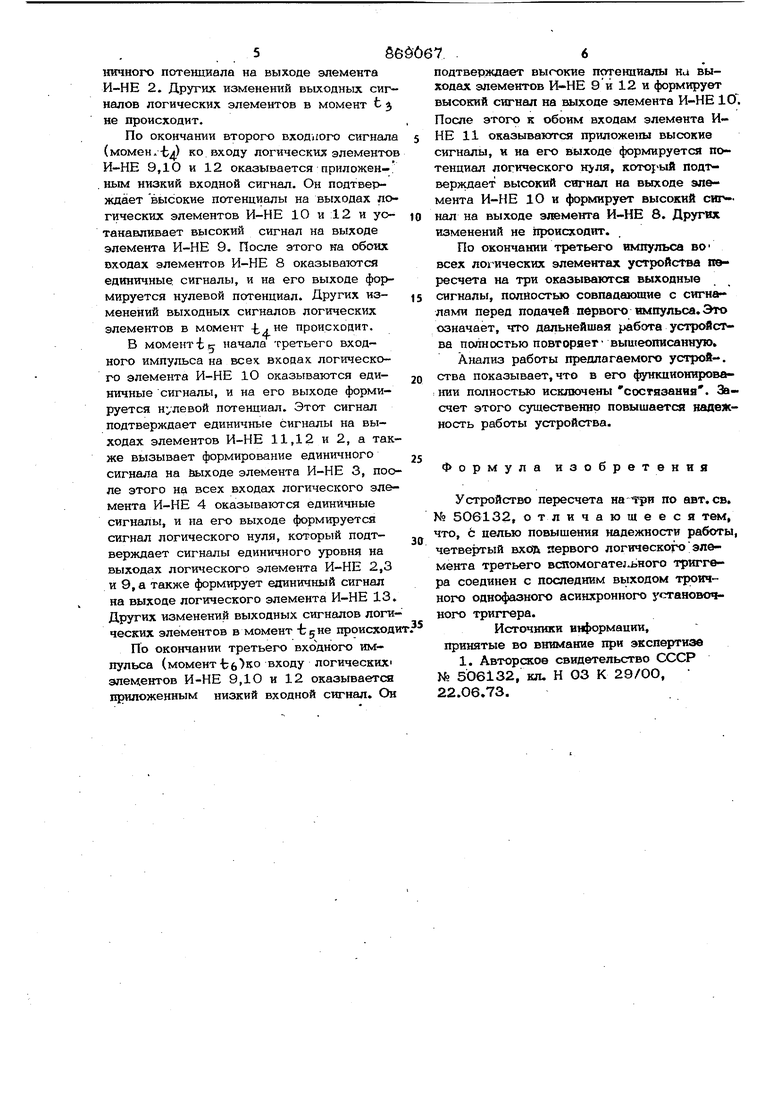

Изобретение относится к импульсной технике и может быть использовано в раз личных устройствах автоматики и вычислительной техники, По основному авт. св. № 5О6132 известно устройство пересчета на три, выполненное по несимметричной схеме, содержащее ши1гу запуска, троичный однофазный асинхронный уствновочпый триггер и три вспомогательных триггера, каж дый из которых выполнен на двух логичесжих элементах И-НЕ (ИЛИ-НЕ) с перекрестными обратными связями, причем выход логического элемента каждого вспомогательного триггера соединен со входом аналогичного элемента последующего вспо могательного триггера и с соответствующим установочным входом троичного однофазного асинхронного триггера, выходы двух логических элементов которого подключены ко входам вторых логических эле ментов соответствующих двух вспомогательных триггеров, вход второго логичеокого элемента третьего вспомогательного триггера соединен с выходом второго логического элемента последующего вспомогательного триггера, а третьи входы тюгических элементов всех вспомогательных триггеров подключены к щине запуска l. Данное несимметричное построение устройства определяет его достаточно щирокие функциональные возможности. Среди сигналов на выходах логических элементов этого устройства существуют не только три сигнала, иэменякнциеся (при выполнении устройства, например, на логических элементах И-НЕ) синфазно переднему 4)онту входного сигнала, но и один сипнал, меняющийся по заднему фронту входного сигнала. Это существенно облегчает построение счетных цепей на указанных устройствах. Цель изобретения - повышение надежности работы за счет полного исключения состязаний в фунвсдиошфовании устройства. Поставленная цель достигается тем, что в устройстве пересчета на три, содерншщем троичный однофазный асинхронный установочный триггер и три вспомогательных триггера, кажцый из которых выполнен на дву логических элементах И-НЕ (ИЛИ-НЕ), четвертый вход первого логического элемента третьего вспомогательного триггера соединен с последующим выходом троичного однофазного асинхронного установочного триггера. На фиг. 1 изображена схема устройств пересчета на три; на фиг. 2 - временные диаграммы его работы. При этом номер диаграммы показывает выходной сигнал логического элемента ИНЕ с тем же номером. Аналогичным образом может быть выполнена и схема на элементах ИЛИ-НЕ. Устройство содержит троичный однофазный асинхронный установочный триггер 1, выполненный на трех элементах И-НЕ (или ИЛИ-НЕ) 2,3 и 4; три вхо- да троичного однофазного асинхронного установочного триггера 1 подключеньт к выходам трех вспомогательных триггеров 5,6 и 7J. триггер 5 выполнен на двух логических элементах И-НЕ (ИЛИ-НЕ): двухвходовом 8 Y четырехвходовом 9, первые входы которь.х подключены к выходу другого элем П1та; триггер 6 выполнен на двух логическчх элементах И-НЕ (ИЛИ-НЕ трехвходовом Ю и двухвходовом 11, первые входы которых подключены к выходу другого эле1.1ента; триггер 7 выполнен на двух логических элементах И-НЕ(ИЛИ-НЕ трехвходовом 12 и двухвходовом 13; ко вторым входам логических элементов 9, 10 и 12 подключена шина запуска; выход элемента 9 соединен с третьим входом элемента 10, выход которого подклю чен к третьему входу элемента 12, выход которого соединен с .третьим входом элемента 9; выход элемента 3 подключен ко второму входу элемента 11, выход которого соединен со вторым входом элемента И-НЕ (ИЛИ-НЕ) 8; выход элемента 4 подключен ко второму входу элемента 13 и к четвертому входу элемента 9. Устройство работает следующим образом. Пусть в рассматриваемый момент времени троичный однофазный асинхронный. триггер 1 находится в состоянии, при ко тором на выходе его логических элементов 2 и 3 присутствуют единичные сигна лы, а на выходе логического элемента 4 нулевой. Если в рассматриваемый момент на вспомогательные триггеры 5,6 и 7 не подаются входные сигналы, т.е. на шине запуска имеет место низкий нулевой сигнал, то на выходе обоих логических элементов 8 и 9 вспомогательного триггера 5 оказываются единичные сигналы, на выходе логического элемента 10 триггера 6 присутствуют единичный сигнал, на выходе логического элемента 11 этого тригг- ра - нулевой, на выходах обоих логических элементов 12 и 13 триггера -7 высокие единичные сигналы. Рассматривается момент ± начала первого импульса, на шине запуска. При этом формируется низкий сигнал на выходе эле мента И-НЕ 12. Низкий сигнал не может быть сформирован на выходе элементов И-НЕ 10, так как на одном из его входов присутствует низкий сигнал с выхода элемента И-НЕ 11. Кроме того, на выходе элемента 9 не может сформироваться низкий сигнал, поскольку к его входу приложен нулевой уровень напряжения с .выхода элемента И-НЕ 4.После формирования низкого потенциала на выходе элемента И-НЕ 12 подтверждается высокий уровень сигналов на выходах элементов 9,13 и 3, и формируется высокий потенциал на выходе элемента И-НЕ 4. Его формирование не может изменить высоких выходных сигнал овна элементах И-НЕ 3, 9 и J.3, так как их поддерживает ранее сформированный низкий потенциал с выхода элемента И-НЕ 12, Но после формирования высокого сигнала на выходе элемента И-НЕ 4 на всех входах элемента И-НЕ 2 оказываются высокие сигналы, и на выходе этого логического элемента формируется низкий оигнал. Остальные сигналы на выходах логических элементов остаются неизменными. По окончании первого входного импульca(MOMeHTjfc2) ко входам элементов ИНЕ 9,10 и 12 оказывается приложенным низкий входной сигнал, который поддерживает высокие сигналы на выходах элементов И-НЕ 9 и 10 и устанавливает высокий сигнал на выходе логического элемента И-НЕ 12. После этого на обоих входах логического элемента И-НЕ 13 оказываются высокие сигналы, и на его выходе формируется низкий уровень вСапряжения. Остальные сигналы на выходах логических элементов устройства остаются неизменными. В момент -t начала второго входного импульса на всех вхоцах логического элемента 9 оказывак тся единичные сигналы, и на его выходе формируется нулевой потенциал. Этот сигнал Подтверждает высокие сигналы на вь1х6дах элементов И-НЕ 9,1 р и 4 и вызывает формирование еди

ичного потенциала на выходе элемента -НЕ 2. Других изменений выходных сигалов логических элементов в момент t 3 не происходит.

По окончании второго входного сигнала 5 (моменл-tj}) ко входу логических элементов -НЕ 9,10 и 12 оказывается приложеным низкий входной сигнал. Он подтверждает высокие потенциалы на выходах логических элементов И-НЕ 10 и 12 и уо Q анавливает высокий сигнал на выходе элемента И-НЕ 9. После этого на обоих входах элементов И-НЕ 8 оказываются диничные, сигналы, и на его выходе фор мируется нулевой потенциал. Других из- 5 менений выходных сигналов логических элементов в момент происходит.

В момент i начала третьего входного импульса на всек вкодах логического элемента И-НЕ 10 оказываются еди- JQ ничные сигналы, и на его выходе формируется нулевой потенциал. Этот сигнал подтверждает единич шю сигналы на выходах элементов И-НЕ 11,12 и 2, а также вызывает формирование единичногоjj сигнала на йыходе элемента И-НЕ 3, после этого на всех входах логического элемента И-НЕ 4 оказываются единичные сигналы, и на его выходе формируется сигнал логического нуля, который подтверждает сигналы единичного уровня на выходах логического элемента И-НЕ 2,3 и 9, а также формирует единичный сигнал на выходе логического элемента И-НЕ 13, Других изменений выходных сигналов логических элементов в момент -fcjHe происходит

По окончании третьего входного импульса (моментЬб)ко входу логических элементов И-НЕ 9,1О и 12 оказывается приложенным низкий входной сигнал. Он

подтверждает выгюкие потенциалы на выходах элементов И-НЕ 9 и 12 и формирует высокий сигнал на выходе элемента И-НЕ 10 После этого к обоим входам элемента ИНЕ 11 оказываются приложены высокие сигналы, и на его выходе формируется потенциал логического нуля, кoтoI ый подтверждает высокий сигнал на выходе элемента И-НЕ 10 и формирует высокий сигнал на выходе элемента И-НЕ 8. Других изменений не происходит.

По окончании третьего импульсе во всех логических элементах ycrpoftctBa пересчета на три оказывахугсв выходные сигналы, полностью совпадающие с cvtrHaлами перед подачей первого вмпульса. Это означает, что дальнейшая работа устройства полностью повторяет вышеописанную.

Анализ работы предлагаемого устрой-. ства показывает, что в его функционирова: НИИ полностью исключены состязания. За- счет этого существенно повышается надежность работы устройства.

Формула изобретения

Устройство пересчета натри по авт.св. № 506132, отличающееся тем, что, 6 целью повышения надежности работы четве угый вхой первого логическотч); элемента третьего вспомогате; ьного триггера соединен с последним выходом троичного однофазного асинхронного установочного триггера.

Источники информации, принятые во внимание при экспертизе

i if tZ tS ttf tS tS

Jf

Г

фиг.2

Авторы

Даты

1981-09-30—Публикация

1980-01-24—Подача