(54) ФАЗОЧАСТОТНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Измерительный преобразователь активной и реактивной составляющих синусоидального тока | 1990 |

|

SU1748079A1 |

| Цифровой фазометр-частотомер | 1980 |

|

SU918884A1 |

| Фазометр | 1985 |

|

SU1273837A1 |

| СПОСОБ СДВИГА ФАЗЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2141165C1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| Устройство для опознавания железнодорожных вагонов | 1988 |

|

SU1558753A1 |

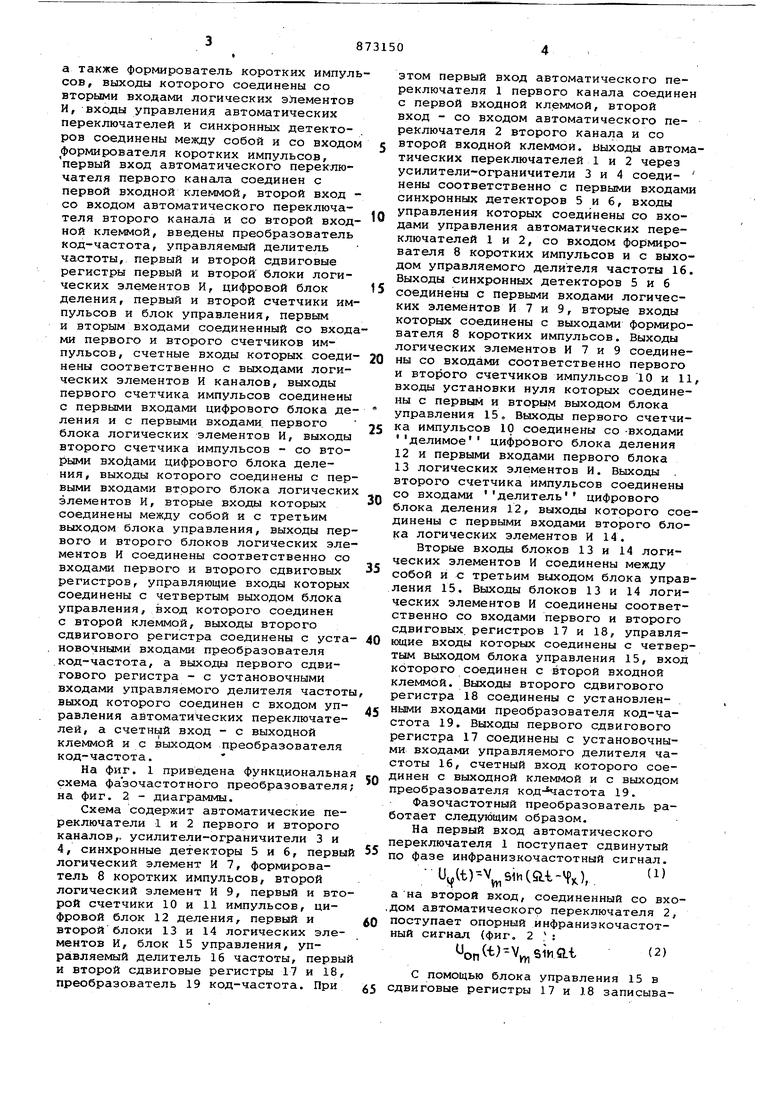

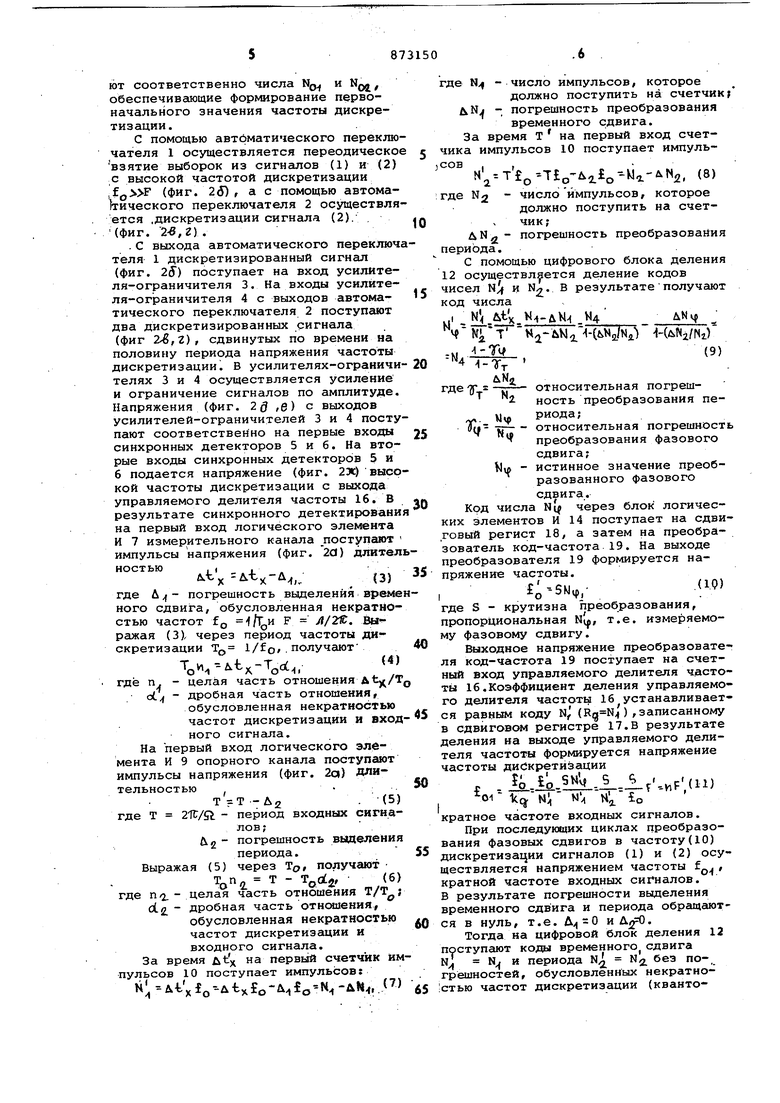

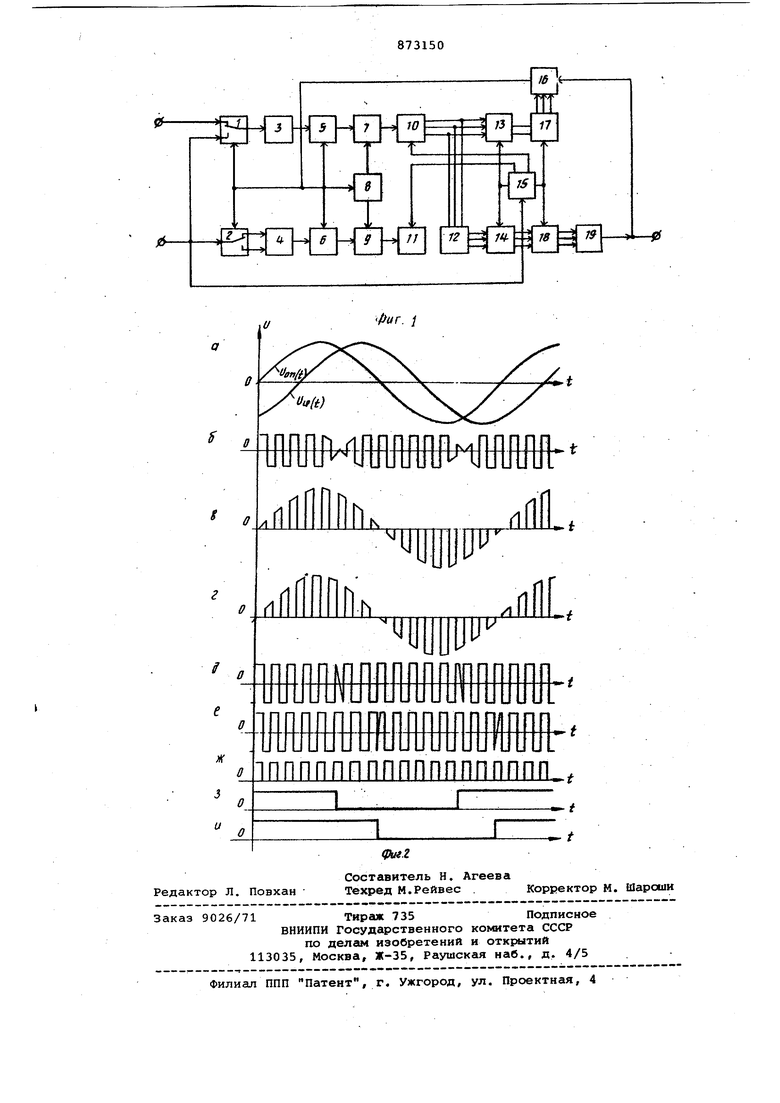

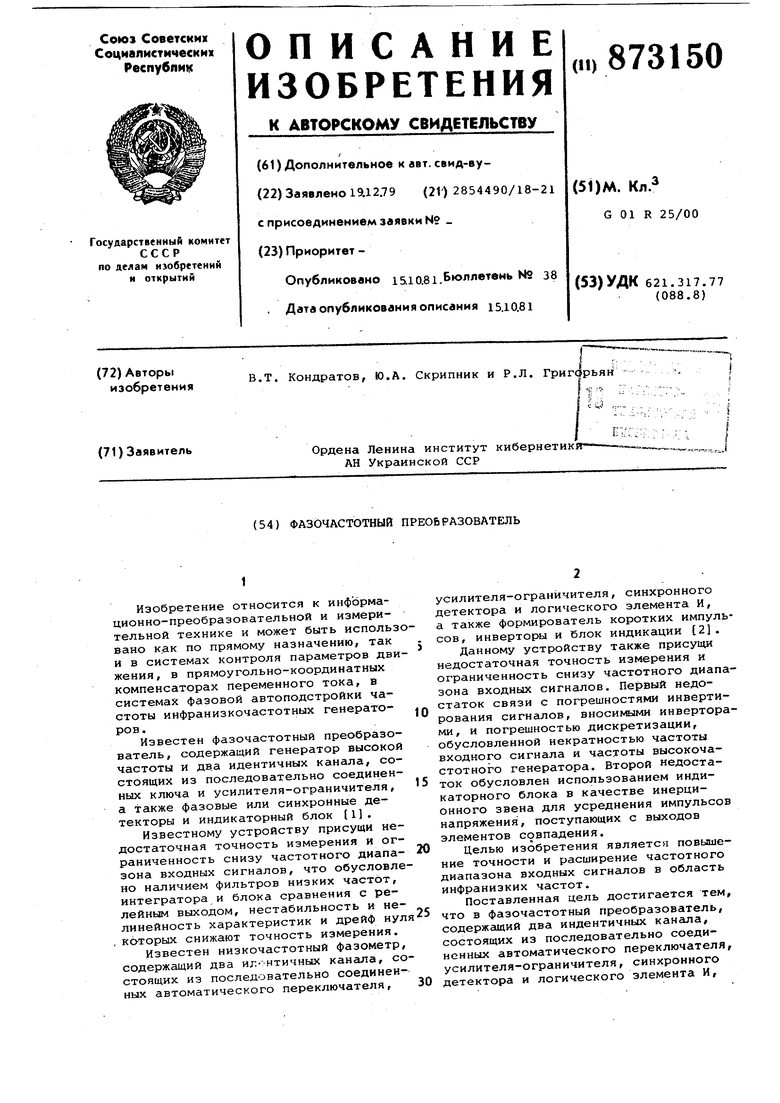

Изобретение относится к информационно-преобразовательной и измерительной технике и может быть исполь вано к,ак по прямому назначению, так и в системах контроля параметров дв жения, в прямоугольно-координатных компенсаторах переменного тока, в системах фазовой автоподстройки частоты инфранизкочастотных генераторов. Известен фазочастотный преобразователь, содержащий генератор высокой частоты и дв.а идентичных канала, состоящих из последовательно соединенных ключа и усилителя-ограничителя, а также фазовые или синхронные детекторы и индикаторный блок 11. Известному устройству присущи недостаточная точность измерения и ограниченность снизу частотного диапазона входных сигналов, что обусловле но наличием фильтров низких частот, интегратора и блока сравнения с релейным выходом, нестабильность и нелинейность характеристик и дрейф нул которых снижают точность измерения. Известен низкочастотный фазометр, содержащий два илонтичных канала, со стоящих из последовательно соединенных автоматического переключателя, усилителя-ограничителя, синхронного детектора и логического элемента И, а также формирователь коротких импульсов, инверторы и блок индикации 2. Данному устройству также присущи недостаточная точность измерения и ограниченность снизу частотного диапазона входных сигналов. Первый недостаток связи с погрешностями инвертирования сигналов, вносимыми инверторами, и погрешностью дискретизации, обусловленной некратностью частоты входного сигнала и частоты высокочастотного генератора. Второй недостаток обусловлен использованием индикаторного блока в качестве инерционного звена для усреднения импульсов напряжения, поступающих с выходов элементов совпадения. Целью изобретения является повышение точности и расширение частотного диапазона входных сигналов в область инфранизких частот. Поставленная цель достигается тем, что в фазочастотный преобразователь, содержащий два индентичных канала, состоящих из последовательно соединенных автоматического переключателя, усилителя-ограничителя, синхронного детектора и логического злемента И, а также формирователь коротких импуль сов, выходы которого соединены со вторыми входами логических элементов И, входы управления автоматических переключателей и синхронных детекторов соединены между собой и со входом формирователя коротких импульсов, первый вход автоматического переключателя первого канала соединен с первой входной клеммой, второй вход со входом автоматического переключателя второго канала и со второй вход ной клеммой, введены преобразователь код-частота, управляемый делитель частоты, первый и второй сдвиговые регистры первый и второй блоки логических элементов И, цифровой блок деления, первый и второй счетчики им пульсов и блок управления, первым и вторым входами соединенный со вход ми первого и второго счетчиков импульсов, счетные входы которых соеди нены соответственно с выходами логических элементов И каналов, выходы первого счетчика импульсов соединены с первыми входами цифрового блока де ления и с первыми входами первого блока логических элементов И, выходы второго счетчика импульсов - со вторыми входами цифрового блока деления, выходы которого соединены с пер выми входами второго блока логически элементов И, вторые входы которых соединены между собой и с третьим выходом блока управления, выходы пер вого и второго блоков логических эле ментов И соединены соответственно со входами первого и второго сдвиговых регистров, управляющие входы которых соединены с четвертым выходом блока управления, вход которого соединен с второй клеммой, выходы второго сдвигового регистра соединены с уста . новочнымй входами преобразователя код-частота, а выходы первого сдвигового регистра - с установочными входами управляемого делителя частот выход которого соединен с входом управления автоматических переключателей, а счетный вход - с выходной клеммой и с выходом преобразователя код-частота. На фиг. 1 приведена функциональна схема фазочастотного преобразователя на фиг. 2 - диаграммы. Схема содержит автоматические переключатели 1 и 2 первого и второго каналов,, усилители-ограничители 3 и 4, синхронные детекторы 5 и 6, первы логический элемент И 7, формирователь 8 коротких импульсов, второй логический элемент И 9, первый и вто рой счетчики 10 и 11 импульсов, цифровой блок 12 деления, первый и второй блоки 13 и 14 логических элементов И, блок 15 управления, управляемый делитель 16 частоты, первы и второй сдвиговые регистры 17 и 18, преобразователь 19 код-частота. При этом первый вход автоматического переключателя 1 первого канала соединен с первой входной клеммой, второй вход - со входом автоматического переключателя 2 второго канала и со второй входной клеммой, выходы автоматических переключателей 1 и 2 через усилители-ограничители 3 и 4 соединены соответственно с первыми входами синхронных детекторов 5 и 6, входы управления которых соединены со входами управления автоматических переключателей 1 и 2, со входом формирователя 8 коротких импульсов и с выходом управляемого делителя частоты 16. Выходы синхронных детекторов 5 и б соединены с первыми входами логических элементов И 7 и 9, вторые входы которых соединены с выходами формирователя 8 коротких импульсов. Выходы логических элементов И 7 и 9 соединены со входами соответственно первого и второго счетчиков импульсов 10 и 11, входы установки нуля которых соединены с первым и вторым выходом блока управления 15, Выходы первого счетчика импульсов 10 соединены со -входами делимое цифрового блока деления 12и первыми входами первого блока 13логических элементов И. Выходы второго счетчика импульсов соединены со входами делитель цифрового блока деления 12, выходы которого соединены с первыми входами второго блока логических элементов И 14, Вторые входы блоков 13 и 14 логических элементов И соединены между собой и с третьим выходом блока управления 15. Выходы блоков 13 и 14 логических элементов И соединены соответственно со входами первого и второго сдвиговых, регистров 17 и 18, управляющие входы которых соединены с четвертым выходом блока управления 15, вход которого соединен с второй входной клеммой. Вькоды второго сдвигового регистра 18 соединены с установленными входами преобразователя код-частота 19. Выходы первого сдвигового регистра 17 соединены с установочными входами управляемого делителя частоты 16, счетный вход которого соединен с выходной клеммой и с выходом преобразователя код- частота 19. Фазочастотный преобразователь работает следующим образом. На первый вход автоматического переключателя 1 поступает сдвинутый по фазе инфранизкочастотный сигнал. V)-- sihCai-4,c),. а на второй вход, соединенный со вхо,дом автоматического переключателя 2, поступает опорный инфранизкочастотный сигнал (фиг. 2 . : UonC-b V SiVfl-t (2) с помощью блока управления 15 в сдвиговые регистры 17 и 18 записывают соответственно числа NQ и NQ , обеспечивающие формирование первоначального значения частоты дискретизации. С помощью автбматического переклю чателя 1 осуществляется переодическо взятие выборок из сигналов (1) и (2) с высокой частотой дискретизации . (фиг. 2d) , а с помощью автоматического переключателя 2 осуществля ется .дискретизации сигнала (2). (фиг. 2-е, г. . с выхода автоматического переключ теля 1 дискретизированный сигнал (фиг. 2S) поступает на вход усилителя-ограничителя 3. На входы усилителя-ограничителя 4 с выходов автоматического переключателя 2 поступают два дискретизированных сигнала (фиг 2,2), сдвинутых по времени на половину периода напряжения частоты дискретизации. В усилителях-ограничи телях 3 и 4 осуществляется усиление и ограничение сигналов по амплитуде. Напряжения (фиг. 2Q ,&) с выходов усилителей-ограничителей 3 и 4 посту пают соответственно на первые входы синхронных детекторов 5 и 6. На вторые входы синхронных детекторов 5 и 6 подается напряжение (фиг. 2Х) высо кой частоты дискретизации с выхода управляемого делителя частоты 16. В результате синхронного детектировани на первый вход логического элемента И 7 измерительного канала поступают импульсы напряжения (фиг. 2d) длител ностью u.t , где погрешность выделения време ного сдвига, обусловленная некратностью частот fo F . Выражая (3), через период частоты дискретизации T(j 1/f о, . получают ,, Н где п. - целая часть отношения ot - дробная часть отношения, обусловленная некратностью частот дискретизации и вход ного сигнала. На первый вход логического элемента И 9 опорного канала поступают импульсы напряжения (фиг. 2а) Длительностью ... Т т - Дг . (5) где Т 21t/S - период входных сигналов;ug погрешность выделения периода. Выражая (5) через Тр, получгиот Т - „/б) где п/2. - целая часть отношения Т/Т ; ctg - дробная часть отнсиаения, обусловленная некратностью частот дискретизации и входного сигнала. За время дtJ на первый счетчик импульсов 10 поступает импульсов: N;-&tVfo-At o-&,fo-N,-Al«. П) где - число импульсов, которое должно поступить на счетчик; N -, погрешность преобразования временного сдвига. За время Т на первый вход счетчика импульсов 10 поступает импуль)СОВ ,. N,.o--Ma- N2, (8) ;где Ng - числоимпульсов, которое должно поступить на счетчик; погрешность преобразовайия периода. С помощью цифрового блока деления 12 осуществляется деление кодов чисел N и N. В результате получают код числа и .N(&tx.-uMH N4 Ч м,-АК1,2,)H&NI/NI) v. w - относительная погреш « Т N. ность преобразования пеЫч Риода; Ли относительная погрешность преобразования фазового сдвига; л - истинное значение преобразованного фазового сдвига. Код числа NI через блок логических элементов И 14 поступает на сдвиговый регист 18, а затем на преобразователь код-частота 19. На выходе преобразователя 19 формируется напряжение частоты. f;-5w,, .10) где S - крутизна преобразования, пропорциональная NVJ, т.е. измеряемому фазовому сдвигу. Выходное напряжение преобразователя код-частота 19 поступает на счетный вход управляемого делителя частоты 16.Коэффициент деления управляемого делителя частоты 16 устанавливается равным коду N (),записанному в сдвиговом регистре 17.В результате деления на выходе управляемого делителя частоты формируется напряжение частоты дискретизации г . JL-ik.l ±-L-A-f..v,F(ii) N, кратное частоте входных сигналов. При последующих циклах преобразования фазовых сдвигов в частоту(10) искретизации сигналов (1) и (2) осуествляется напряжением частоты f, кратной частоте входных сигналов. результате погрешности выделения ременного сдвига и периода обращаютя в нуль, т.е. и . Тогда на цифровой блок деления 12 оступают коды временного сдвига N и периода N N5 без по-, решностей, обусловленных некратнотью частот дискретизации (квантования) и частоты входных сигналов. С выхода цифрового блока деления 12 через блок логических элементов И 14 и сдвиговый регистр 18 на установочные входы преобразователя код-частот 19 поступает код числа Afv(12) В результате на выходе преобразовате ля код-частота 19 устанавливается частота F -cw - cio J-or vp-bHx X(13) пропорциональная преобразуемому фазо вому сдвигу. В предлагаемом устройстве исключе на погрешность выделения временного сдвига и периода входных сигналов, обусловленных некратностью частоты дискретизации и частоты входных сигналов, в результате достигается повы шение точности преобразования фазового сдвига в частоту. Расширение частотного диапазона в область инфра низких частот достигается также за счет формирования частоты дискретиза ции, адаптивной и кратной частоте входных сигналов. Формула изобретения Фазочастотный преобразователь. содержащий два идентичных канала, состоящих из последовательно соедине ных автоматического переключателя, усилителя-ограничителя, синхронного детектора и логического элемента И, а также формирователь коротких импул сов, выходы которого соединены со вторыми входами логических элементов И,.входы управления автоматических переключателей и синхронных детекторов соединены между собой и со входом формирователя коротких импульсов, первый автоматического переключателя первого канала соединен с первой входной клеммой, второй вход - со входом автоматического переключателя второго канала и со второй входной клеммой, о т л и ч а ю-. щ и и с я тем, что, с целью повышения точности и расширения частотного диапазона входных сигналов в область инфранизких частот, введены преобразователь код-частота, управляемый делитель частоты, первый и второй сдвиговые регистры, первый и второй блоки логических элементов И, цифровой блок деления, первый и второй счетчики импульсов и блок управления , первым и вторым выходами соединенный со входами установки нуля первого и второго счетчиков импульсов, счетные входы которых соединены соответственно с вь1ходами логических элементов И каналов, выходы первого счетчика импульсов соединены с первыми входами цифрового блока деления и с первыми входами первого блока логических элементов И, выходы второго счетчика импульсов - со вторыми входами цифрового блока деления, выходы которого соединены с первыми входами второго блока логических элементов И, вторые входы которых соединены между собой и с третьим выходом блока управления, выходы первого и второго блоков логических элементов И соединены соответственно со входами первого и второго сдвиговых регистров, управляющие входы которых соединены с четвертым выходом блока управления, вход которого соединен с второй входной клеммой, выходы второго сдвигового регистра соединены с установочными входами преобразователя код-частота, а выходы первого сдвигового регистра - с установочными входами управляемого делителя частоты, выход которого соединен с входом управления автоматических переключателей, а счетный вход - с выходной клеммой и с выходом преобразователя код-частота. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 471553, кл G 01 R 25/00, 15.06.73. 2.Авторское свидетельство СССР 451965, кл. G 01 R 25/00,26.02.73.

Авторы

Даты

1981-10-15—Публикация

1979-12-19—Подача