. (54) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1981 |

|

SU970689A1 |

| Устройство задержки | 1984 |

|

SU1223355A1 |

| Устройство для защиты от асинхронного режима синхронной машины с бесщеточным возбудителем | 1978 |

|

SU777769A1 |

| Реле времени | 1980 |

|

SU917348A1 |

| УСТРОЙСТВО КОМБИНИРОВАННОЙ ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1994 |

|

RU2091950C1 |

| ДАТЧИК ИМПУЛЬСОВ НАБОРА НОМЕРА | 1972 |

|

SU331501A1 |

| УСТРОЙСТВО КОМПЛЕКСНОЙ ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1996 |

|

RU2117372C1 |

| Стабилизированный источник питания | 1986 |

|

SU1492347A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 1999 |

|

RU2179775C2 |

| УСТРОЙСТВО КОМБИНИРОВАННОЙ ЗАЩИТЫ ТРЕХФАЗНЫХ НАГРУЗОК | 1994 |

|

RU2084064C1 |

I

Изобретение относится к устройствам для автоматики и может быть использовано как для формирования импульсов заданной длительности, так и в качестве реле времени для Sa-. мыкания или размыкания контактов цепи на определенное время.

Известные .элементы задержки (реле времени), выполненные на нейтральных электромагнитных реле в каг честве -исполнительного элемента, в которых обмотка реле после его сра батывания находится под током, не только неэкономичны, но и быстро вырабатывают свой ресурс, а следовательно, обладают низким показателем надежности.

Известны реле времени, основанные на компарировании заряда конденсатора триггером Шмидта, они имеют контактную цепь запуска в цепи эмитг тера и блокировку устройства за счет включения запуска на время, большее времени задержкир.

Функциональные возможности такого устройства ограничены, жроме того, оно обладает низким коэффициентом использования напряжения питания изза резистора в цепи эмиттеров триггера Шмидта.

Известно устройство задержки, которое содержит соединенные последовательно времязадающую RC-цепочку, триггер Шмидта, компарирующий уровень за

to ряда времязадающего конденсатора, и выходной транзистор, в коллекторную цепь которого включена обмотка исполнительного элемента. Питающее напряжение на устройство и режимы

15 его работы задаются с помощью механического переключателя, нагрузка подключается к питанию через контакты исполнительного элемента в течение времени интервала или по его исте20чении f 2.

Известное реле времени обладает недостаточной надежностью и экономичностью, так как обМотка реле посе срабатывания находится под тоой, пока переключатель.режимов не будет переведен в исходное положение. При этом реле быстро вырабатывает свой ресурс. Кроме того надежность реле времени снижается из-за использования механического переклнгчения при управлении режимами ра- боть1 схемы. Использ1;ование триггера мидта в качестве компаратора не озволяет в достаточной мере использовать величину, напряжения питания, . т.е. заряжать времязадающий конденсатор допуровней близких к велич 1не напряжения питания. Иначе говоря, ограничен предел максимального времени задержки из-за наличия ограничений на величину резистора в цепи эмиттеров триг1 ера Шмидта,

Целью изобретения является повыг шение надежности и экономичности.

Поставленная цель достигается Тем, что в устройство, содержащее последовательно соединенные времязадающую цепЬу компаратор, выполненный, например, на транзисторе с резистором и переключающим диодом в . эмй герн6й цепи, и выходной транзистор, с нагрузкой в коллекторной цепи, введены инвертор, включенный между компаратором и выходным транзистором, синхронные разрядный ключ и управляемый источник напряжения, запускающий ключ и развязывающее устройство, причем разряднйй ключ подсое- , динен параллельно конденсатору времязадающей цепи, входы разрядного ключа и управляемого источника напря жения подключены к общей точке соединения выхядов развязывающего устройства и запускающего ключа, выход правляемого источника напряжения подключен к времязадающей цепи и инвертору, вход развязывающего устройства подключен к общей точке выходного транзистора и нагрузки, а вход запускающего ключа подсоединен к шине Запуск.

Компаратор, вьтолненный на транзисторе, с резистором и переключаюощм-диодом в эмиттерной цепи, позвуоляет более полно использовать величину напряжения источника питания для формирования больших выдерже1с времени.

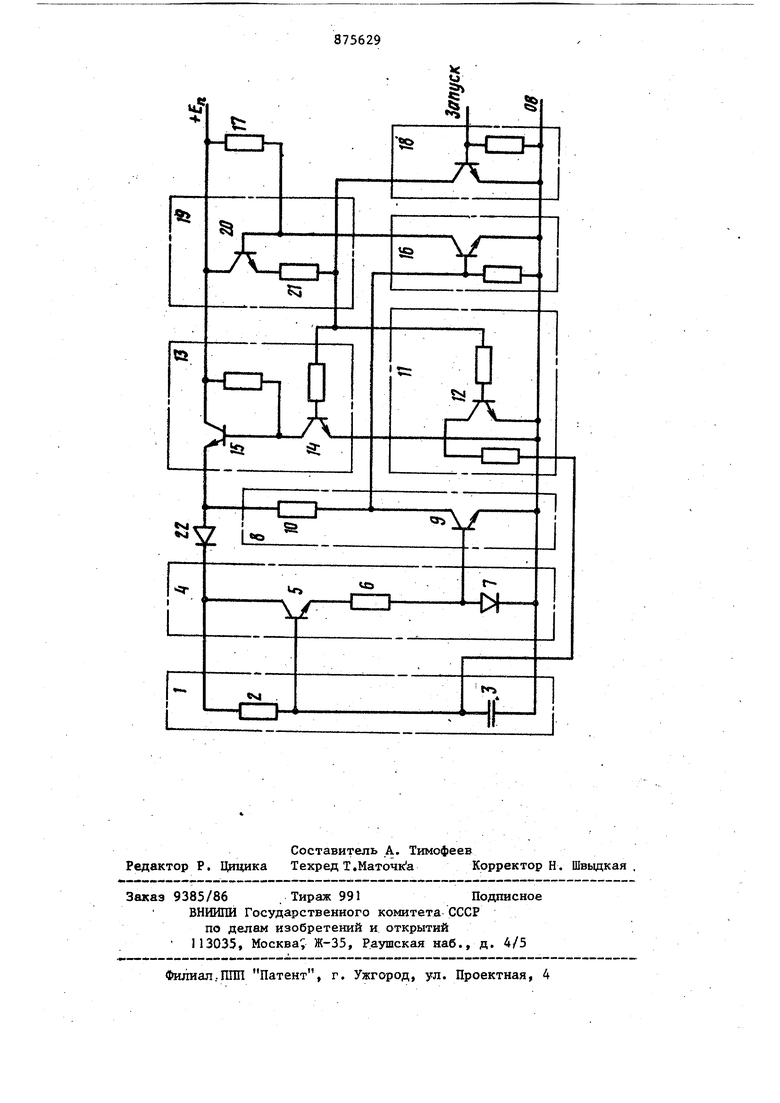

На чертеже представлена принципната ная электрическая схема Ьредла/гаемого устройства задержки.

Устройство задержки содержит времязадающую цепь 1, состоящую из резистора 2 и конденсатора 3, компаратор 4, состоящий из транзистора 5

с резистором 6 и переключающим диодом 7 в эмиттерной цепи, инвертор 8, состоящий из транзистора 9 и резистор ра 10 в коллекторной цепи, разрядный ключ 11. на транзисторе 12, управп

ляемый источник 13 на транзисторах

14и 15, ключ 16 с нагрузкой 17 в коллекторной цепи, запускающий ключ ;18 и развязывающий элемент 19 на транзисторе 20 и резисторе 21 .Диод 22 введён

s в схему для повышения устойчивости работы. Диод 22 может отсутствовать, если компаратор 4 питать непосредственно от источника питания(+ . Однако при этом несколько возрастает ток,

0 потребляемый в исходном состоянии. Нагрузка 17 может быть как активной, так и являться обмоткой исполнительного реле.

Устройство работает следующим

5 образом.

В исходном состоянии при отсутствии управляющего сигнала по шине Запуск ключи 16 и 18 закрыты, а транзисторы 12 и 14 насыщетл, т.е. времязадающий конденсатор 3 блокирован, а напряжение на эмиттере транзистора 15 близко к нулевому значению, что поддерживает ключ 16 через резистор 10 в закрытом состоянии.

При подаче отпирающего импульса по шине Запуск ключ, 18 открывается, транзисторы 12 и 14 закрываются, потенциал на эмиттере транзистора

15становится высоким, что приводит к отпиранию ключа 16 резистор 10 и блокировке схемы низким уровнем на коллекторе открытого ключа

16, подаваемым через развязывающий элемент 19 на входы разрядного ключа 11 и управляемого источника напряжения 13.

Закрывание разрядного ключа 11 и подача высокого потенциала на врёмязадающую цепь 1, компаратор 4 и инвертор 8 с выхода управляемого источника 13 Приводят к тому, что конденсатор 3 времязадающей цепи начинает заряжаться через резистор 2, и когда напряжение на конденсаторе 3 становится таким, что ток через,

5 резистор 6 компаратора 4 превысит значение пикового тока переключающего диода 7, транзистор 9 инвертора 8 открывается и шунтирует базо-эмит терный переход ключа 16, что приводит к закрыванию последнего, и схема возвращается в исходное состояние. Таким образом, в предлагаемом устройстве обмотка исполнительного элемента находится под током только во время формирования временного интервала, что повьппает надежность устройства в целом, причем в качестёёй полнительного элемента исйольззпотся нейтральные электромагнитные реле так как схема обеспечивает автомати блокировку запуска и установку в исходное состояние. Рабочий бень зарядного конденсатора 3может практически приближаться к величине + Ер J что дает возможность совместно с режимом транзистора компаратора обеспечивать формирование достаточно больших интервалов задержки. Шяна Запуск легко сопрягается со стандартными уров11ями логических систем управления. Развязка нагрузки 17 от выхода запускающего ключа 18 через развязывающее устройство 19 обеспечивает возможность запуска как импульсным сигналом, так и единичным уровнем. Значения токов потребле ния устройством в исходном состоянии даже при з;начительных величинах Е весьма малы, т.е. устройство достаточно экономично. Все узлы элемента задержки могут быть изготовлены в одном корпусе как в модульном, так и интегральном исполнении. 9 Формула изобретения Устройство задержки, содержащее соединенные последовательно времязадапицую цепь, компаратор, выполненный например, на транзисторе с резистором и переключаюощм диодом в эмиттернбй цепи, и выходной транзистор с нагрузкой в коллекторной цепи, отличающееся тем, что, с целью повышения надежности, в него введены инвертор, включенный между компаратором и выходным транзистором, синхронные разрядный ключ и управляем мый источник напряжения, запускающий ключ и развязывающее устройство, причем разрядный ключ подсоединен параллельно конденсатору времязадающей цепи, а вход разрядного ключа совместно со входом управляемого источника напряжения подключены к-общей точке соединения выходов развязывающего устройства и запускающего ключа,выход управляемого источника напряжения подключен к времязадающей цепи и инвертору, вход развязывающего устройства подключен к общей точке выходного транзистора и нагрузки, а вход запускающего ключа подсоединен к щине Запуск. Источни си информации, принятые во вш1мание при экспертизе 1.Патент США № 40i5142, кл. 307-247, опублик. 1977, 2.Заявка Японии № 54-12316, кл. 6(1) 42(1003) (прототип). .

Авторы

Даты

1981-10-23—Публикация

1980-02-20—Подача