(54) ЭЛЕКТРОННЫЙ КЛЮЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1980 |

|

SU907799A1 |

| Регулятор напряжения генераторного источника питания | 1988 |

|

SU1663741A1 |

| РЕГУЛЯТОР НАПРЯЖЕНИЯ ГЕНЕРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ | 1999 |

|

RU2149497C1 |

| РЕГУЛЯТОР НАПРЯЖЕНИЯ ГЕНЕРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ | 1996 |

|

RU2104611C1 |

| РЕГУЛЯТОР НАПРЯЖЕНИЯ ГЕНЕРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ | 1997 |

|

RU2120178C1 |

| Прерыватель | 1973 |

|

SU454692A2 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Двухтактный транзисторный преобразователь постоянного напряжения | 1982 |

|

SU1032569A1 |

| Устройство для управления мощным высоковольтным транзисторным ключом | 1991 |

|

SU1778886A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

I .

Изобретение относится к автоматике и вычислительной технике и может 6bitb использовано в аналоговых и гибридных вычислительных устройствах различного назначения.

Известны электронные ключи, содержащие транзисторы противоположного типа проводимости и блок управления (1J.

Недостаток устройства - невысокая надежность.

Наиболее близким техническим решением к предлагаемому является электронный ключ, содержащий два транзисторных прерывателя тока, первый из которых подключен к потенциальному выводу, а второй - к общему выводу источника коммутируемого напряжения- и резисторы, подключенные к блоку управления 2J., Недостатки этого устройства - низкое быстродействие, обусловленное непостоянством времени включения и отключения, .и невысокая на;а1ежность.

Цель изобретения - повышение быстродействия и надежнвстн.

С этой целью в электронный ключ, соДер жащий два компенсированных прерывателя тока, состоящих из транзисторов протнво положного типа проводимости, коллекторы транзисторов компенсированных прерывателей тока соединены соответственно с общим и потенциальным выводами источника

, коммутируемого напряжения, а эмкттёр Л - с выходной шиной, и резисторы, первые

выводы которых подключены к выходам блока управления, введены делители напряжения, каждый из которых состоит из соедииенных последовательно нелинейного элемента и резистора, причем выэоды неJ0 линейных элементов делителей напряжения подключены к базам соответствующих транзисторов первого компенсированного прерывателя тока, а выводы резисторов делителей напряжения соединены с базами соответствующих транзисторов второго компен15 сироваиного прерывателя тока, при этом вторые выводы резисторов соединены со средними точками соответствующих делителей напряжения.

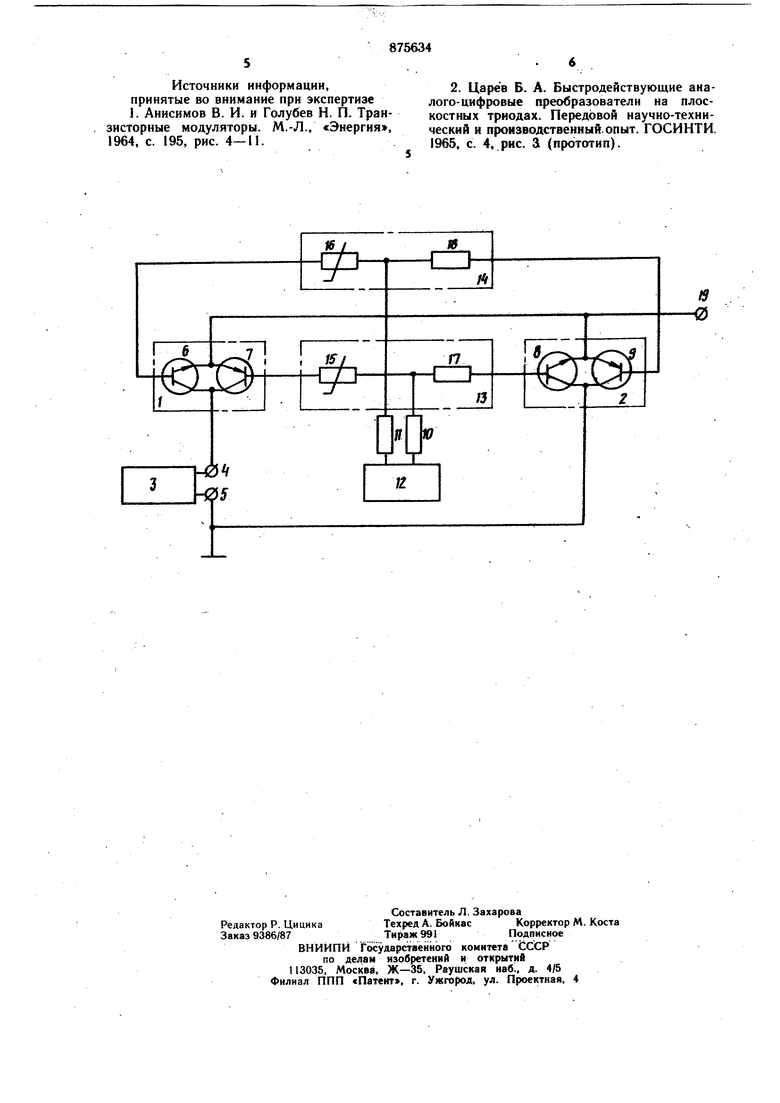

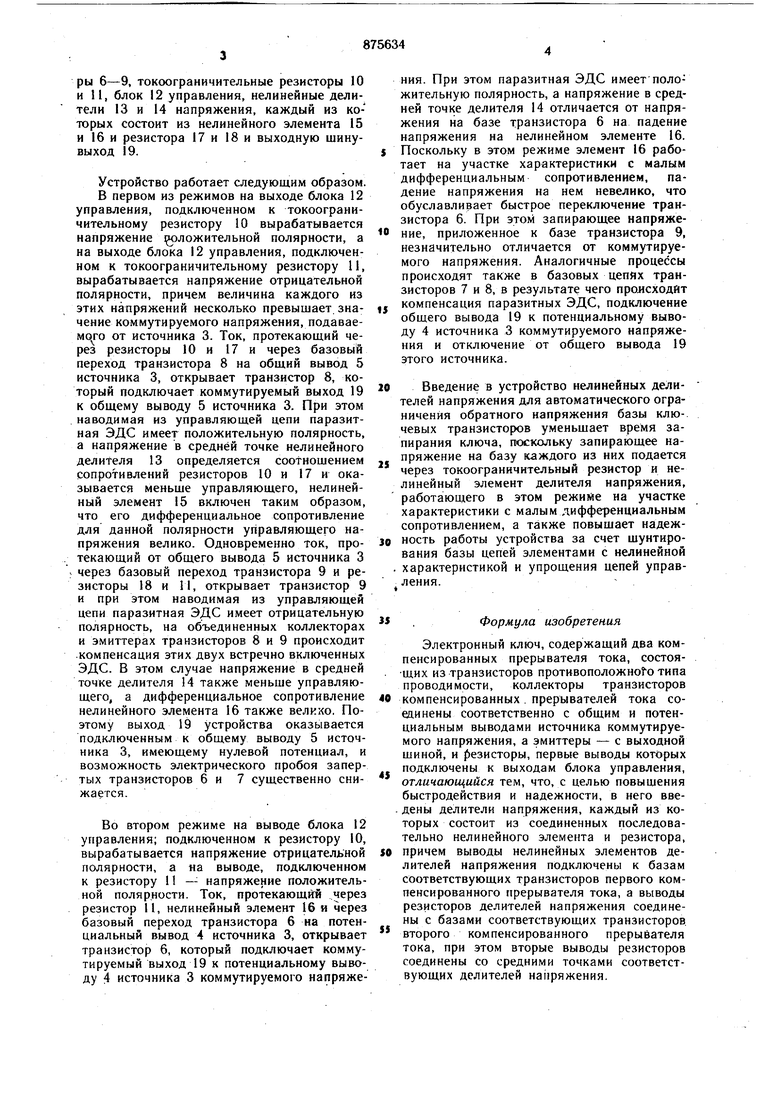

На чертеже представлена принцнпиаль. ная электрическая схема устройства.

Я| Устройство содрржит компенсированные прерыватели тока I и 2, источник 3 коммутируемого напряжения с потенциальным выводом 4 и общим выводом 5, транзисторы 6-9, токоограничительные резисторы 10 и И, блок 12 управления, нелинейные делители 13 и 14 напряжения, каждый из которых состоит из нелинейного элемента 15 и 16 и резистора 17 и 18 и выходную шинувыход 19.

Устройство работает следующим образом.

В первом из режимов на выходе блока 12 управления, подключенном к токоограничительному резистору 10 вырабатывается напряжение ложительной полярности, а на выходе блока 12 управления, подключенном к токоограничительному резистору 11, вырабатывается напряжение отрицательной полярности, причем величина каждого из этих напряжений несколько превышает значение коммутируемого напряжения, подаваемого от источника 3. Ток, протекающий через резисторы 10 и 17 и через базовый переход транзистора 8 на общий вывод 5 источника 3, открывает транзистор 8, который подключает коммутируемый выход 19 к общему выводу 5 источника 3. При этом наводимая из управляющей цепи паразитная ЭДС имеет положительную полярность, а напряжение в средней точке нелинейного делителя 13 определяется соотношением сопротивлений резисторов 10 и 17 и оказывается меньше управляющего, нелинейный элемент 15 включен таким образом, что его дифференциальное сопротивление для данной полярности управляющего напряжения велико. Одновременно ток, протекающий от общего вывода 5 источника 3 через базовый переход транзистора 9 и резисторы 18 и М, открывает транзистор 9 и при этом наводимая из управляющей цепи паразитная ЭДС имеет отрицательную полярность, на объединенных коллекторах и эмиттерах транзисторов 8 и 9 происходит компенсация этих двух встречно включенных ЭДС. В этом случае напряжение в средней точке делителя 14 также меньше управляющего, а дифференциальное сопротивление нелинейного элемента 16 также велико. Поэтому выход 19 устройства оказывается подключенным к общему выводу 5 источника 3, имеющему нулевой потенциал, и возможность электрического пробоя запертых транзисторов 6 и 7 существенно снижается.

Во втором режиме на выводе блока 12 управления; подключенном к резистору 10, вырабатывается напряжение отрицательной полярности, а на выводе, подключенном к резистору 11 -- напряжение положительной полярности. Ток, протекающий через резистор II, нелинейный элемент 16 и через базовый переход транзистора 6 на потенциальный вывод 4 источника 3, открывает транзистор 6, который подключает коммутируемый выход 19 к потенциальному выводу 4 источника 3 коммутируемого напряжения. При этом паразитная ЭДС имеет положительную полярность, а напряжение в средней точке делителя 14 отличается от напряжения на базе транзистора 6 на падение напряжения на нелинейном элементе 16. Поскольку в этом режиме элемент 16 работает на участке характеристики с малым дифференциальным сопротивлением, падение напряжения на нем невелико, что обуславливает быстрое переключение транзистора 6. При этом запирающее напряжение, приложенное к базе транзистора 9, незначительно отличается от коммутируемого напряжения. Аналогичные процессы происходят также в базовых цепях транзисторов 7 и 8, в результате чего происходит компенсация паразитных ЭДС, подключение общего вывода 19 к потенциальному выводу 4 источника 3 коммутируемого напряжения и отключение от общего вывода 19 этого источника.

Введение в устройство нелинейных делителей напряжения для автоматического ограничения обратного напряжения базы ключевых транзисторов уменьшает время запирания ключа, поскольку запирающее напряжение на базу каждого из них подается

через токоограничнтельный резистор и нелинейный элемент делителя напряжения, работающего в этом режиме на участке характеристики с малым дифференциальным сопротивлением, а также повышает надежность работы устройства за счет шунтирования базы цепей элементами с нелинейной . характеристикой и упрощения цепей управления.

Формула изобретения

Электронный ключ, содержащий два компенсированных прерывателя тока, состоящих из транзисторов противоположного типа проводимости, коллекторы транзисторов

компенсированных. прерывателей тока соединены соответственно с общим и потенциальным выводами источника коммутируемого напряжения, а эмиттеры - с выходной шиной, и (Резисторы, первые выводы которых подключены к выходам блока управления, отличающийся тем, что, с целью повышения быстродействия и надежности, в него вве. дены делители напряжения, каждый из которых состоит из соединенных последовательно нелинейного элемента и резистора,

0 причем выводы нелинейных элементов делителей напряжения подключены к базам соответствующих транзисторов первого компенсированного прерывателя тока, а выводы резисторов делителей напряжения соединены с базами соответствующих транзисторов, второго компенсированного прерывателя тока, при этом вторые выводы резисторов соединены со средними точками соответствующих делителей на11ряжения.

Источники информации, принятые во внимание при экспертизе 1. Анисимов В. И. и Голубев Н. П. Транзисторные модуляторы. М.-Л., «Энергия, 1964, с. 195, рис. 4-11.

Авторы

Даты

1981-10-23—Публикация

1980-02-14—Подача