(54) РЕГУЛЯТОР МОЩНОСТИ ПЕРЕМЕННОГО ТОКА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор электрической мощности переменного тока | 1982 |

|

SU1056170A1 |

| Регулятор электрической мощности переменного тока(его варианты) | 1981 |

|

SU983690A1 |

| Регулятор электрической мощности | 1980 |

|

SU943685A1 |

| Цифровой тиристорный регулятор | 1981 |

|

SU954992A1 |

| Способ управления трехфазным тиристорным регулятором | 1984 |

|

SU1226594A1 |

| Устройство для формирования управляющего сигнала | 1980 |

|

SU903843A2 |

| Устройство регулирования электрической мощности переменного тока | 1991 |

|

SU1830523A1 |

| Устройство для регулирования температуры в камере высокого давления | 1981 |

|

SU1008712A1 |

| Устройство для компенсации реактивной мощности нагрузки и симметрирования трехфазной сети | 1985 |

|

SU1261044A1 |

| Способ стабилизации активной мощности тиристорного регулятора и устройство для его осуществления | 1982 |

|

SU1073874A1 |

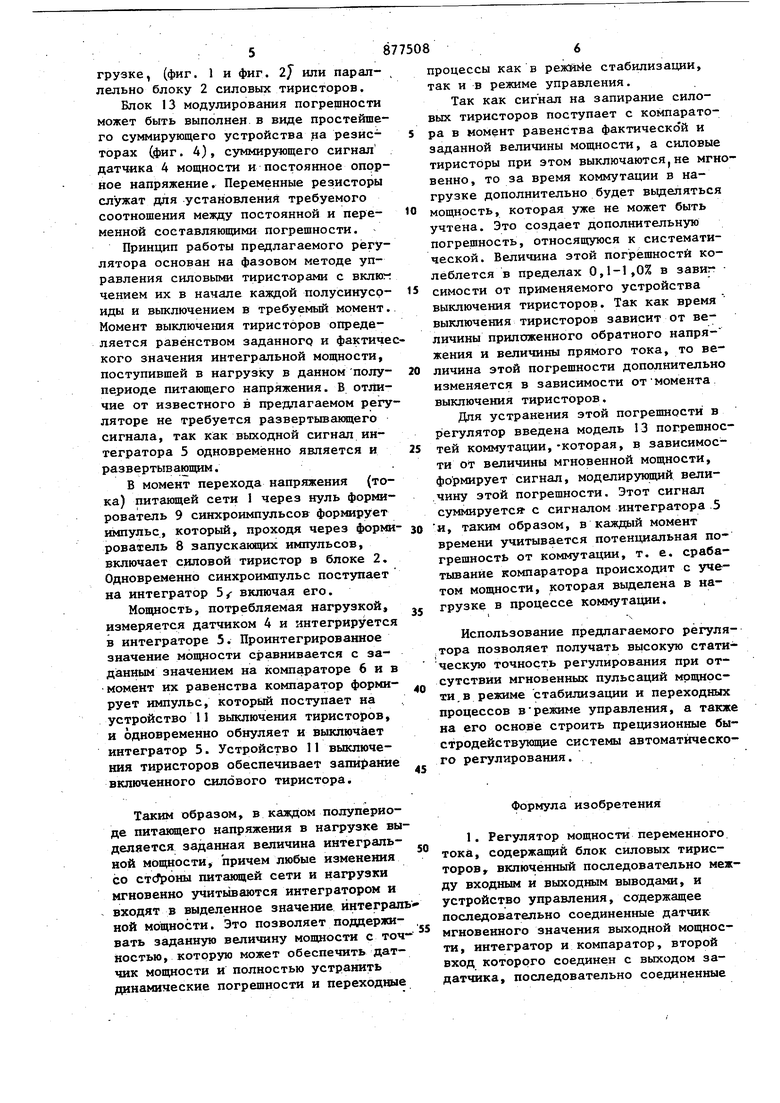

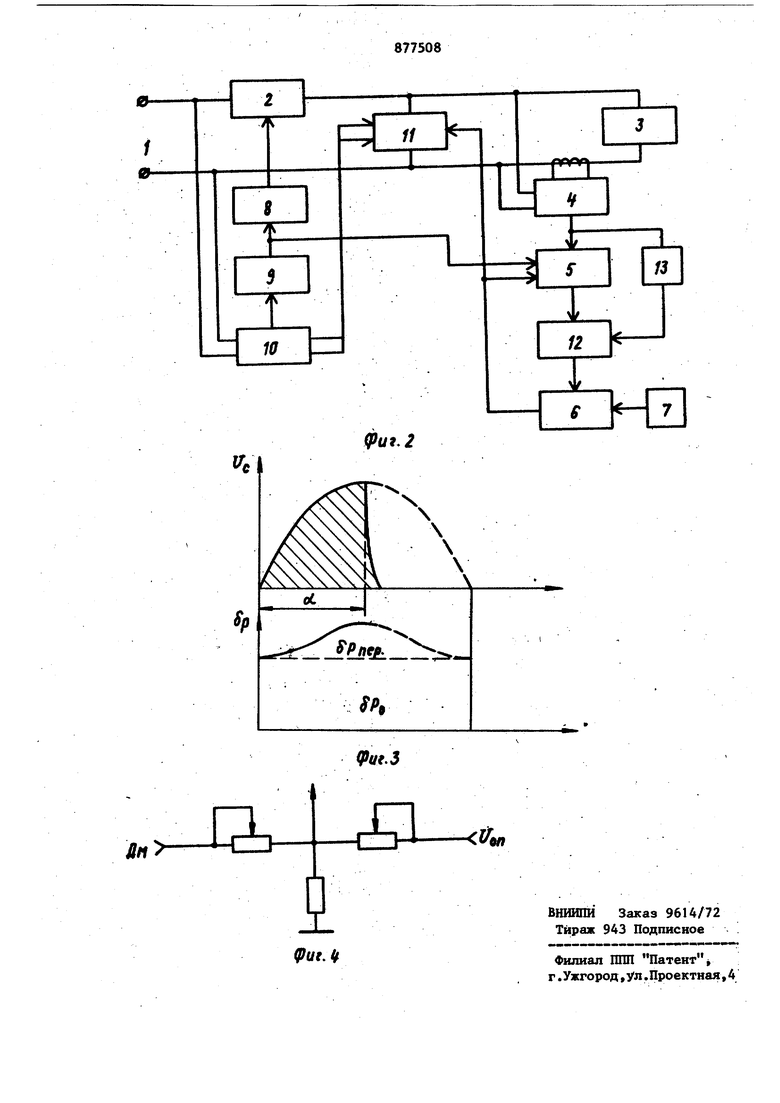

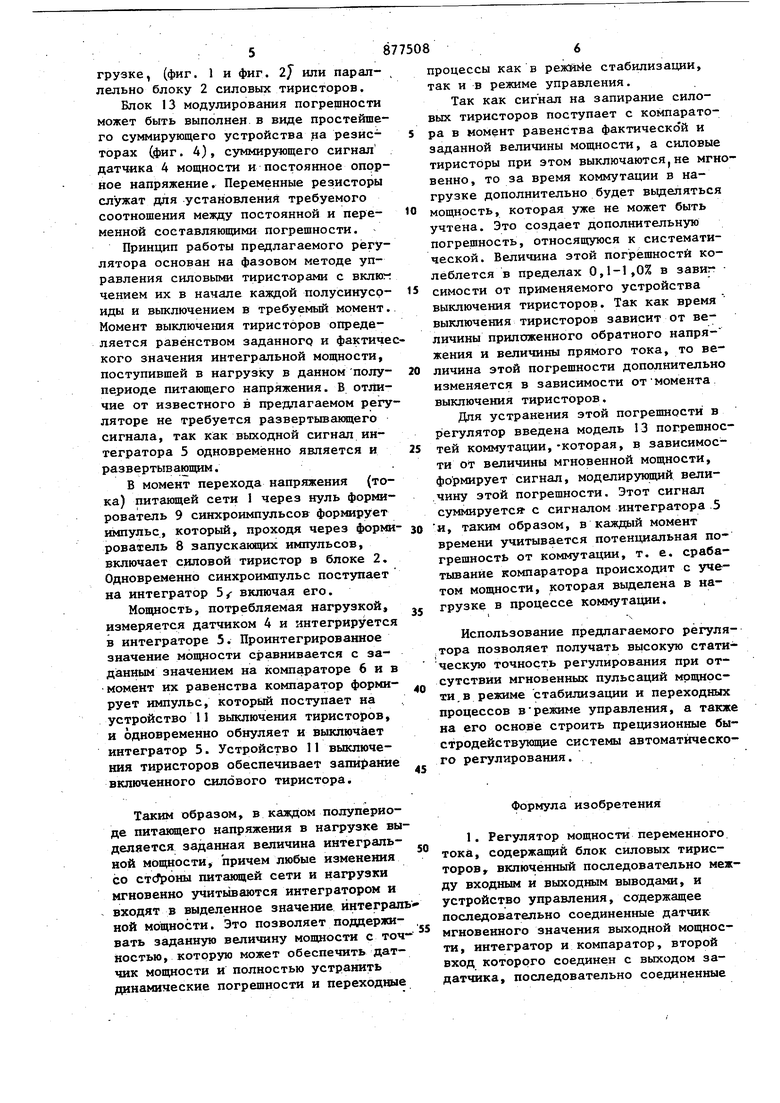

Изобретение относится к регулирова нию электрических величин, в частности мощности. Известны регуляторы электрической мощности в нагрузке, подключенной к сети переменного тока, содержащие силовую цепь из последовательно соединенных тиристорных ключей и нагрузки, и управляющую цепь, содержащую датчик регулируемой величины, усредняю щий фильтр, компаратор и формиррватели запускающих импульсов, принцип дей ствия которых основан на усреднении сигналов датчика регулируемой величины с последукщим сравнением полуденно го сигнала обратной связи с задайным значением и формированием (по результатам сравнения сигнала на запуск силовых тиристоров О . Недостатком таких регуляторов являются значительная инерционность, обусловленная наличием усредняющего фильтра и, как следствие, невысокая статическая и динамическая точность. Наиболее близким к предлагаемому по технической сущности является регулятор мощности, содержащий блок силовых тиристоров, включенный последовательно между входным и выходным выводами, и устройство управления, содержащее последовательно соединенные датчик мгновенного значения выходной мощности, интегратор и компаратор, второй вход которого соединен с выходом задатчика, последовательно соединенные формирователь синхронизирукнцих импульсов и формирователь запускающих импульсов, при этом выход формирователя запускающих импульсов соединен с управляницим входом блока силовых тиристоров, а вход формирователя синхронизирукмцих импульсов соединен с одним из выходов синхронизирующего трансформатора, вход которого соединен с входными выводами. Принцип работы регулятора основан на фазовом управлении силовыми тиристорами с естественным выключением, послед8них. Момент включения силовых тиристоров определяется соотношениеК меязду заданным и средним значениями мощности и развертывающим сигналом 23. Однако в таком регуляторе точность поддержания заданного значения зависит от точностных показателей усредняющего фильтра (интегрирующей цепи), причем точность увеличивается с увеличегшем постоянной времени фильтра. При этом ухудшаются динамические показатели регулятора, так как сигнал обратной связи не в состоянии передавать быстрые изменения мощности. Таким образом, увеличение статической точности в данном регуляторе связано с ухудшением динамической точности. Кроме того, при изменении задания рег лирования в регуляторе наблюдаются пе реходные процессы, длительность которых .также определяется постоянной фил тра, и которые не позволяют использовать его в качестве исполнительного устрой ства в быстродействующих системах автоматического регулирования. Цель изобретения - улучшение динамических характеристик. Поставленная цель Достигается тем, что в устройство введен блок выключения силовых тиристоров, синхронизирукщие входы которого подключены к другим выходам синхрочизирукнцего трансформатора, а управлякящй вход соедине с выходом компаратора, при этом выход компаратора соединен с первым входом синхронизации интегратора, второй вхо синхронизации которого соединен с выходом формирователя синхронизирующих импульсов. Кроме того, для дополнительного по вышения точности регулирования в регу лятор введен двухвходовый , включенный между выходом интегратора и входом компаратора, и блок моделирования погрешности, выход которого подключен ко второму входу сумматора, а вход - к выходу датчика мгновенного значения вьпсодной мощности. На фиг. 1 представлена функциональ ная схема регулятора мощности; на фиг. 2 - функциональная схема регулятора мощности, обеспечивающая дополнительное увеличение точности; на фиг 3 - диаграммы питающего напряжения- и погрешности коммутации; на фиг. 4 - пришщпиальная схема модели погрешностей коммутации. Функциональная схема регулятора мощности (фиг. 1} содержит питающую. 4 сеть 1 и подключенную к ней силовую цепь, состоящую из последовательно соединенных блока 2 силовых тиристоров и нагрузки 3, последовательно соединенные датчик 4 мгновенного значе- . ния выходной мощности, токовая изме; ительная цепь которого посредством измерительного трансформатора подключена к силовой цепи, а измерительная цепь напряжения подключена параллельно нагрузке, интегратор 5, компаратор 6 и задатчик 7, выход которого соединен со вторым входом компаратора, формирователь 8 запускающих импульсов, выход которого подключен к управляющему входу блока 2 силовых тиристоров, формирователь 9 синхроимпульсов, выход которого соединен со входом формирователя запускающих импульсов и одним из входов синхронизации интегратора 5, синхронизирующий трансформатор Ю, вход которого подключен к питающей сети 1, а выходы - один ко входу формирователя 9 синхроимпульсов, другие - к синхронизирующим входам устройства 11 выключения силовых тиристоров, управляющий вход которого соединен со вторым входом синхронизации интегратора 5 и выходом компаратора 6. Схема регулятора (фиг. 2) дополнительно содержит двухвходовый сумматор 12, включенньй между выходом интегратора 5 и первым входом компаратора 6, блок 13 модулирования погрешности, вход которого подключен к выходу датчика 4, а выход - ко второму входу сумматора 12. В качестве датчика мгновенной мощности используется измерительный преобразователь мощности на датчиках Холла. Интегратор 5 вьшолнен на основе операционного усилителя, интегрирующая емкость которого может закорачиваться ключом, управляемьм триггером. Компаратор 6 выполнен на базе операционного усилителя. Формирователь 8 запускающих икшульсов и формирователь 9,синхроимпульсов выполнены на основе транзисторных импульсных усилителей. Устройство 11 принудительного выключения силовых тиристоров может быть выполнено на основе тиристорных ключей и коммутирующих емкостей, включенных определенным образом, и может быть включено в схеме параллельно нагрузке, (фиг. 1 и фиг. 2j или параллельно блоку 2 силовых тиристоров. Блок 13 модулироваиия погрешности может быть выполнен в виде простейшего суммирующего устройства на резисторах (фиг. 4), суммирующего сигнал датчика 4 мощности и постоянное опорное напряжение. Переменные резисторы служат для установления требуемого соотношения между постоянной и переменной составляющими погрешности. Принцип работы предлагаемого регулятора основан на фазовом методе управления силовыми тирист-орами с вклюг чением их в начале каждой полусинусриды и выключением в требуемый момент. Момент выключения тиристоров определяется равенством заданного и фактиче кого значения интегральной мощности, поступившей в нагрузку в данномполупериоде питающего напряжения. В отЛичие от известного в предлагаемом регу ляторе не требуется развертывакяцего сигнала, так как выходной сигнал интегратора 5 одновременно является и развертывающим. В момент перехода напряжения (тока) питающей сети 1 через нуль формирователь 9 синхроимпульсов формирует импульс, который, проходя через форми рователь 8 запускающих импульсов, включает силовой тиристор в блоке 2, Одновременно синхроимпульс поступает на интегратор 5 включая его. Мощность, потребляемая нагрузкой, измеряется датчиком 4 и интегрируется 13 интеграторе 5. Проинтегрированное значение мощности сравнивается с заданным значением на компараторе бив момент их равенства компаратор формирует импульс, который поступает на устройство I1 выключения тиристоров, и одновременно обнуляет и выключает интегратор 5. Устройство 11 выключения тиристоров обеспечивает запирание включенного силового тиристора.

Таким образом, в каждом полупериоде питающего напряжения в нагрузке выделяется заданная величина интегральной мощности, причем любые изменения со стсТ)ошй питающей сети и нагрузки мгновенно учитываются интегратором и входят в выделенное значение йнтеграль ной мощности. Это позволяет поддерживать заданную величину мощности с точ ностью, которую может обеспечить датчик мощности и полностью устранить динамические погрешности и переходные

Формула изобретения

с

(Put. 2

fp

N

fP.

iit.3

Авторы

Даты

1981-10-30—Публикация

1980-02-22—Подача