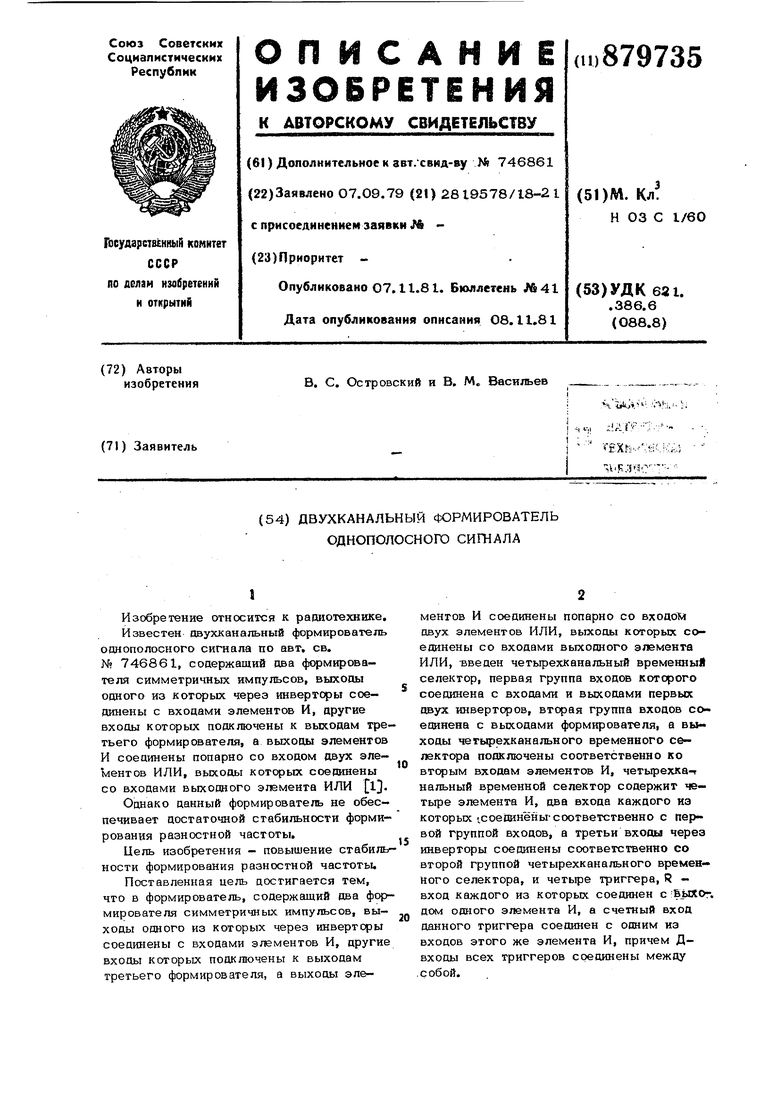

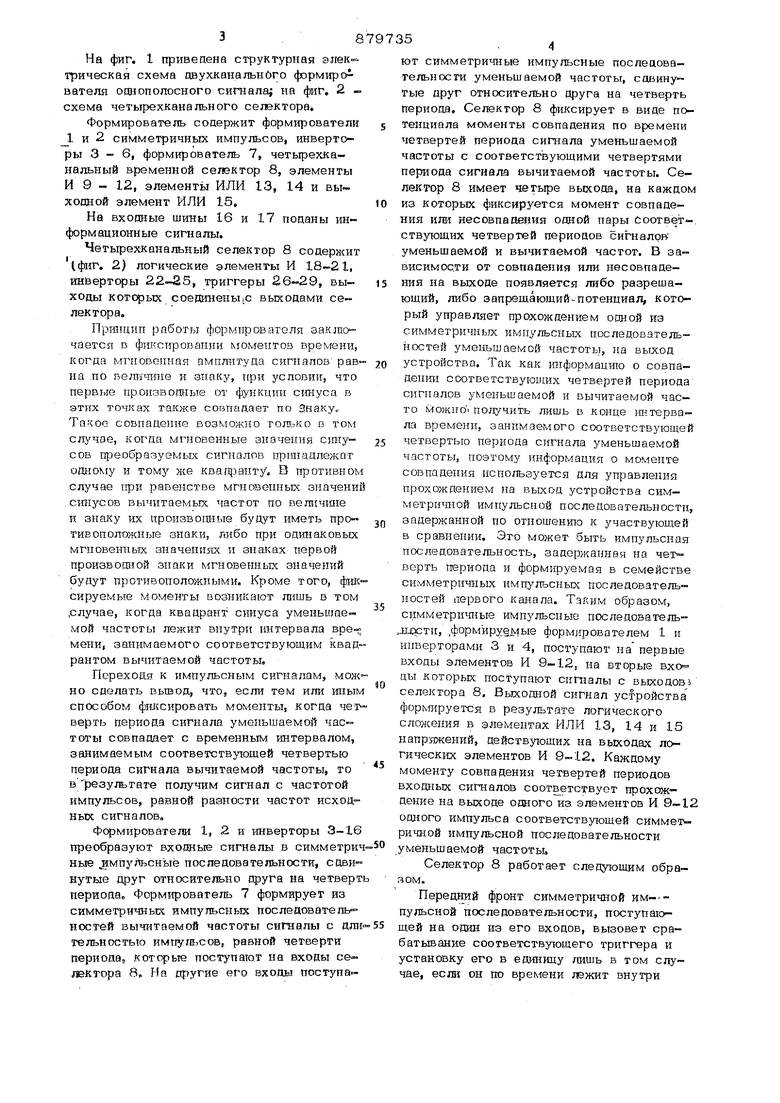

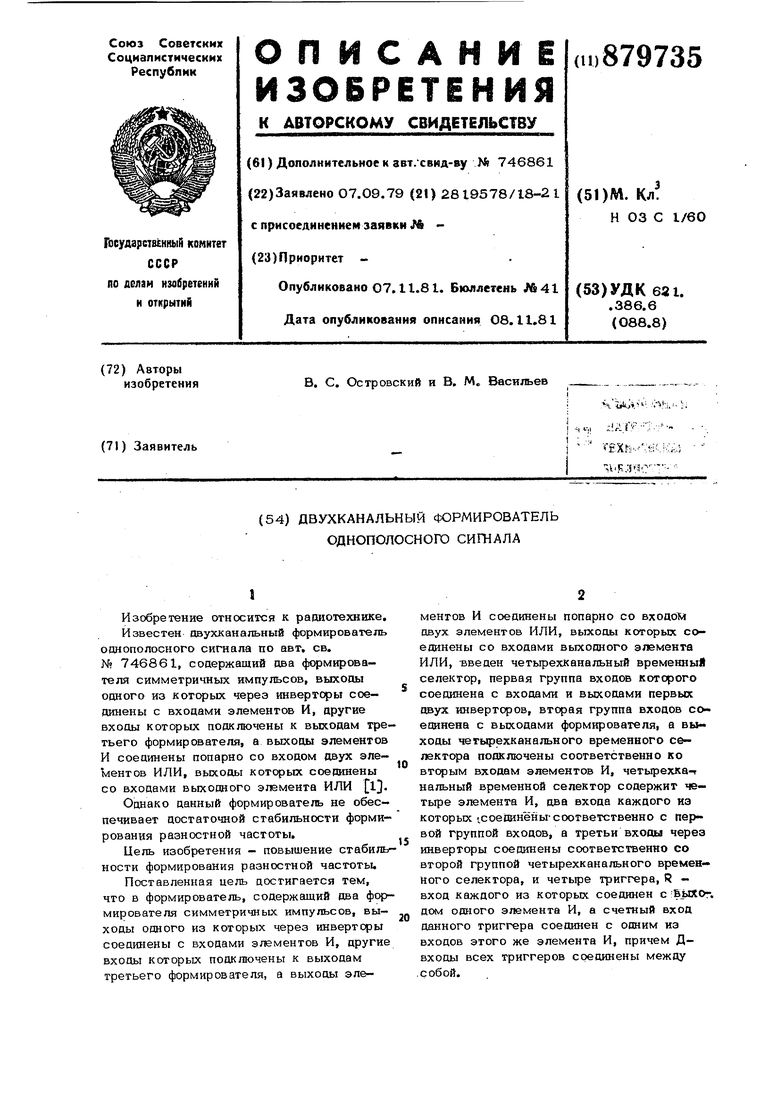

Изобретение относится к радиотехнике. Известен овухканальный формирователь оонополосного сигнала по авт. св. N 746861, содержащий два формирователя симметричных импульсов, выходы одного из которых через инверторы соединены с входами элементов И, другие входы которых подключены к выходам третьего формирователя, а выходы элементов И соединены попарно со входом двух элементов ИЛИ, выходы которых соединены со входами выходного элемента ИЛИ l}. Однако данный формирователь не обеспечивает достаточной стабильности формирования разностной частоты. Цель изобретения - повышение стабильности формирования разностной частоты. Поставленная цель достигается тем, что в формирователь, содержащий два формирователя симметричных импульсов, выходы одного из которых через инверторы соединены с входами элементов И, другие входы которых подключены к выходам третьего формирователя, а выходы эле- ментов И соединены попарно со Bxoaolvi двух элементов ИЛИ, выходы которых соединены со входами выходного элемента ИЛИ, -введен четырехканальный временный селектор, первая группа входов которого соединена с входами и выходами первых двух инверторов, вторая группа входов соединена с выходами формирователя, а выходы чегырехканального временного селектора подключены соответственно ко вторым входам элементов И, четырехка-т нальный временной селектор содержит че- тьфе элемента И, два входа каждого из которых 1Cое1винёньгсоответственно с первой группой входов, а третьи входы через инверторы соединены соответственно со второй группой четырехканального временного селектора, и четыре триггера, R вход каждого из которых соединен с BJjXOr. дом одного элемента И, а счетный вход данного триггера соединен с одним из входов этого же элемента И, причем Двходы всех триггеров соединены между собой. На фиг. 1 привецена структурная электрическая схема сшухканальнбго формирсА вагеля оплополосного сигнала; на фиг, 2 - схема четырехканального сегкктора. Формирователь соаержит формирователи 1 и 2 симметричных импульсов, инверторы 3-6, формирователь 7, четырехканальный временной селектор 8, элементы И 9 - 12, элементы ИЛИ 13, 14 и выхооной элемент ИЛИ 15. На вхоиные шины 16 и 17 поданы информационные сигналы. Четырехканальный селектор 8 содержит Чфиг. 2) логические элементы И 18-21, инверторы 22-25, триггеры 26-29, выходь которых соединены С выходами селектора. Прштцип работы формирователя закгаочается в фиксировании моментов времени, когда мгновенная амплитуда сигналов равна .по величине и зп.аку, при условии, что первые произвошгые от функции cmiyca в этих точках также совпадает по Знаку.Токое совпадение возможно только в том случае, когда мгновенные значения синусов щэеобразуомых сигналов принадлежат одному и тому же квагфанту. В противном случае при равенстве мгновенньк значений синусов вычитаемых частот по велччшю и знаку их «роизво шые будут иметь противоположные знаки, гшбо при одинаковых мгновенных значениях и знаках первой производной знаки мгновенных значений будут противоположными. Кроме того, фии; сиру ем ые моменты возникают тшшь в том .случае, когда квадрант синуса уменьшаемой частоты лежит внутри интервала вре« мени, занимаемого соответствующим квадрантом вычитаемой частоты. Переходя к импульсным сигналам, мож но сделать вьтод, что, если тем или иным способом фшссировать моменты, когда чет верть периода сигнала уменьшаемой частоты совпадает с временным интервалом, занимаемым соответствующей четвертью периода сигнала вычитаемой частоты, то в результате получим сигнал с частотой импульсов, равной разности частот исходных сигналов. Ффмирователи 1, 2 и инверторы 3-16 преобразуют входные сигналы в симметри

ные ,импуЛьсныё последовательности, сдвинутые друг относительно друга на четверть периода,, Форм5фователь 7 формирует из симметричньсх импульсных последователь иостей вычитаемой частоты сипналы с длительностью импугазсов, равной четверти периода которые поступают на входы се™ jKKTOpa 8, На другие его входы поступаСелектор 8 работает следующим образом.

Передний фронт симметричной им-пульсной последовательности, поступающей на один из его входов, вызовет срабатывание соответствующего триггера и установку его в единицу /шшь в том случае, если он по времени хвжит внутри ЮТ симметричные импульсные последовательности уменьшаемой частоты, сдвину™ тые друг относительно друга на четверть периода. Селектор 8 фиксирует в виде потенциала моменты совпадения по времени четвертей периода сигнала уменьшаемой частоты с соответствующими четвертями периода сигнаяз вычитаемой частоты. Селектор 8 имеет четыре выхода, на каждом из которых фиксируется момент совпадения или несовпаиення одной пары соответ-. ствующих четвертей периодов сигналов уменьшаемой и вычитаемой частот. В зависимости от совпадения или несовпадения на выходе появляется либо разрешающий, либо запрешающий-потенциал, который управляет прохождением оиной из симметричных импульсных последовательностей уменьшаемой частоты, на выход устройства. Так как шгформацию о совпаденш соответствующих четвертей периода сигналов уменьшаемой и вычитаемой часго можно получить лишь в конце 1-штервала времени, занимаемого соответствующей четвертью периода сигнала уменьшаемой частоты, поэтому информация о моменте совпадения используется для управления прохождением на выход устройства симметри июй импульсной последовательности, задержанной по отношению к участвующей в сравнении. Это может быть импульсная последовательность, задержанная на чет верть периода и формируемая в семействе симметричных импульсных последовательностей первого канала. образом, симметричные импульсные последователь.нлх;ти, .формируемые формирователем 1 и инверторами 3 и 4, поступают на первые входы элементов И 9-12, на вторые вхо цы которых- поступают сигаалы с выходовз селектора 8. Выходной сигнал устройства формируется в результате логического слойсения в элементах ИЛИ 13, 14 н 15 напряжений, действующих на выходах логических элементов И 9-12. Каждому моменту совпадения четвертей периодов входных сигналов соогв етствует прохождение на выходе одного из элементов И одного импульса соответствующей симметричной импульсной последовательности уменьшаемой частоты. чегЕ5ерти периода сигнала вычитаемой частоты, поступающей на третий вход соответствующего элемента И 18-21 через соответствующий инвертор 22-25. В противном случае соответствующий элемент И 18-21 формирует сигнал установки триггера 26-29 в нулевое состояние одновременно с приходом сигнала на тактовый вход этого триггера, Импулл сные последовательности, поступающие на вторые входы элементов И 18-21, определяют положение заднего 4рся1та соот ветствующей четверти периода сигнала уменьшаемой частоты и, если он выходит за пределы соответствующей четверги периода сигнала вычитаемой частоты, то соответствующий элемент И 18-21 также формирует сигнал установки триггера 26-29 в нулевое состояние. Если четверть периода сигнала уменьщаемой частоты полностью лежит внутри интервала времени, занимаемой соответ ствуюшей четвертью периода сишала вычитаемой частоты, то соответствующий триггер 26-29 устанавливается в состо яние единицы и удерживает это состояние до прихода следующей четверти периода сигнала уменьшаемой частоты. С приходом новой четверти периода процесс анализа повторяется и либо происхоШЕГ смен выходного потенциала триггера 2в-29, либо он сохраняет свое значение к т.д. Формула изобретения 1. Двухканальный формирователь однополосного сигнала по авт, св. N 74686 отличающийся iSf.i, 4VO, с повышения стабильности фсрмнрованйа разностной частоты, в него ввеаеи четы рехканальныйвременной cejraiiicp, сзраая группа входов котфого coeatmeHe с входами и выходами гюрвыж двух инверторов, вторая группа входов соешшеяа с выходами формирователя, а выходы четырехка- , нального временного селектора подключены соответственно ко вторым входам зле™ ментов И. 2. Формирователь по п. 1, от л и ч а « щ „ g я тем, что четырехканальйый временной селектор содержит четыре элемента И, два входа каждого на которых соешшены соответственно с первой группой входе, а третьи входы через инверторы соединены соответственно со второй группой 1ктьфехканального вpe feннoгo селэктора, н четь}ре триггера, R - вход каждого из которых соединен с выходом одного элемента И, з счетный вход даниого триггера соецгшен с оцлим из входов этого aneNseHTa И, причем ды всех триггеров соединены между собой. Источники {шформвции, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 746861, Н ОЗ С 1/6О, 27.04.78 (прототип).

ГУ

Фае. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный формирователь однополосного сигнала | 1982 |

|

SU1125737A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для измерения мощности и герметичности цилиндров двигателля внутреннего сгорания | 1987 |

|

SU1493897A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Регулируемый конвертор | 1986 |

|

SU1365290A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С АВТОНОМНЫМ ИНДУКТОРОМ | 2005 |

|

RU2291548C1 |

| Способ воспроизведения сигналов цифровой информации с носителя магнитной записи | 1988 |

|

SU1532974A1 |

| Устройство для управления тиристорными регуляторами параллельных групп тяговых электродвигателей | 1982 |

|

SU1049284A1 |

| Следящий аналого-дискретный преобразователь для измерения частоты сигналов допплеровских измерителей скорости | 1981 |

|

SU1018192A1 |

| Одноканальное устройство для управления @ -фазным вентильным преобразователем | 1983 |

|

SU1320868A1 |

Авторы

Даты

1981-11-07—Публикация

1979-09-07—Подача