(Л

i

00

iNd

йь

гч

тора 1 через фазосдвигающий блок 2 поступает на делитель 3 частоты. Для коррекгщи на третий вход элемента ИЛИ 1А подается команда, которая через формирователь 15 поступает на установочный вход счетчиков 6 и 10. При этом с выхода дешифратора 11 сигнал поступает на вход элемента И 12. Код коррекции поступает на вход преобразователя 9 кода коррекции, с выхода кото- рого поступает в регистр 8 сдвига. Сигнал с выхода элемента И 12 через формирователь 13 поступает на элемент И 5, а сигнал с выхода блока 2 через переключатель 4, элемент И 5 и пере- слючатель 21 поступает на вход счетчика 6. Сигнал с выхода триггера 19 через инвертор 17 разрешает прохождение сигналов через блок 21. При равенстве кодов шести разрядов счетчика 6 и регистра 8 с выхода сумматора 7 сигнал через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 и триггер 19 разрешает прохождение сигнала с выхода переключателя 4 через элемент И 5 и переключатель 22 на промежуточный вход счетчика 6. Сигналы с выходов переключателей 21 и 22 через блок электронных ключей 16 поступают на дополнительные входы делителя 3 частоты. Для проведения грубой коррекции шкалы времени на первый вход элемента ИЛИ 14 поступает сигнал, которьй через элемент ИЛИ 20 поступает на вход элемента И 23 и разрешает прохождение сигнала управления на второй управляЮ1ций вход блока 2 с выхода формирователя 13. Для проведения точной коррекции на первый вход схемы ИЛИ поступает управляющий сигнал. При проведении грубой и точной коррекции шкалы времени код коррекции также как и при коррекции кода времени через преобразовател 9 кода времени записьтается в регистр 8, при этом счетчик 6 работает как единое целое. 11 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1985 |

|

SU1307598A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для формирования управляемых отметок времени | 1986 |

|

SU1370645A2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

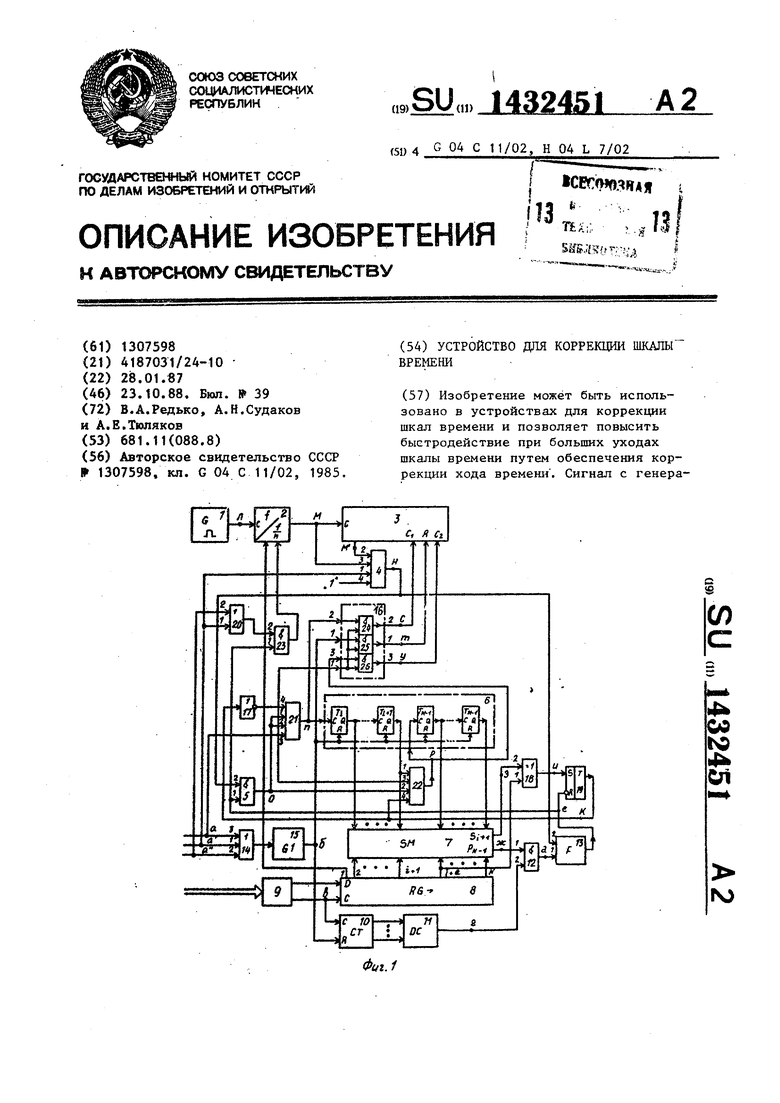

Изобретение может быть использовано в устройствах для коррекции шкал времени и позволяет повысить быстродействие при больших уходах шкалы времени путем обеспечения коррекции хода времени . Сигнал с генера

1

Изобретение относится к радиотех- Ш1ке, может быть использовано в измерительных системах и.является усовершенствованием устройства для коррекции шкапы времени по авт.ев. 9 1307598.

Цель изобретения - повышение быстродействия при больших уходах шкалы времени путем обеспечения коррекции кода времени.

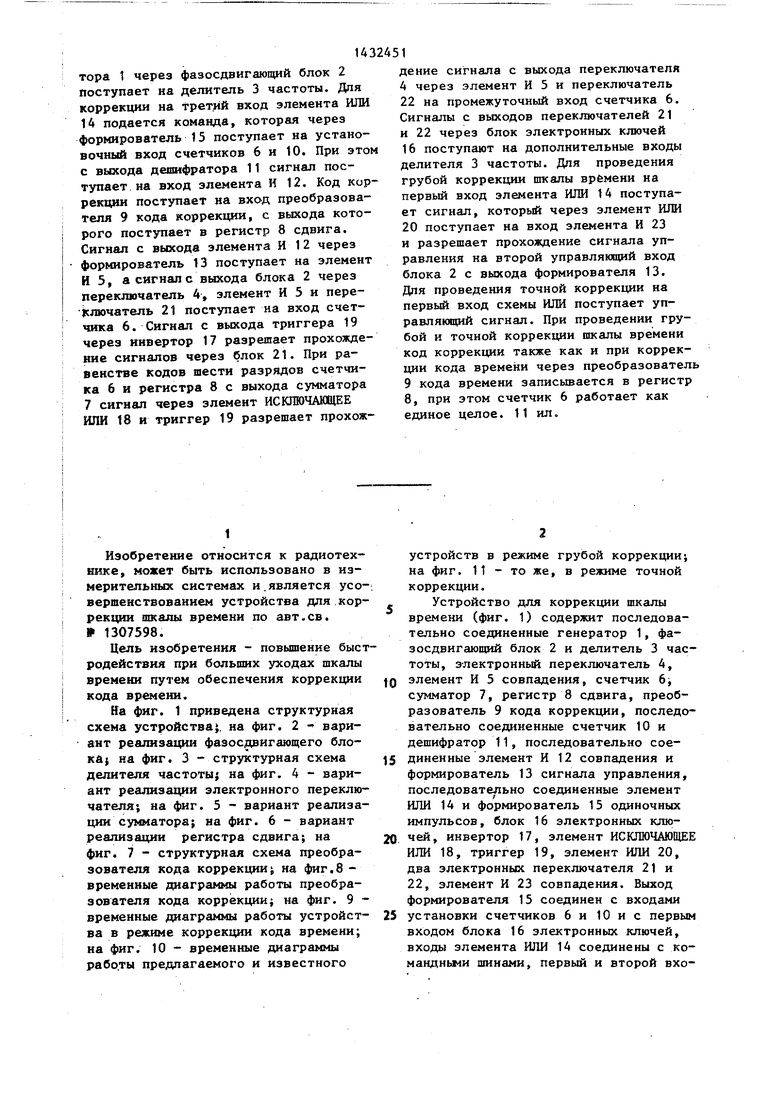

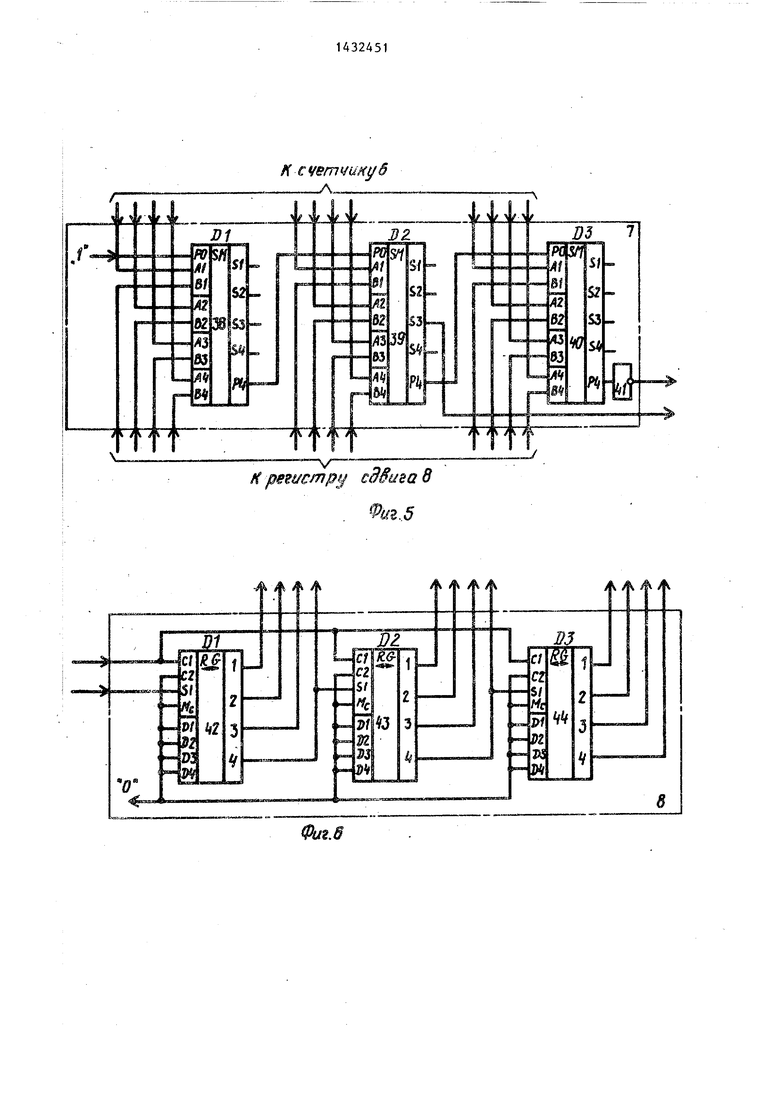

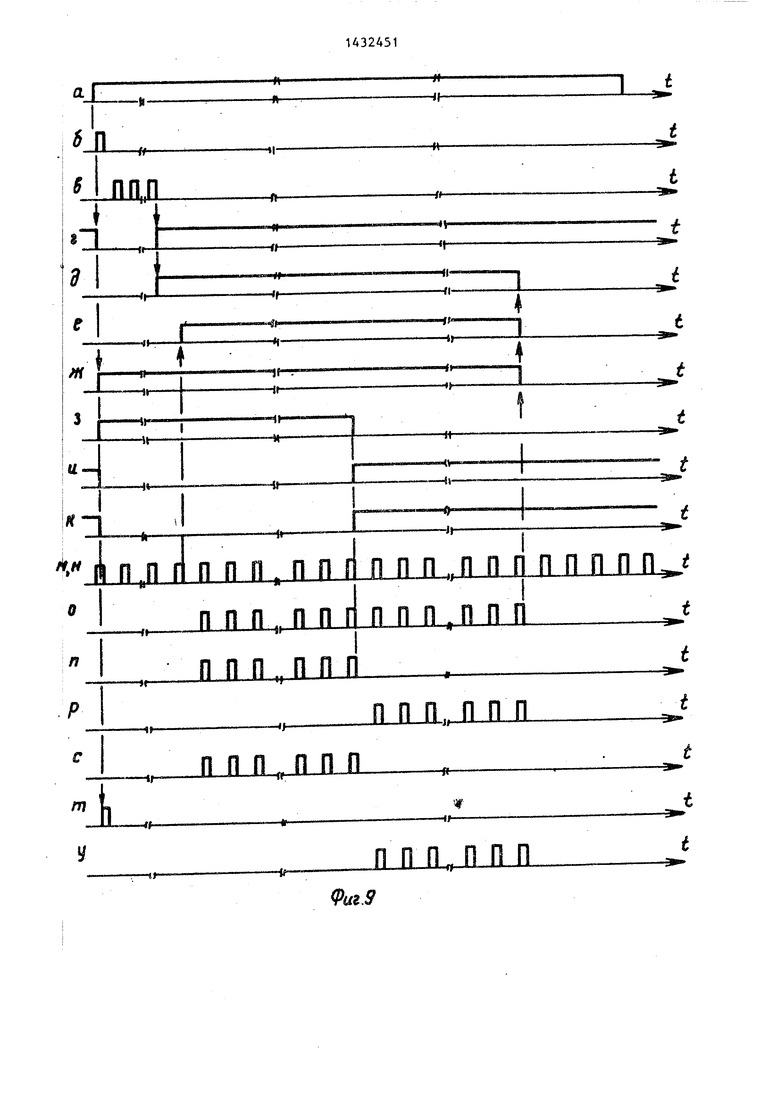

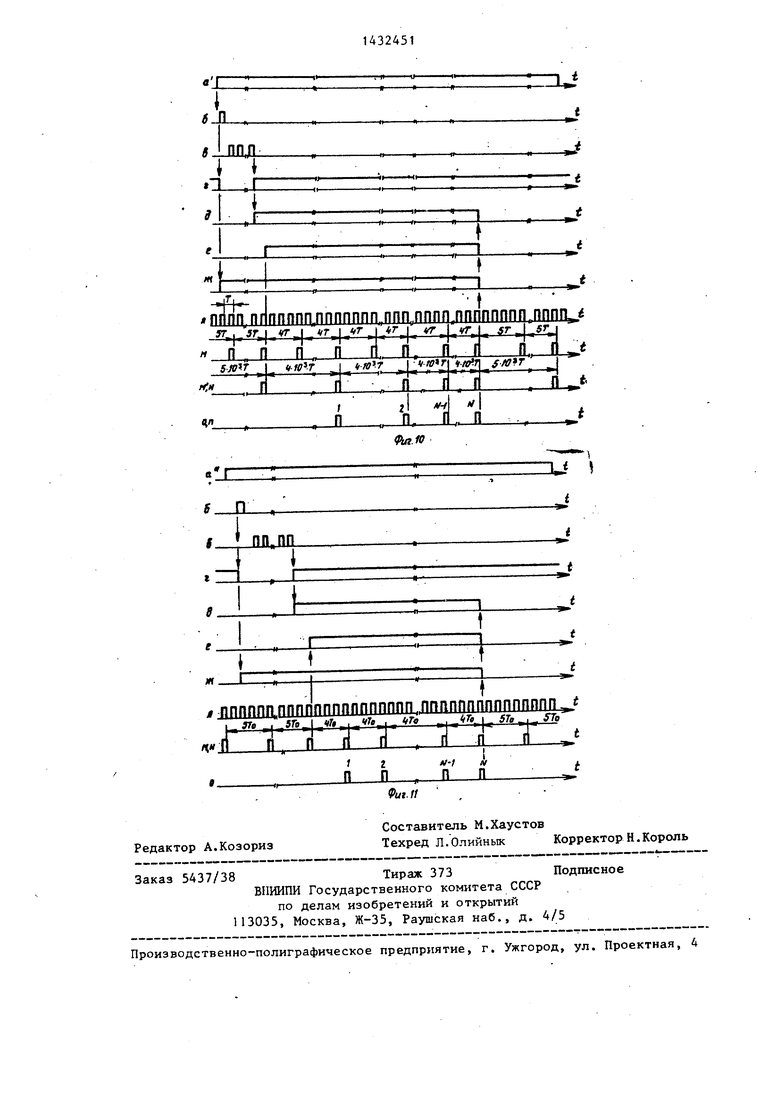

ffa фиг. 1 приведена структурная схема устройства, на фиг. 2 - вариант реализахдш фазосдвигающего блока} на фиг. 3 - структурная схема делителя частоты; на фиг. 4 - вариант реализации электронного переключателя на фиг. 5 - вариант реализации сумматора; на фиг. 6 - вариант реализации регистра сдвига; на фиг. 7 - структурная схема преобразователя кода коррекции на фиг.8 - временные диаграммы работы преобразователя кода корр гкции; на фиг. 9 - временные диаграммы работы устройст- ва в режиме коррекции кода времени; на фиг. 10 - временные диаграммы работы предлагаемого и известного

устройств в режиме грубой коррекции; на фиг. 11 - то же, в режиме точной коррекции.

Устройство для коррекции шкалы времени (фиг. 1) содержит последовательно соединенные генератор 1, фа- зосдвигаюшяй блок 2 и делитель 3 частоты, электронный переключатель 4, элемент И 5 совпадения, счетчик 6 сумматор 7, регистр 8 сдвига, преобразователь 9 кода коррекции, последовательно соединенные счетчик 10 и дешифратор 11, последовательно соединенные элемент И 12 совпадения и формирователь 13 сигнала управления, последовательно соединенные элемент ИЛИ 14 и формирователь 15 одиночных импульсов, блок 16 электронных ключей, инвертор 17, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, триггер 19, элемент ИЛИ 20, два электронных переключателя 21 и 22, элемент И 23 совпадения. Выход формирователя 15 соединен с входами установки счетчиков 6 и 10 и с первым входом блока 16 электронных ключей, входы элемента ИЛИ 14 соединены с ко- мандньми шинами, первый и второй входы элемента ИЛИ 14 соединены с соответствующими входами элемента ИЛИ 20, при этом первый вход элемента ИЛИ 14 соединен также с первым входом электронного переключателя 4, к второму входу которого подключен выход делителя 3 частоты. Выход фазосдви- гающего блока 2 соединен с третьим входом переключателя 4, выход элемен- та И 5 Совпадения соединен со счетным входом счетчика 6 через переключатель 21, второй вход которого также подключен к выходу элемента И 5, выход переключателя 21 соединен с вто- рым входом блока 16 электронных ключей. Между последовательно соединенными выходом и входом i+1-го разрядов счетчика 6 включен переключатель 22, второй вход которого подклю-20 установки R триггеров Т, - Т ц., сое- чен к выходу элемента И 5 совпадения, динены между собой и являются входом а третий вход соединен с третьим вхо- установки счетчика 6. Выходы О триг- дом переключателя 21, с управляющим входом блока 16 электронных ключей и с третьим входом элемента ИЛИ 14, 25 выход триггера 19 соединен с четвертым входом переключателя 22 и через инвертор 17 с четвертым входом переключателя 21. Третий вход блока 16

геров Т, - Tfj., являются выходами сч чика 6.

Блок 16 электронных ключей состои из трех элементов И 24-26 совпадения первые входы которых соединены между собой и являются управляющим входом блока 16, а вторые входы являются

электронных ключей соединен с выходом 30 первым, вторым и третьим входами бло

переключателя 22,,а выходы соединены соответственно с входом установки и с первым и вторым дополнительными счетными входами делителя 3 частоты. Выходы разрядов счетчика 6 соединены с входами первого слагаемого сумматора 7, входы второго слагаемого которого соединень с выходами старших (N-1)-x разрядов регистра 8 сдвига, выход младшего разряда которого подключен к первому управляющему входу фазосдвигающего блока 2. Выход переноса сумматора 7 через элемент И 12 соединен с первым входом формирователя 13, выход которого Подключен к R-входу триггера 19 и к первому входу элемента И 5 совпадения. Выход переключателя 4 соединен с вторыми входами-элемента И 5 совпадения и формирователя 13, выход которого через элемент И 23 совпадения подключе к второму управляющему входу фазосдвигающего блока 2. Второй вход элемента И 23 совпадения подключен к выходу элемента ИЛИ 20. Выходы i+2-го разряда регистра 8 сдвига иi+1-го разряда сумматора 7 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 соединены с S-входом триггера 19. Информационный и такто

вьй выходы преобразователя 9 соединены с соответствующими входами регистра 8 сдвига, а вход подключен к информационной шине, Счетный вход счетчика 10 соединен с тактовым .ВЬЕХОДОМ преобразователя 9, а выход дешифратора 11 подключен к второму входу элемента И 12 совпадения.

Счетчик 6 состоит из N-1 последовательно соединенных триггеров Т, - Tf,.,, при этом выход Q каждого предыдущего триггера соединен со счетным входом С каждого последующего триггера. Выход i-ro триггера 1 соединен со счетным входом i+1-го триггера Т,., череэ переключатель 22. Счетный вход первого триггера I является счетным входом счетчика 6. Входы

установки R триггеров Т, - Т ц., сое- динены между собой и являются входом установки счетчика 6. Выходы О триг-

геров Т, - Tfj., являются выходами счечика 6.

Блок 16 электронных ключей состоит из трех элементов И 24-26 совпадения, первые входы которых соединены между собой и являются управляющим входом блока 16, а вторые входы являются

ка 16. Выходы элементов И 24-26 совпадения являются соответственно первым, вторым и третьим выходами блока 16.

Фазосдвигающий блок 2 (фиг. 2) содержит элемент И-НЕ 27, два инвертора 28 и 29 и многофункциональное синхронизирующее устройство МСУ 30. Вход CLK МСУ 30 является счетным входом, а выход F1 - выходом фазосдвигающего блока 2. Входы элемента И-НЕ 27 являются ут1равляк)щими входами фазосдвигающего блока 2, при этом вход элемента И-НЕ 27, соединенный с входом генератора 28, является первым управляюшим входом блока 2. Входы инверторов 28 и 29 подсоединены соответственно к первому входу и выходу элемента И-НЕ 27. Выходы инверторов 28 и 29 и элемента И-НЕ 27 соединены соответственно с входами D1, D2, D3 МСУ 30, на входы V и D 4 которого подана логическая 1, а на входы ЕХР1, ЕХР2, ЕХРЗ и CLR - логический О.

Делитель 3 частоты (фиг. 3) содержит последовательно соединенные делитель 31 частоты, элемент ИЛИ 32, делитель 33 на 60 частоты (счетчик минут), элемент ИЛИ 34, делитель 35

514324516

на 24 часто.ты (счетчик часов). Вход .ляются выходами разрядов регистра 8

сдвига.

Преобразователь кода 9 коррекции

делителя 31 частоты является счетным входом делителя 3 частоты. Входы установки делителей 33 и 35 частоты являются входом установки делителя 3 частоты. Вторые входы элементов ИЛИ 32 и 34 являются соответственно первым и вторым дополнительными счетными входами делителя 3 частоты, а его выходом является,, например, выход ш-го разряда делителя 31.

Электронный переключатель 4 (21 и 22) (фиг. 4) состоит из элемента И-НЕ 36 и элемента 2И (2НЕ-И) ИЛИ- НЕ; 37, первый вход которого является первым входом электронного переключателя 4 (21 и 22), второй и третий входы являются третьим входом электронного переключателя 4 (21 и 22), четвертый вход подключен к выходу элемента И-НЕ 36, а выход является выходом электронного переключателя 4 (21 и 22). Выходы элемента И-НЕ 36 являются вторыми и четвертым входами электронного переключателя 4 (21 и 22).

Двенадцатиразрядньй сумматор 7 (фиг, 5) состоит из трех четырехразрядных сумматоров 38-40 и инвертора 41. На вход переноса РО сумматора 38 подана логическая 1. Входы первого А; и второго В; слагаемого сумматоров 38-40 являются соответственно входами первого и второго слагаемых сумматора 7. Вьиод переноса Р4 каждого предыдущего сумматора 38 (39) соединен с входом переноса РО каждого последующего сумматора 39 (40). Выход переноса последнего .сумматора 40 подключен к входу инвертора 41, выход которого является выходом переноса сумматора 7. Выход S3 третьего разряда суммы сумматора 39 является выходом i+1-го (где i+1 7) разряда суммы (S; +1) сумматора 7.

Двенадцатиразрядный регистр 8 сдвига (фиг. 6) содержит три регистра 42-44. Информационный вход S1 регистра 42 является информационным входом регистра 8 сдвига, а его тактовый вход С1 - тактовым входом регистра 8 сдвига. Тактовые входы регистров 42-44 соединены между собой. Выход четвертого разряда каждого предьщущего регистра 42 (43) соединен с информационным входом SI каждого последующего регистра 43 (44). Выходы разрядов регистров 42-44 яв30

(фиг. 7) состоит из элемента ИЛИ АЗ, триггера 46 и элемента 47 задержки. S- и R-входы триггера 46 соединены с входами элемента ИЛИ 45 и подключе ны к шине кода коррекции. Инверсный

Q выход триггера 46 является информационным выходом преобразователя 9. Выход элемента ИЛИ 45 соединен с вхо дом элемента 47 задержки, выход кото рого является тактовым выходом преоб

15 разователя 9.

Формирователь 13 сигнала управления может быть выполнен на DC-триггере, при этом R-вход триггера является первым входом, а вход синхрони2Q зации триггера - вторым входом формирователя 13. На 1-вход триггера подана логическая 1, на вход К - логический О. Прямой выход триггера является выходом формирователя 13

25 Устройство для коррекции шкапы времени работает следующим образом.

Генератор 1 является источником импульсов с периодом повторения Т (фиг. Юл и 11л) для запуска фазо- сдвигающего блока 2, который выполнен в виде делителя частоты с переменным коэффициентом деления. В исходном состоянии коэффициент деления равен К (пусть К 5), что определя ется наличием на втором управляющем входе уровня логического О, поступающего через элемент И 23 с выхода формирователя 13 (фиг. tOe).

С выхода фазосдвигающего блока 2

.Q импульсы подаются на вход делителя 3 частоты. Б делителе 3 частоты производится деление частоты входных им пульсов, например, до 1/60 Гц делите лем 31 частоты, иа выходах разрядов которого формируются импульсы проме жуточных частот. Под промежуточными частотами понимают частоты импульсны сигналов делителя 31 частоты, получающиеся при последовательном делени входной частоты. Сигналы с выхода т- го разряда делителя 31 частоты подаются на второй вход электронного переключателя 4. Сигналы 1/60 Гц с выхода делителя 31 частоты через элемент ИЛИ 32 (фиг. 3), делитель 33 на 60 частоть, представляющий собой сче чик минут, и элемент ИЛИ 34 подаются на делитель 35 на 24 частоты, представляющий собой счетчик часов, в ре

35

45

50

55

0

(фиг. 7) состоит из элемента ИЛИ АЗ, триггера 46 и элемента 47 задержки. S- и R-входы триггера 46 соединены с входами элемента ИЛИ 45 и подключены к шине кода коррекции. Инверсный

Q выход триггера 46 является информационным выходом преобразователя 9. Выход элемента ИЛИ 45 соединен с входом элемента 47 задержки, выход которого является тактовым выходом преоб5 разователя 9.

Формирователь 13 сигнала управления может быть выполнен на DC-триггере, при этом R-вход триггера является первым входом, а вход синхрониQ зации триггера - вторым входом формирователя 13. На 1-вход триггера подана логическая 1, на вход К - логический О. Прямой выход триггера является выходом формирователя 13.

5 Устройство для коррекции шкапы времени работает следующим образом.

Генератор 1 является источником импульсов с периодом повторения Т (фиг. Юл и 11л) для запуска фазо- сдвигающего блока 2, который выполнен в виде делителя частоты с переменным коэффициентом деления. В исходном состоянии коэффициент деления равен К (пусть К 5), что определя ется наличием на втором управляющем входе уровня логического О, поступающего через элемент И 23 с выхода формирователя 13 (фиг. tOe).

С выхода фазосдвигающего блока 2

Q импульсы подаются на вход делителя 3 частоты. Б делителе 3 частоты производится деление частоты входных импульсов, например, до 1/60 Гц делителем 31 частоты, иа выходах разрядов которого формируются импульсы промежуточных частот. Под промежуточными частотами понимают частоты импульсных сигналов делителя 31 частоты, получающиеся при последовательном делении входной частоты. Сигналы с выхода т- го разряда делителя 31 частоты подаются на второй вход электронного переключателя 4. Сигналы 1/60 Гц с выхода делителя 31 частоты через элемент ИЛИ 32 (фиг. 3), делитель 33 на 60 частоть, представляющий собой счетчик минут, и элемент ИЛИ 34 подаются на делитель 35 на 24 частоты, представляющий собой счетчик часов, в ре5

5

0

5

7143

зультате чего на выходах разрядов делителей 33 и 35 частоты производится формирование кода времени. Сигналы, представляющие собой автономную шкалу времени, используются потребителями для синхронизации работы других устройств, входящих в одну систему с данным устройством. Потребители могут использовать необходимые для их работы сигналы автономной шкалы времени, снимая их с соответствующих выходов разрядов делителей 31, 33 и 35 частоты.

Таким образом, делитель 3 частоты осуществляет формирование и хранение шкалы времени, под которой понимают совокупность импульсных сигналов на выходах делителя 31 частоты и кода времени, формируемого делителями 33 и 35 частоты.

При наличии расхождения между шкалами времени устройства и образцовых часов производится коррекция шкалы времени, При больших (до 1 сут) рас- хождениях этих шкал времени коррекция проводится в три этапа: коррекция кода времени, а также грубая и точная коррекция, заключающиеся в грубо и точной коррекции фазы импульсных сигналов, образующих шкалу времени.

Для коррекции кода времени на третью командную шину подается команда в виде логической 1 (фиг. 9а), которая через элемент ИЛИ 14 поступает на формирователь 15. На выходе формирователя 15 появляется импульс (фиг. 9б), которьм сбрасывает счетчики 6 и 10. При этом на выходе дешифратора 11 появляется логический О ,(Фиг. 96), на выходе переноса сумматора 7 - логическая 1 (фиг. 9ж), на выходе i+1-го (седьмого) разряда суммы сумматора 7, подключенного к элементу 18,- логическая 1 (фиг.9з Предположим, что в i+2-м (восьмом) разряде регистра 8 сдвига содержится логическая 1. В этом случае на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ 18 появляется логический О, который появляется и на вькоде триггера 19 (фиг. Эк), поскольку на его R-входе присутствует логический О с выхода формирователя 13.

Импульс с выхода формирователя 15 через блок 16 электронных ключей, открытый сигналом на управляющем входе блока 16, проходит на вход устаноки делителя 3 частоты (фиг. 9т).

Q

5 o

5 о

.„ .

5

55

При этом происходит сброс делителей 33 и 35 (фиг. 3) в делителе 3 частоты, т.е. сброс кода времени. Команда с третьей командной шины подается на третьи входы электронных переключателей 21 и 22, разрешая в этих переключателях прохождение сигналов с выхода элемента И-НЕ 36 (фиг. 4) через элемент 2И(2НЕ-И)ИЛИ-НЕ 37. Логический О с выхода триггера 19 (фиг. 9к) подается на четвертый вход переключателя 22, запрещая прохождение через него сигналов, и через инвертор 17 на четвертый вход переключателя .21, разрешая прохождение сигналов с выхода элемента И 5 на выход переключателя 21 через элемент И-НЕ 36 (фиг. 4).

По шине кода коррекции производится ввод в устройство N-разрядного последовательного кода коррекции, который представляет собой импульсный код,подающийся старшимиразрядами вперед по двум линиям связи в виде прямого и инверсного кодов. Единице кода коррекции соответствует наличие 1Ф1пульса на линии Связи прямого кода и отсутствие импульса на линии инверсного кода. Код коррекции имеет, например, при N 12 следующую структуру: младший разряд - произвольный, следующие шесть разрядов - код минут текущего времени, старшие пять разрядов - код часов текущего времени об- разг.овых часов.

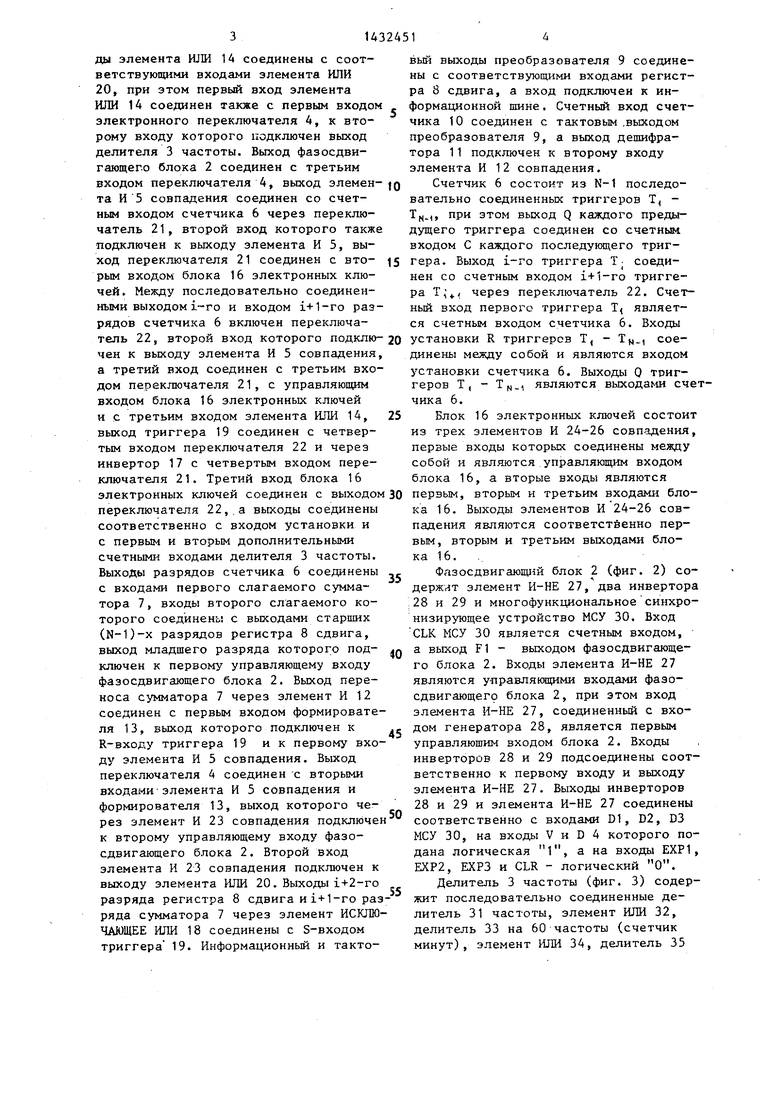

.од коррекции поступает на преобразователь 9 кода коррекции (фиг. 7), причем импульсы прямого кода поступают на S-вход триггера 46 преобразователя 9 (фиг. 8а), а импульсы инверсного кода - на его R-вход (фиг. 8б). На инверсном ВЕзкоде триггера 46 формируется последовательный инверсньй код коррекции (фиг. 8в). На выходе элемента ИЛИ 45 из импульсов прямого и инверсного кодов формируется так-, товая серия импульсов сдвига (фиг. 8г), которая через эл емент 47 задержки поступает на тактовый выход преобразователя 9 (фиг. 8д, 9в). Задержка тактовых импульсов сдвига обеспечивает надежную запись инверсного кода Коррекции в регистр 8 сдвига.

Разряды инверсного кода коррекции поочередно подаются с инверсного выхода триггера 46 преобразователя 9 (фиг. 7) на информационный вход регистра 8 сдвига и записываются в него под воздействием импульсов сдвига на тактовом входе таК;, что во 2, 3, ... i-t-1-й разряды (где 1 6) записывается код минут, а в i+2, i+3, ...., N-разряды - код часов (, N « 12). Одновременно счетчик 10 подсчитывает число тактовых импульсов сдвига. Как только в регистр 8 сдвига записывается последний разряд кода, на выходе дешифратора 11 появляется логическая (фиг, 9г), которая через элемент И 12 совпадения, открытый сигналом логической 1 с выхода переноса cy мaтopa 7 (фиг 9ж), проходит на первый вход формирователя 13 (фиг. 9д), разрешая изменение состояния последнего под воздействием импульсов на втором входе . После э того первый же импульс, поступакяций с выхода фазосдвигающего блока 2 через переключатель 4 на второй вход формирователя 13 (фиг. 9м, и), срезом устанавливает на выходе формирователя 13 логическую 1 (фиг. 9е). Этот сигнал открывает элемент И5 совпадения, и импулхЛы с выхода переключателя 4 начинают проходить на вторые входы переключателей 21 и 22 (фиг. 9о). Поскольку на выходе триггера 19 присутствует логический О (фиг. 9к), переключатель 22 закрыт, а переключатель 21 открыт Импульсы с выхода элемента И 5 совпадения через переключатель 21 проходя на счетньй вход триггера Т, счетчика 6 (фиг. 9п) и через блок 16 электронных ключей на первый дополнительный счетный вход делителя 3 частоты (фиг. 3), т.е. счетчик минут.

Счетчик производит счет импульсов до тех nopi, пока не произойдет совпадение кода на выходах его разрядов с кодом минут, инверсная копия которого записана во 2, 3, ... i+1-м разрядах регистра 8 сдвига. При этом в сумматоре 7 появляется перенос из i-ro (шестого) разряда в i+1-й (седьмой).

Рассмотрим случай 5 кох да на. (седьмой) разряд второго слагаемого сумматора 7 подается логическая 1 с i+2-го (восьмого) разряда регистра 8 сдвига -В этом случае в седьмом разряде суммы сумматора 7 (S;) появляется логический О (фиг. 9з). Этот сигнал поступает на второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 18, в результате чего на его выходе появляется

5

5

логическая 1 (фиг. 9и), так как на первый вход злемента 18 в данном случае также поступает логическая 1 с восьмого разряда регистра 8 Сдвига Если же в восьмом разряде регистра 8 сдвига будет логический О, то на выходе элемента ИСКШОЧАКЩЕЕ ШШ 18 также появится логический 1, так Q как перенос из шестого в седьмой разряды сумматора 7 вызывает появление логической 1 в седьмом разряде суммы

Логическая 1 с выхода элемента ИСКЛЮЧАЩЕЕ ИЛИ 18 (фиг. 9и) переворачивает триггер 19 (фиг. 9к), на R-входе которого присутствует логическая 1 с выхода формирователя 13. Логическая 1 с выхода триггера 19 (фиг. 9к) разрешает прохождение импульсов с выкода элемента И 5 совпадения через переключатель 22 на триггер Т счетчика 6 и запрещает прохождение сигналов через переключатель 21 на триггер Т.

Таким образом,, через переключатель 21 проходит пачка импульсов, число которых cooTBeTcfByeT коду минут, содержащемуся в коде коррекции, т.е. числу минут текущего времени. Эта пачка импульсов заполняет ранее сброшенный делитель 33 частоты в делителе 31 частоты (фиг. 3) ., при этом код на выходах разрядов делителя 33 соответствует коду минут текущего времени.

Счет импульсов с выхода элемента И 5 совпадения продолжает вторая часть счетчика 6, выполненная на триггерах Т.,. При этом импульсы с выхода переключателя 22 (фиг. 9р) проходят через блок электронных ключей 16 на второй дополнительный счетный вход делителя 3 частоты (фриг. 9у), заполняя через элемент ИЛИ 34 ранее сброшенный делитель 35 частоты (фиг. 3), т.е. счетчик часов.

Как только код на выходах разрядов второй части счетчика 6 совпадает с кодом часов, храняющимся в инверсном виде в старпшх пяти разрядах регистра 8ксдвига, на выходе переноса сумматора 7 появится логический О (фиг. 9ж). На выходе элемента И 12 совпадения также появляется логический О (фиг, 9д), который возвращает формирователь 13 в исходное состояние Логический О с выхода формирователя 13 (фиг. 9е) запирает элемент И 5 совпадения.

0

5

0

0

5

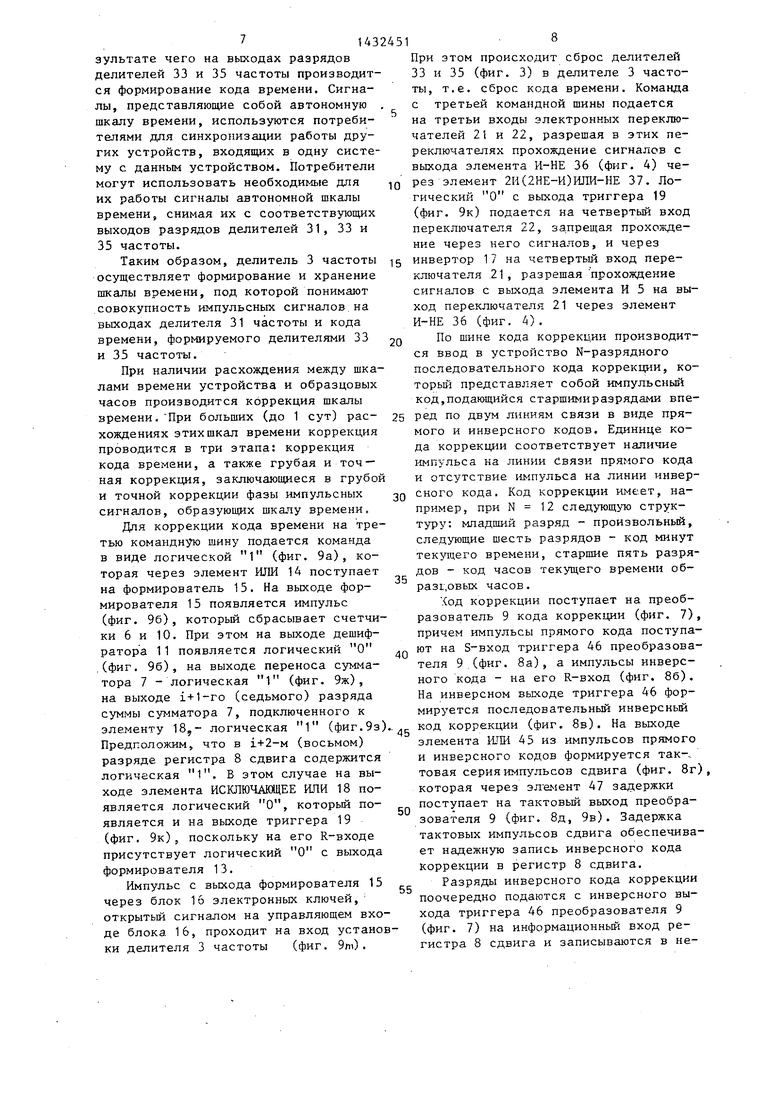

Таким образом, через переключатель 22 проходит пачка импульсов, число которых соответствует коду часов, содержащемуся в коде коррекции, т.е. числу часов текущего времени. Эта пачка импульсов заполняет делитель 35 частоты в делителе 3 частоты (фиг. 3) при зтом код на выходах разрядов делителя 35 частоты соответствует коду часов текущего времени. Таким образом, в результате первого этапа коррекции шкалы времени производится коррекция кода времени в делителе 3 частоты. Второй и третий этапы коррекции (грубая и точная коррекция) производятся так же, как в известном устройстве. Для проведения грубой коррекции шкалы времени на первую командную шину подается логическая 1 (фиг. 10а), которая через элемент ИЛИ 14 проходит на формирователь 15. На выходе формирователя 15 появляется импульс (фиг. 106 который сбрасьшает счетчики 6 и 10. На выходе дешифратора 11 появляется логический О (г. Юг), а на выходе переноса сумматора 7 - логическая 1 (фиг. 10ж).

Команда (логическая 1, фиг.Юа) через элемент ИЛИ 20 подается также на второй вход элемента И 23 совпадения, разрешая прохождение сигнала управления на второй управляющий вход фазосдвигающег.0 блока 2 с выхода формирователя 13. Кроме того, команда поступает на третий вход переключателя 4, при этом на выход переключателя 4 проходят импульсы с выхода делителя 3 частоты (фиг.10м,к).

На третьей командной шине в этом режиме присутствует уровень логического О, которьй запирает блок 16 электронных ключей и воздействует на третьи входы переключателей 21 и 22. При этом на выход переключателей 21 и 22 проходят сигналы с их первых входов. Выход элемента И 5 совпадения в этом случае через переключатель 21 соединен со счетньм входом счетчика 6, а вькод шестого разряда счетчика 6 (триггер Т; ) через переключатель 22 соединен со счетным входом его следующего седьмого разряда (триггер Т,-,).

Таким образом, при грубой коррекции счетчик 6 работает как единое целое в отличие от коррекции кода времени, когда этот счетчик разделен

5

5

переключателем 22 на две независимые части.

После подачи логической 1 на первую командную шину производится запись в регистр 8 сдвига кода коррекции аналогично записи кода при коррекции кода времени. При этом код коррекции имеет следующую структуру: в младшем разряде - знак коррекции, в старших разрядах - величина коррекции.

Аналогично коррекции кода времени после записи кода в регистр 8 сдвига на выходе дешифратора 11 появляется . логическая 1 (фиг. Юг), которая через элемент И 12 совпадения, открытый логической 1 с выхода сумматора 7 (фиг. 10ж), проходит на первый вход формирователя 13. По срезу первого импульса на втором входе формирователя 13 на его выходе появляется сигнал управления в виде логической 1 (фиг. Юе), который разрешает прохождение импульсов через эле- . мент И 5 совпадения на счетчик 6 (фиг. 10о,п) и изменяет коэффициент деления фазосдвигающего блока 2 на К t1 в зависимости от знака коррекции, поступающего на второй управляющий вход с выхода младшего (первого) разряда регистра 8 сдвига. На фиг.10 в качестве примера показано изменение коэффициента деления фазосдвигающего блока 2 с К 5 на К-1 4.

Первый после изменения коэффициента деления импульс на выходе фазor сдвигающего блока 2 появляется на время Т раньше или позже, чем при исх;од- ном коэффищ1енте деления, второй импульс - на время 2Т раньше или позже и т.д. (Т - период повторения импульсов генератора 1). Таким образом, изменение коэффициента деления фазо- 5 сдвигающего блока вызьшает изменение фазы его выходных импульсов и приводит к сдвигу шкалы времени.

Счетчик производит счет импульсов с выхода переключателя 4. Двоичный код с выходов разрядов счетчика 6 подается на входы первого слагаемого сумматора 7, на входы второго слагаемого которого подается величина коррекции в инверсном коде с выходов старших N-1-X разрядов регистра 8 сдвига. Как только в счетчике 6 окажется записанным код, равный величине коррекции, на выходе переноса сумматора 7 появляется логический О

0

5

0

0

5

13

(фиг, 10ж). Hd выходе элемента И 12 совпадения появляется логический О (фиг. 10д), который возвращает формирователь 13 в исходное состояние. Логический О с выхода формирователя 13 (фиг. 10е) запрещает прохожде- :ние импульсов через элемент И 5 сов:падения на счетчик 6 и врсстанавливаIет исходный коэффициент деления фазоjсдвигающего блока 2.

; Величина грубой коррекции равна

j ±Т-М К,

I где Т - период повторения импульсов

i генератора 1;

I М - величина коррекции;

j К - коэффициент деления делителя

I 3 частоты от.входа до т-го.

: выхода (на фиг, 10 К( 10).

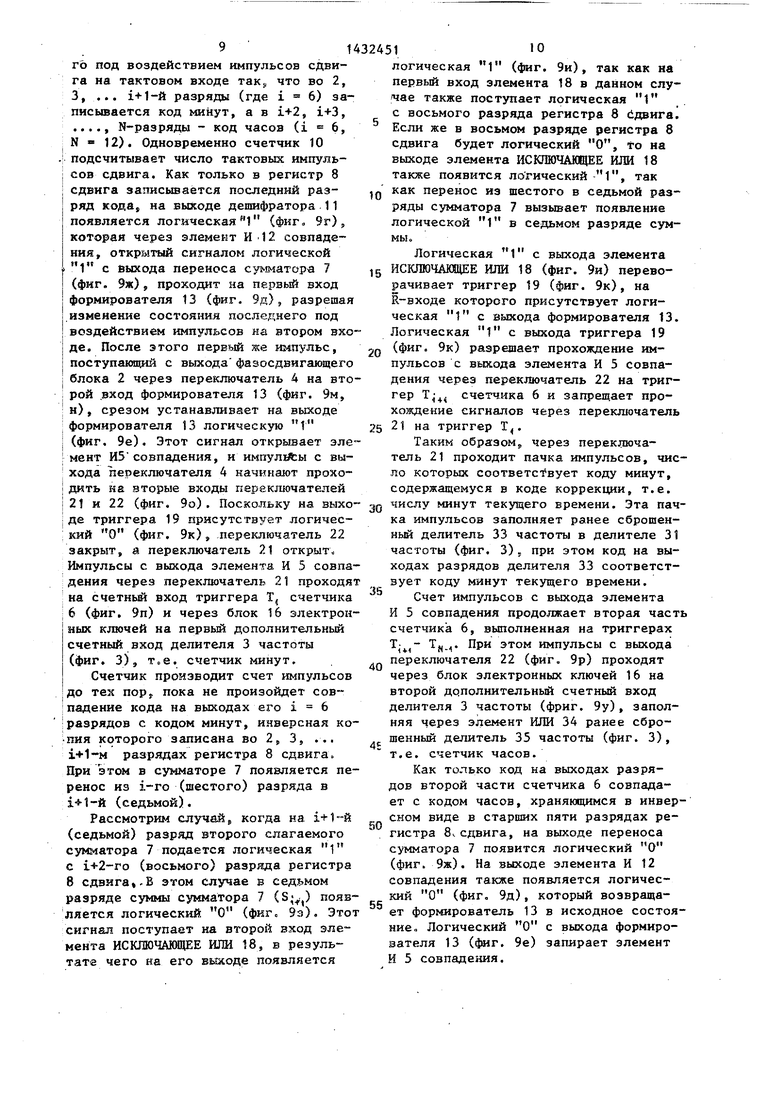

После Грубой коррекции проводится аналогично точная коррек1р1я.

На второй командный вход подается логическая 1 (фиг. 11 а). Импульсом с выхода формирователя 15 производится сброс счетчиков 6 и 10 (фиг. 116, г, д, ж). Затем в устройство вводится код коррекции и происходит точная

i коррекция аналогично грубой. Посколь: ку на третьем входе электронного пе реключателя 4 присутствует.логический

: на его выход проходят импульсы с

выхода фазосдвигающего блока 2 (а не

с делителя 3 частоты).

Формула изобретения

Устройство для коррекции шкалы времени по авт.ев № 1307598, отличающееся тем, что, с целью повышения быстродействия при больших уходах шкалы времени в устройство введены блок электронных ключей, инвертор, элемент ИСКЛЮЧАЩЕЕ ИЛИ, триггер, дополнительный элемент ИЛИ, два дополнительных электронньлх переключателя и дополнительный элемент совпа

дения, элемент ИЛИ выполнен с тремя входами, делитель частоты выполнен с четырьмя входами, электронный переключатель выполнен с четьфьмя входаU32451

1А

0

5

5

0

в

5

ми, причем первый дополнительный электронный переключатель включен между последовательно соединенными первым элементом совпадения и первым счетчиком, между последовательно сое- диненнь1ми выходом i-ro и входом (i+1)- го разрядов первого счетчика включен второй дополнительньй электронньй переключатель, а между последовательно соединенными выходом формирователя сигнала управления и вторым управляющим входом фазосдвигающего блока включен дополнительный элемент совпадения, при этом выход первого элемента совпадения соединен с вторыми входами первого и второго дополнительных электронных переключателей, третьи входы которых подключены к входу управления блока электронных ключей и к третьему входу элемента ИЛИ, выход триггера соединен с четвертым входом второго дополнительного электронного переключателя и через инвертор с чет- вертьм входом первого дополнительного электронного переключателя, первый вход блока электронных ключей подключен к выходу формирователя одиночных импульсов, второй и третий входы соединены с выходами первого и второго дополнительных электронных переключателей, соответственно-, первый, второй и третий выходы блока электронных ключей подключены к входу установки и к первому и второму дополнительным счетным входам делителя частоты соответственно, первый и второй входы дополнительного элемента ИЛИ соединены соответственно с первым и вторым входами элемента ИЛИ, а выход подключен к второму входу дополнительного элемента совпадения, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом (i+2)-ro разряда регистра сдвига, второй вход подключен к выходу (i+1)-ro -разряда суммы сумматора, а выход соединен с S-входом триггера, R-вход которого подключен к выходу формирователя сигнала управления.

К Sbi/iodoM Ълока 16 9иг.З

fe.V

К cvsmvuN d

-Л™

Фш,В

9u.8

иг.5

| Устройство для коррекции шкалы времени | 1985 |

|

SU1307598A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-23—Публикация

1987-01-28—Подача