I

Изобретение относится к информа ционно-преобразовательной технике и может быть использовано для кодирования значений фазовых углов с повышенной точностью.

Известен двухканальный преобразователь фаза-код с гетеродинным преобразованием частоты сигналов, сдвинутых по фазе. В этом устройстве введение третьего коммутируемого канала с гетеродинированием.для поочередного преобразования входных сигналов позволяет формировать управляющий сигнал, пропорциональный фазовой неидентичности основных канапов 1 |.

Недостатком этого преобразователя является трудность выполнения двух избирательных усилителей в основных каналах с перекрестными (зеркальными) фазочастотными характеристиками.

Наиболее близким по технической сущности является измерительный преобразователь фаза-1 од, содержащий

три преобразовательных канала, автоматические переключатели, два преобразователя фазоэого сдвига в число импульсов, реверсивный счетчик q регистрами памяти на выходе, счетчнк с регистром памяти на выходе и блок управления Г21

Недостатком этого устройства является неполное исключение инструментальных погрешностей преобразования фазового сдвига в код. Так, погрешности основного преобразователя фазового, сдвига в число импульсов, в котором осуществляется промежуточное преобразование фазового сдвига во временной иитервап, не обнаруживаются системой коррекции и поэтому не исключаются. Погрешности кодирования временного интервала, возникаю, щне от нестабильности частоты счетных импульсов и нестабильности фронтов кода1руемого интервала, также не корректируются .

Цель изобретения - повьпиение точности преобразования.

Поставленная цель достигается тем что в преобразователь, содержащий в каждом из трех преобразовательных каналов смеситель и последовательно соединенный с ним избирательнь1й усилитель, общий для всех преобразовательных каналов гетеродин, два преобразователя фазового сдвига в число импульсов, причем входы одного из них соединены с выходами избирательных усилителей первого и второго преобразовательных каналов, входы . другого - с выходами избирательных усилителей второго и третьего преобразовательных каналов, счетчик импульсов с двумя регистрами памяти на выходе, реверсивный счетчик импульсов с регистром памяти на выходе, входы счетчиков импульсов соединены с выходами первого и второго преобразователей фазового сдвига в число импульсов соответственно, автоматический переключатель, своими входами соединенный с сигнальными входами смесителей первых двух преобразовательных каналов, а выходом - с сигнальным входом смесителя в третьем преобразовательном канале, блок управления, выходы которого соединены с управляющими входами счетчиков импульсов, регистров памяти и автоматического переключателя, введены формирователь коротких импульсов и три триггерных делителя частоты, входы которых соединены с выходом формирователя коротких импульсов, входом подключенного к общему гетеродину, выход первого триггерного делителя частоты соединен с управляющим входом смесителя первого преобразовательного канала, первый выход второго триггерного делителя частоты соединен с управляющим входом смесителя второго преобразовательного канала, а второй первым входом блока управления, первый вход третьего триггерного делителя частоты подсоединен к управляющему входу смесителя третьего преобразовательного канала, а второй выход i ко второму входу блока управления, установочные входы -первого триггерного делителя частоты соединены с выходом рА-истра памяти реверсивного счетчика импульсов, выходы регистра памяти другого счетчика

соединены с установочными входами второго триггерного делителя частоты.

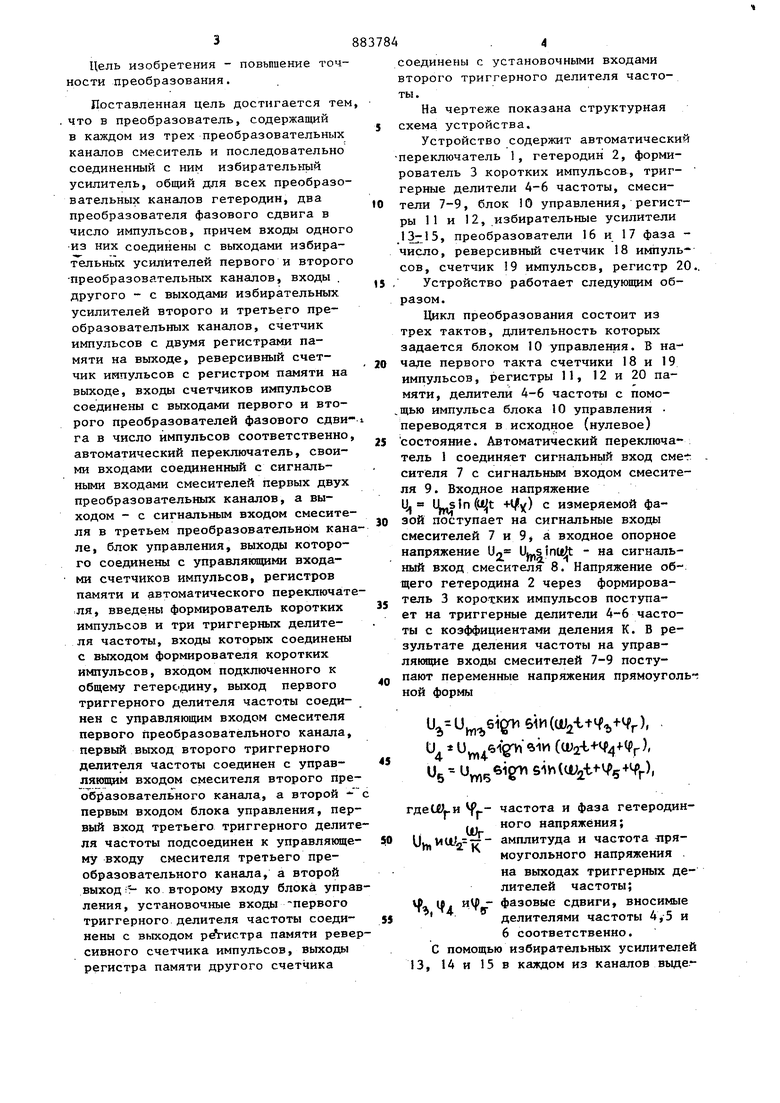

На чертеже показана структурная схема устройства.

Устройство содержит автоматический переключатель 1, гетеродин 2, формирователь 3 коротких импульсов, триггерные делители 4-6 частоты, смесители 7-9, блок 0 управления, регистры 11 и 12, избирательные усилители ., преобразователи 16 и 17 фаза число, реверсивный счетчик 18 импульсов, счетчик 19 импульсов, регистр 20

Устройство работает следующим образом.

Цикл преобразования состоит из трех тактов, длительность которых задается блоком 10 управления. В начале первого такта счетчики 18 и 19 импульсов, регистры 11, 12 и 20 памяти, делители 4-6 частоты с помо,щью импульса блока 10 управления переводятся в исходное (нулевое) состояние. Автоматический перекпюча тель 1 соединяет сигнальный вход сме сителя 7 с сигнальным входом смесителя 9. Входное напряжение У, (Ul{t +t/y) с измеряемой фазой поступает на сигнальные входы смесителей 7 и 9, а входное опорное напряжение U2 Uy sinutt - на сигнальный вход смесителя 8. Напряжение общего гетеродина 2 через формирователь 3 коротких импульсов поступает на триггерные делители 4-6 частоты с коэффициентами деления К. В результате деления частоты на управляющие входы смесителей 7-9 поступают переменные напряжения прямоуголь ной формы

) и 4. (и;2-ь--Ч4 Ч г), 5 - 5ih((,

гдеШ..и j.- частота и фаза гетеродин. , ного напряжения; амплитуда и частота прямоугольного напряжения . на выходах триггерных делителей частоты;

H(f - фазовые сдвиги, вносимые делителями частоты 4,5 и

6 соответственно.

С помощью избирательных усилителей 13, 14 и 15 в каждом из каналов выде1ЯЮТСЯ гармонические напряжения Ux, U, Ug разностной частотыW + .-Kfi), U - U cos (,1Й2 + ), ( , , и фазовые сдвиги. вносимые смесителем и избирательным усилителем каждого из каналов. Фазовый сдвиг между выходными нап ряжениями избирательных усилителей 13и 14 с учетомфазовой неидентичности каналов определяется выражением, . фазовая погрешность, вносимая неидентичностью фазовых характеристик преобразоватгльных звеньев 7,8, 13 и 14. Фазовый сдвиг между выходными нап ряжениями избирательных усилителей 14и 15с учетом фазовой неидентичности каналов определяется выражением, фазовая погрешность, вносимая неиндентичностью фазовых ха ра{стеристик преобразовательных звень ев 8,9, 14 и 15. Фаза, вносимая делителями 4-6 час тоты, определяется начальной установ кой их триггеров. При установке всех триггеров делителей в начальное состояние вносимые ими фазовые сдвиги равны 5 Y . Фазовый сдвиг V{), помощью преобразователя 16 фазо ,-. JL ft f n f-rt-t« -w44 тч 4гтлчтэ . MM Г.ОГО сдвига в последовательность иМ пульсов и счетчика 19 импульсов преобразуется в код Njf, который записывается в регистр 12 (, где К - масштабный коэффициент преобразования фаза.- код преобразователя 16 и счетчика 19; utpg- погрешность преобразования фаза - код, вносимая блоками 16 и 19. Фазовый сдвйг1/ ас помощью преобразователя 1 7 фазового сдвига в последовательность импульсов и реверсив ного счетчика 18 импульсов, работа46ющего в режиме Сложение, преобразуется в промежуточный код N2 , ,)г где К - масштабный коэффициент преобразования фаза - код преобразователя 17 и счетчика 18; - погрешность преобразования фаза - код, вносимая блоками I 7 и 18. Во втором такте по сигналу блока 10 управления автоматический переклю чатель 1 соединяет сигнальный вход смесителя 8 с сигнальным входом сме- сителя 9. При этом на преобразователь 17 воздействует фазовый сдвигЦ / J-U-V; + 4- ; Код, записанный в регис ре 12 памяти, по принципу временной задержки преобразуется в сдвиг фаз напряжений U и для этого делитель 6 частоты снова переводится в начальное состояние, т.е. If Чо момент, когда все триггеры делителя. 6 переходят из состояния Единица в состояние Нуль на второй вход блока 10 управления поступает сигнал, по которому блок 10 управления выдает коьйнду переписи числа N.записанноно в регистре 12, в делитель 5, вследствие чего всё триггеры делителя 5 устанавливаются в состояния, определяемые кодом N. Таким образом, фазовый сдвиг вносиМый делителем 5 частоты бпределяется выражением 4.,т,--Фо+ .,), рде jJ, - масштабный коэффициент преобразования код - фаза делителя 5 частоты. На вход счетчика 18, переведенного во втором такте в режим Вычитание, постзшает последовательность, импульсов, пропорциональная фазовому сдвигу у -. При этом в счетчик 8 заносите} промежуточный код М -KaUV 2.o,) (А(4 о ,-у -ч о i AU и . .6Яl,,,,. . результате двух тактов преобразования в реверсивном счетчике 18 формируется разностный код (N-j-.N), который при выборе К равен N4 ), т.е. разностный код пропорционален фазовой погрешности от неидентичности фазовых характеристик каналов и кодирующих блоков. Разностный (корректирующий) код по сигналу блока 10 управления записывается в конце такта в регистр 11 памяти. В третьем такте по сигналу блока 10 делитель 5 частоты переводится в начальное состояние .(M} VQ). В момент, когда все триггеры делителя 5 переходят из состояния Еди ница в состояние Нуль, на первый вход блока 10 поступает сигнал, по которому блок 10 выдает команду пере писи числа Ил, записанного в регистре 11, в делитель 4, вследствие чего триггеры делителя 4 устанавливаются в состояния, определяемые кодом Мл. После этого сдвиг фаз напряжений и и 1К определяется выражеV o- N4Hi2 o- - U%,.W. где йл. масштабный коэффициент преобразования код - фаза дели теля 4 частоты. Код, соответствующий фазовому сдв гу между сигналами избирательных уси лителей 13 и 14 с учетом гетеродинных напряжений равен . МБ л (,1- ь-М 4 )-X,( ,).. . . При выборе К2 р2Фазовый сдвиг, вносимый делителем 4 частоты, компе сирует фазовую погрешность от неиде тичности преобразовательных характе ристик звеньев в первом и втором тфеобраэовательных каналах и погреш йость кодирования преобразовательных звеньев 16 и 19 и результирующий код Му ,По сигналу 10 управления этот код переносится в регестр 20, где хранится до следующег цикла преобразования, состоящего из трех тактов, Првдла1гаемый преобразователь реа лизуется на современной элементной .базе - интегральных микросхемах. Бл годаря цифровой коррекции погрешнос ти преобразователя снижаются требов ния к стабильносЛ и идентичности характеристик микросхем и их внешни элементов, что позволяет применять 4. 8 более простые и дешевые элементы и уплы. Формула изобретения Преобразователь фаза - код с авто матической коррекцией погрешности преобразования, содержащий в каждом из трех преобразовательных каналов, смеситель и последовательно соедиченный с ним избирательный усилитель, общий для всех преобразовательных каHknoB гетеродин, два преобразователя фазового сдвига в число импульсов, причем входы одного из них соединены с выходами избирательных усилителей первого и второго преобразовательных каналов, входы другого - с выходами избирательных усилителей второго и третьего преобразовательных каналов, счетчик импульсов с двумя регистрами памяти на выходе, реверсивный счетчик импульсов с регистрами памяти на выходе, входы счетчиков импульсов соединены с выходами первого и второго преобразователей фазового сдвига в число импульсов, соответственно, автоматический переключатель, входами соединенный с сигнальными входами смесителей первых двух преобразовательных каналов, а выходом - с сигнальным входом смесителя в третьем преобразовательном канале, блок управления, выходы которого соединены с управляющими входами счетчиков импульсов, регистров памяти и автоматического переключатет ля, отличающийся тем, что, с целью повьш1ения точности преобразования, введены формирователь коротких импульсов и три триггерных делителя частоты, входы которых соединены с выходом формирователя коротких импульсов, входом подключенного к общему гетеродину, выход первого триггерного делителя частоты соединен с управляк м входом смесителя первого преобрагзовательного канала, первый выход второго триггерного делителя частоты соединен с управляющим входом смесителя второго преобразовательного канала, а второйс первым входом блока управления, первый выход третьего триггерного делителя частоты подсоединен к управгляющему входу смесителя третьего преобразовательного канала, а второй выход - ко второму ВХОДУ блока управления, установочные входы первого триггерного делителя частоты соединены с выходом регистра памяти реверсивного счетчика импульсов, выходы регистра памяти другого счетчика соединены с установочными входами второго триггерного делителя частоты. Источники информации, принятые во внимание, при экспертизе 883 78410 I Авторское свидетельство СССР № 564100, ; кл. Н 03 К 13/20, 2. Авторское свидетельство СССР по заявке 2508398/J 8-21, .1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометр | 1985 |

|

SU1298685A1 |

| Преобразователь угла поворотаВАлА B КОд | 1980 |

|

SU842906A1 |

| Фазометр | 1980 |

|

SU960657A1 |

| Преобразователь угловых перемещений в код | 1977 |

|

SU693410A1 |

| Измерительный преобразователь фаза-код | 1977 |

|

SU690626A1 |

| Фазочастотный преобразователь | 1979 |

|

SU873150A1 |

| Измеритель разности фаз | 1977 |

|

SU711492A1 |

| Способ измерения квадратурных составляющих периодических сигналов | 1987 |

|

SU1525599A1 |

| Измерительный узкополосный усилитель | 1982 |

|

SU1072250A1 |

| ФАЗОМЕТР С ЦИФРОВЫМ ОТСЧЕТОМ | 1967 |

|

SU203775A1 |

ff

Авторы

Даты

1981-11-23—Публикация

1980-02-14—Подача