Изобретение относится к технике записи и воспроизведения телевизионных сигналов на магнитную ленту и может использоваться при коррекции временных искажений.

Известно устройство коррекции временных искажений, содержащее блок вытеснения гасящих импульсов, блок формирования сигнала гашения, блок формирования сигнала синхронизации, блок замещения сигнала синхронизации и блок автоматической подстройки частоты (АПЧ), вход которого подсоединен к первым входам синхроселектора и первого дискриминатора, выход которого подключен к последовательно соединенным блоку кодирования и формирования импульсов коммутации ключей, блоку коммутируекых линий задержки, второму дискриминатору и f-корректору 1.

Однако известное устройство имеет узкий диапазон коррекции.

Цель изобретения - расширение диапазона коррекции.

Цель достигается тем, что в устройстве коррекции временных искажений, содержащем блок вытеснения гасящих импульсов, блок формирования сигнала гашения, блок формирования

сигнала синхронизации, блок замещения сигнала синхронизации и блок автоматической подстройки частоты

(АПЧ), вход которого подсоединен к первым входам синхроселектора и первого дискриминатора, выход которого подключен к последовательно

соединенным блоку кодирования и фор.мирования импульсов коммутации клю10чей, блоку коммутируемых линий задержки, второму дискриминатору и -корректору, первый вход блока выбора вида опорного сигнала подключен к выходу блока АПЧ, второй вход

15 блока выбора вида опорного сигнала подключен через блок формирования внешнего опорного импульса к входу устройства, а выход блока выбора вида опорного сигнала подключен к

20 третьему блоку задержки через последовательно соединенные первый и второй блоки задержки, причем выход первого блока защержки подключен к первому входу блока перераспределе25ния опорных сигналов, к первому входу первого элемента И, к входу второго блока задержки, выход которого подключен ко второму входу блока перераспределения опорных сигналов, к

30 первому входу первого элемента ИЛИ

И к входу третьего блока задержки, выход которого подключен к третьему входу блока перераспределения опорных сигналов, к первому входу третьего элемента И и ко второму входу первого элемента ИЛИ, выход которого подключен к первому входу второго элемента И, причем вторые входы первого, второго и третьего элементов И соединены мекду собой и подключены к выходу блока формирования импульсов управления, а выходы первого, второго и третьего элементов И подключены к. соответствующим входам блока перераспределения опорных сигналов, выход которого через

блок формирования опорных СИГНсШОВ

подключен к первым входам первого дискриминатора, второго дискриминатора и ко входу блока фазирования сигнала синхронизации, выход которого подключен к первому входу второго элемента ИЛИ и ко входу модулятора, выход которого подключен к первому входу фазового дискриминатора и через блок выделения заднего фронта подсоединен ко второму входу второго элемента ИЛИ, выход которог подсоединен к блоку формирования сигнала гашения, к блоку формирования сигнала синхронизации и через четвертый блок задержки - ко второму входу фазового дискриминатора, первый выход jcoTOporo подключен к последовательно соединенным первому фильтру и первому ключу, вторрй выход фазового дискриминатора подсоединен к последовательно соединенным второму фильтру, инвертору и втором ключу, а выходы первого и второго ключей объединены и подключены ко входу интегратора, выход которого через фильтр низких частот подключен ко второму входу модулятора, а второй вход интегратора подключен к источнику опорного напряжения, а блок управляемой линии задержки подсоединен к выходу блока коммутируемой линии задержки и к выходам jT-KoppeKTOpa, а выход блока управляемой линии задержки подключен ко входу блока вытеснения гасящих импульсов .

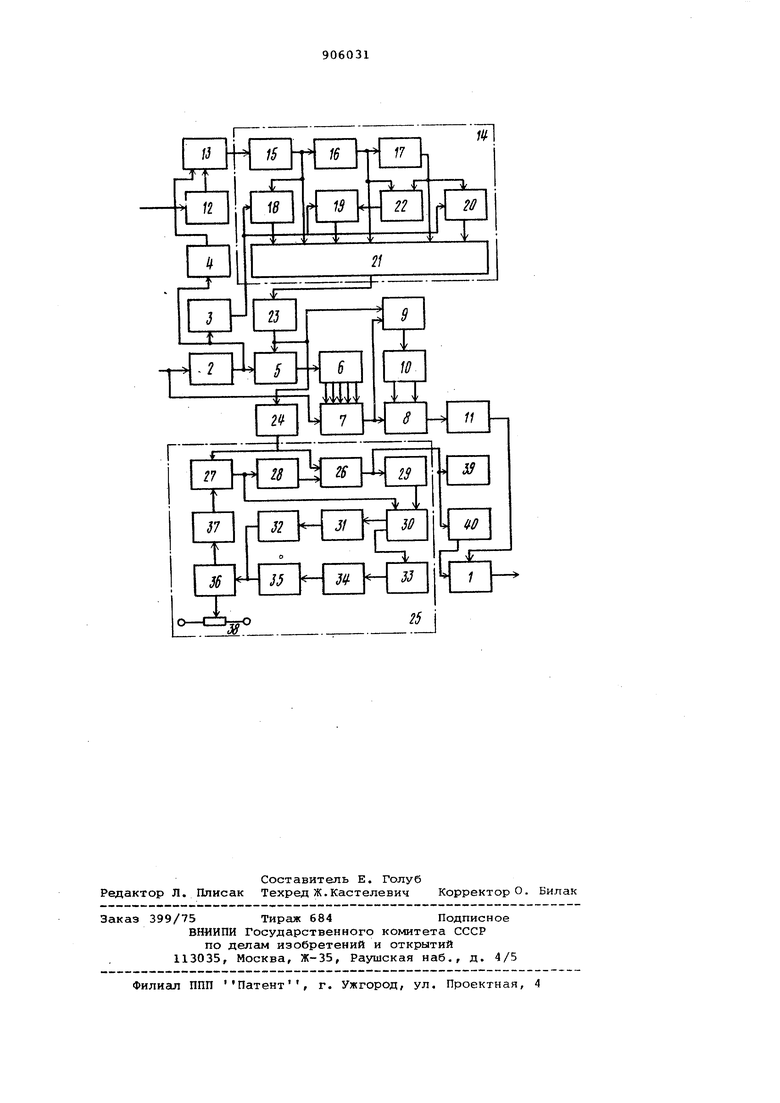

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство коррекции временных искажений содержит блок 1 замещения сигнала синхронизации, синхроселектор 2, блок 3 формирования импульсов управления, блок 4 АПЧ, первый дискриминатор 5, блок б кодирования и формирования импульсов коммутации ключей, блок 7 коммутируемых линий задержки, блок 8 управляемой линии задержки, второй дискриминато 9, f -корректор 10, блок 11 вытесгнения гасящих импульсов, блок 12 формирования внешнего опорного импульса, блок 13 выбора вида опорного сигнала, блок 14 автофазировки опорного сигнала, состоящий из первого, второго и третьего блоков задержки 15, 16, и 17 соответственно, - первого, второго и третьего элементов И 18, 19 и 20 соответственно, блока 21 перераспределения опорных сигналов и первого элемента ИЛИ 22, блок 23 формирования опорных сигная лов, блок 24 формирования сигнала синхронизации, блок 25 удвоения частоты опорного сигнала, состоящий из второго элемента ИЛИ 26, модулятора 27, блока 28 выделения заднего фронта, четвертого блока 29 задержки,

5 фазового дискриминатора 30, первого фильтра 31, первого ключа 32, второго фильтра 33, инвертора 34, второго ключа 35, интегратора 36, фильтра 37 низких часто1 и 3.8

0 опорного напряжения, блок 39 формирования сигнала гашения, блок 40 формирования сигнала синхронизации.

Устройство работает следующим образом.

5 Воспроизводимый с ленты видеосигнал .подается на вход синхроселектора 2. Выходным сигналом синхроселектора являются строчные синхроимпульсы синхронизации, выделенные из

Q входного видеосигнала. В положении передних фронтов этих импульсов заключена информация о временной ошибке воспроизводимоrq, видеосигнала. Эти импульсы поступают на блок 3

« формирования импульсов управления, в котором из передних фронтов формируются короткие импульсы, а также поступают на блок 4 АПЧ, для которого строчные импульсы синхронизации являются ведущими. Выходным сигналом блока 4 являются импульсы, синфазные с выходными импульсами синхроселектора 2 и опережающие передние фронты строчных синхроимпульсов в видеосигнале по меньшей мере на

время, равное диапазону коррекции устройства. Блок 4 имеет достаточно большую постоянную времени (чтобы его выходной сигнал служил опорным для работы устройства коррекции в

Q режиме внутреннего Ьпорного источника сигнала). I

Выходные импульсы синхроселектора 2 поступают также на первый дискриминатор 5, в котором вырабатывается

напряжение ошибки, пропорциональное временному рассогласованию между опорным импульсом и импульсом синхроселектора. Это напряжение управляет работой блока 6 кодирования и

0 формирования импульсов коммутации ключей, в котором вырабатывается код, количество импульсов которого определяется напряжением первого дискриминатора 5. В течение актив5 иой части строки информация в коде

хранится в триггерах промежуточной памяти, расположенных в блоке 6. Выходными сигналами блока 6 являютс потенцисшы с выходов триггеров промежуточной памяти, которыми производится коммутация ключей, содержащих набор дискретных линий,расположенных в блоке 7 комглутируемых линий задержки. На вход блока 7 поступает входной видеосигнал, а с его выхода видеосигнал, содержащий временную ошибку, равную величине дискретности набора линий задержки, поступает на блок 8 управляемой линии задержки и на второй дискриминатор 9. Выходное напряжение второго дискриминатора соответствует остаточной временной ошибке видеосигнала, прошедшего первую ступень коррекции. Это напряжение через f-KOppeKTOp 10 поступает на управляющие входы блока 8 управляемой линии задержки, доводя значение временной остаточной ошибки в видеосигнале до минимального уровня.

Далее рассмотрим формирование опорных импульсов на входах первог и второго дискриминаторов. Внешние опорные импульсы поступают на вход блока 12 формирования внешнего -опорного импульса. Этим блоком формируется импульс, длительность которого равна удвоенному значению диапазона коррекции,устройства. Этот импульс служит в качестве импульса ворота для блока 13 выбора вида опорного сигнала, в котором импульс с выхода блока 4 АПЧ задерживается на время, равное половине длительности импульса, поступающего с выхода блока 12. При такой фазировке сигнала блоком 1 и, следовательно,, входного видеосигнала относительно сигнала внешнего опорного источника на выход блока 13 проходят внешние опорные импульсы. При этом устройство работает от внешнего опорного источника сигнала. В случае расстройки, при которой импульсы сигнала АПЧ выходят за пределы импульса ворота, блок 13 автоматически подключает к выходу импульсы с выхода блока 4 АПЧ. При этом устройство коррекции временных искажений переходит в режим работы от внутреннего опорного источника сигнала, т.е. от выходных импульсов блока 4 АПЧ. Выходные импульсы блока 13 поступгиот на вход блока 14 автофазировки опорного сигнала, входным устройством которого является первый блок задержки 15, и производят запуск этого блока.

Первый блок задержки 15 вырабатывает импульс, длительность которого несколько меньше половины диапазона коррекции. Задним фронтом этого импульса производится запуск второг блока задержки 1б, вырабатывающего

импульс, длительность которого равна длительности импульсов первого блока задержки. Задним фронтом импульса с выхода второго блока задержки производится запуск третьего бло, ка задержки 17, вырабатывающего импульс, длительность которого несколько больше половины диапазона коррекции. Суммарная длительность импульсов с выхода второго и третьего

Q блоков задержки равна величине диапазона коррекции устройства. Выходные импульсы первого блока задержки 15 поступают на вход первого элемента И 18, выходные импульсы второго и третьего блоков задержки поступают

5 на входы первого элемента ИЛИ 22, а выход третьего блока задержки, кроме того, подключен ко входу третьего элемента И 20. Кроме того, выходные импульсы всех трех блоков

0 задержки поступают на блок 21 перераспределения опорных сигналов. На выходе первого элемента ИЛИ 22 образуется импульс, длительность которого равна сумме длительностей импульсов второго и третьего блоков задержки. Этот импульс поступает на второй вход второго элемента И 19. Все первые входы первого, второго и третьего элементов И соединены

Q между собой и на них поступает короткий импульс, выработанный в блоке 3 формирования импульсов управления, совпадающий по времени с положением переднего фронта строчного синхроимпульса, поступающего с

выхода синхроселектора 2.

Далее блок автофазировки опорного сигнала работает следующим образом. В случае, если передний фронт воспроизводимого строчного синхроимпульса располагается в пределах длительности импульса, поступающего с выхода первого элемента ИЛИ 22, на выход второго элемента И 19 пройдут короткие импульсы, поступающие

с выхода блока О формирования импульсов управления. Этими импульсами производится управление блоком 21 таким образом, что на его выход проходят импульсы с выхода второго блока задержки 16. При этом положение передних фрюнтов этих импульсов служит опорным для работы первого и второго фазовых дискриминаторов, а длительность импульса ворота

определяет номинальный диапазон коррекции устройства. Такая фазировка переднего фронта воспроизводимого строчного синхроимпульса относительно опорного соответствует номинальной работе устройства. В случае, если

стык программ выполнен таким образом, что передний фронт воспроизводимого строчного синхроимпульса в смонтированной програ име располагается между передними фронтами импульсов, следующих с выходов первого и второго блоков задержки, т.е. в пределах длительности импульса с выхода первого блока задержки 15, на вход блока 21 проходят импульсы не с выхода второг элемента И19, а с выхода первого элемента И 18, так как на его входах указанные импульсы совпадают по времени. При этом блок 21 подключает на вход опорный импульс с выхода первото блока задержки 15, Следовательно, на входы первого и второго дискриминаторов через блок 23 формирования опорных сигналов проходят импульсы, опережающие свое номинальное положение на величину, несколько меньшую половины диапазона коррекции, т.е. на величину длительности импульса с выхода первого блока задержки 15, а корректированный видеосигнал с выхода устройства опережает свое номинальное положение на ту же величину. В случае воспроизведения смонтированной программы, в которой передний фронт воспроизводимого синх роимпульса расположен между задним фронтом импульса, следующего с выхода первого элемента ИЛИ 22 и задним фронтом импульса, на вход блока 21 поступают импульсы с выхода третьего элемента И 20. При этом блок 21 подключает на выход импульсы, следующие с выхода третьего бло ка задержки 17. Следовательно, на входы первого и второго фазовых дис криминаторов через блок 23 проходят импульсы, отстающие относительно но минального положения на вели«1ину, несколько меньшую половины диапазона коррекции, т.е. на величину длительности импульса, вырабатываемого во втором блоке задержки 16. Передние фронты этих импульсов совпадгиот с передними фронтами импульсов, вырабатываемых третьим блоком задержки. При такой новой фазировке выходной корректированный видеосигнал отстает относительно своего номинал ного положения на величину длительности импульса, вырабатываемого вто рым блоком задержки 1-6. Коммутируемый опорный импульс, поступающий с выхода блока 23 формирования опорных сигналов являющий ся опорным для первого дискриминато ра 5, поступает также на вход блока 24 фазирования сигнала синхронизаци в котором производится фазирование сигнала синхронизации, вырабатываемого устройством с синхросигналом видеосигнала, поступающего с выхода блока 8 управляемой линии задержки. Импульсы с выхода блока 2 фазирования сигнала синхронизации поступают на блок 25 удвоения частоты опорного сигнала, с которого подаются на первый вход второго эле |мента ИЛИ 26 и на запуск модулятора 27, представляющего из себя управляемую схему задержки, формирующую импульс, длительность которого равна половине периода строчных синхроимпульсов. Задний фронт этого импульса через блок 28 выделения заднего фронта поступает на второй вход второго элемента ИЛИ 26, с выхода которого импульсы двойной строчной частоты поступают на запуск четвёртого блока 29 задержки, который вырабатывает импульсы с длительностью. Несколько меньшей половины периода строчной развертки. Выходные импульсы четвертого блока 29 задержки, а также импульсы с выхода модулятора 27 поступают на фазовый дискриминатор 30, который перераспределяет импульсы, следующие с двойной строчной частотой по двум каналам (по прямому и инверсному) причем по прямому каналу пропускает импульсы-с выхода четвертого блока 29 в момент передачи положительного разрешающего потенциала с выхода модулятора 27, а по инверсному каналу - в момент передачи отрицательного разрешающего потенциала с выхода модулятора 27. Прямой канал фазового дискриминатора содержит первые фильтр 31 и ключ 32, а инверсный канал содержит второй фильтр 33, инвертор 34, второй ключ 35. Фильтры 31 и 33 нормируют крутизну фронтов импульсов, передвигаег ых по обоим каналам таким образом, чтобы обеспечить прохождение импу;й.са через инвертор без каких-либо искажений его формы. Выходы ключей объединяются, образуя канал разнополярных импульсов, которые поступают на интегратор 36, где происходит перезаряд элемента памяти, а момент действия разнополярных импульсов. С выхода интегратора 36 постоянным потенциалом через фильтр 37 низких частот производится управление модулятором 27 путем изменения средней задержки заднего фронта импульса, формируемого модулятором 27. Исходная установка по положению заднего фронта этого импульса, соответствующая полови41е Периода строчной частоты, производится регулировкой опорного напряжения от источнику 38 опорного напряжения. Измерения частоты опорного сигнала а по точности и стабильности установки задержанного фронта модулятора и, следовательно, двойной строчной частоты на выходе блока 25 показывают возможность установки фазы с точностью +2 НС, а в диапазоне температур 20 - 60° диапазон дрейфа этой фазы не превышает +4 не и зависит от величины коэффициента передачи модулятора по постоянному току и от дрейфа коэффициента передачи инвертора 34. Выходной сигнал блока

25 с выхода второго элемента ИЛИ 26 поступает на вход.блока 39 формирования сигнала гашения и на вход блока 40 формирования сигнала синхронизации, С выхода блока 8 управляемой линии задержки видеосигнал, прошедший временную коррекцию, поступает на вход блока И вытеснения гасящих импульсов, где происходит вытеснение старых гасящих импульсов из видеосигнала импульсами, поступающими с выхода блока формирования сигнала гашения. С выхода блока 11 вытеснения гасящих импульсов видеосигнал поступает на вход блока 1 замещения сигнала синхронизации.

Таким образом, на выходе устройства формируется полный видеосигнал, в котором остаточная ошибка соответствует своему номинальному значению, а стабильность сигнала синхронизации равна стабильности внешнего опорного сигнала, если, во-первых, он присутствует и, во-вторых, если положение переднего фронта воспроизводимого строчного синхроимпульса располагается в пределах длительности импульса, следующего с выхода блока 12 формирования внешнего опорного импульса, длительность которого несколько меньше удвоенной величины диапазона коррекции устройства. В случае, если внешний опорный сигнал отсутствует, стабильность сигнала синхронизации в полном видеосигнале на выходе устройства равна стабильности сигнала внутреннего опорного источника, сигнала, формируемого в блоке 4 АПЧ.

Формула изобретения

Устройство коррекции временных искажений, содержащее блок вытеснения гасящих импульсов, блок формирования сигнала гашения, блок формирования сигнала синхронизации,бло замещения сигнала синхронизации и блок автоматической подстройки частоты (АПЧ), вход которого подсоединен к первым входам синхроселекгора и первого дискриминатора, выход которого подключен к последовательно соединенным блоку кодирования и формирования импульсов ком тации ключей, блоку коммутируе1 ых линий задержки, второму диcкpИEvшнaтopy и -J KOppeKTOpy, отличающеес я тем, что, с целью расширения диапазона коррекции, первый вход блока выбора вида опорного сигнала подключен к выходу блока АПЧ, второ вход блока выбора вида опорного сигнала подключен через блок формирования внешнего опорного импульса к входу устройства, а выход блока выбора вида опорного сигнала подключен к третьему блоку задержки через последовательно соединенные первый и второй блоки задержки, причем выход первого блока задержки подключен к первому входу блока перераспределения опорных сигналов, к первомувходу первого элемента И, к входу второго блока задержки, выход которого подключен ко второму входу блока п.ерераспределения опорных сигналов, к первому входу первого элемента ИЛИ и к входу третьего блока задержки, выход которого подключен к третьему входу блока перераспределения опорных сигналов, к первому входу третьего элемента И и ко второму входу первого элемента ИЛИ, выход которого подключен к первому входу второго элемента И, причем вторые входы первого, второго и третьего элементов И соединены между собой и подключены квыходу блока формирования импульсов управления, а выходы первого, второго и третьего элементов И подключены к соответствующим входам блока перераспределения опорных сигналов, выход которого через блок формирования опорных сигналов подключен к первым входам первого дискриминатора, второго дискриминатора и ко входу блока фазирования сигнала синхронизации, выход которого подключен к первому входу второго элемента ИЛИ и ко входу модулятора, выход которого подключен к первому входу фазового дискриминатора и через блок выделения заднего фронта подсоединен ко второму входу второго элемента ИЛИ, выход которого подсоединен к блоку формирования сигнала гашения, к блоку формировани сигнала синхронизации и через четвертый блок задержки - ко второму входу фазового дискриминатора, первый выход которого подключен к последовательно соединенным первому фильтру и nepBOf-iy ключу, второй выход фазового дискриминатора подсоединен к последбвательно соединенным второму фильтру, инвертору и второму ключу, а выходы первого и второго ключей объединены и подключены ко входу интегратора, выход которого через фильтр низких частот подключен ко второму входу модулятора, а второй вход интегратора подключен к источнику опорного напряжения, а блок управляемой линии задержки подсоединен к выходу блока коммутируемой линии задержки и к выходам f-корректора, а выход блока управляемой линии задержки, подключен ко входу блока вытеснения гасящих импульсов.

Источники информации, принятые во внимание при экспертизе

1. Гончаров В.Д., Лазарев В.И. Техника магнитной-записи, М., Энергия, 1978, с. 226-229, 196-199.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации временных искажений | 1980 |

|

SU965018A1 |

| Устройство для выделения синхроимпульсов из полного видеосигнала | 1980 |

|

SU924913A1 |

| Устройство коррекции временных искажений | 1980 |

|

SU932648A1 |

| Частотный модулятор для устройств магнитной видеозаписи | 1984 |

|

SU1254593A1 |

| Устройство обнаружения цветоразностных сигналов | 1982 |

|

SU1085017A1 |

| Устройство синхронизации видеомагнитофона | 1981 |

|

SU965015A1 |

| Канал воспроизведения видеомагнитофона | 1980 |

|

SU886319A1 |

| Канал синхронизации видеомагнитофона | 1982 |

|

SU1031001A1 |

| Устройство выделения сигнала синхронизации из полного телевизионного сигнала | 1980 |

|

SU930744A1 |

| Устройство для измерения параметров радиотелевизионной передающей станции | 1973 |

|

SU510811A1 |

Авторы

Даты

1982-02-15—Публикация

1980-05-28—Подача