(54) УСТРОЙСТВО КОМПЕНСАЦИИ ВРЕМЕННЫХ ИСКАЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство коррекции временных искажений | 1980 |

|

SU932648A1 |

| Устройство коррекции временных искажений | 1980 |

|

SU906031A1 |

| Устройство для выделения синхроимпульсов из полного видеосигнала | 1980 |

|

SU924913A1 |

| Канал воспроизведения видеомагнитофона | 1980 |

|

SU886319A1 |

| Устройство подавления шума в канале воспроизведения видеомагнитофона | 1983 |

|

SU1124451A1 |

| Устройство выделения сигнала синхронизации из полного телевизионного сигнала | 1980 |

|

SU930744A1 |

| Измеритель дифференциальных искажений | 1983 |

|

SU1223409A1 |

| Канал синхронизации видеомагнитофона | 1982 |

|

SU1031001A1 |

| Устройство обнаружения цветоразностных сигналов | 1982 |

|

SU1085017A1 |

| Устройство совмещения изображений телевизионной стереопары | 1987 |

|

SU1438024A2 |

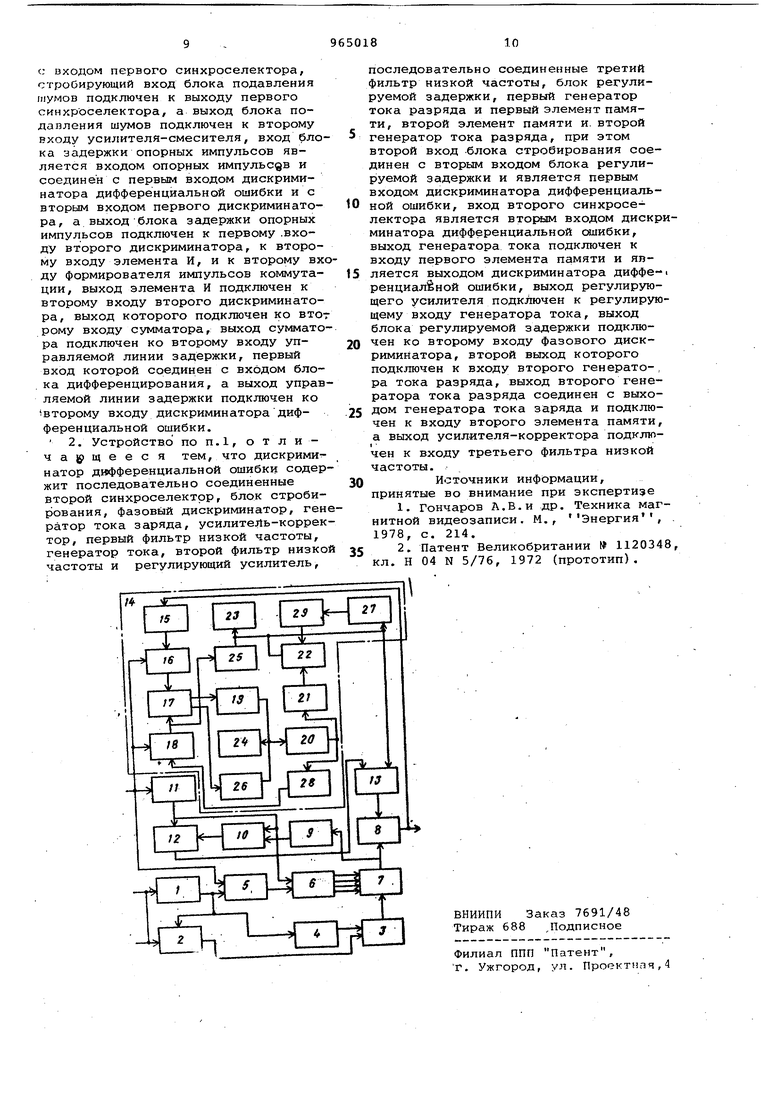

Изобретение относится к технике записи и воспроизведения телевизионных сигналов на магнитную ленту и может использоваться в многоголовочном видеомагнитофоне. Известно устройство компенсации временных искажений, содержащее последовательно соединенные синхроселектор, блок коммутируемых линий за держки и управляемую линию задержки последовательно соединенные дискриминатор и формирователь импульсов коммутации, причем выход синхроселек тора -подключен к, входу дискриминатора, вход синхроселектора является входом видеосигнала, выходы формирователя импульсов коммутации подключены к соответствующим входам блока коммутируемых линий задержки, а выход управляемой линии задержки являе ся выходом видеосигнала 1. I. Недостатком данного устройства является малый диапазон компенсации временной ошибки. Наиболее близким по техническол у решению к предлагаемому изобретению является устройство компенсации временных искажений, содержащее последовательно соединенные первый синхро селектор, блок формирование импульсов врезки, усилитель-смеситель, блок, коммутируемых линий задержки и управляемую линию задержки, последовательно соединенные первый дискриминатор и формирователь импульсов коммутации, второй дискриминатор, причем вход первого синхроселектора является входом видеосигнала, выход первого синхроселектора подключен к первому входу первого дискриминатора, выходы формирователя импульсов коммутации подключены к соответствующим входам блока коммутируемых линий задержки, а выход управляемой линии задержки является выходом видеосигнала f2j. Однако при применении двигателя блока головок видеомагнитофона на шариковых подшипниках, известное устройство компенсации временных искажений не обеспечивает достаточной компенсации временной ошибки, особенно к концу активной части строки. Цель изобретения - повышение точности .компенсации временной ошибки. Поставленная цель достигается тем, что в устройство компенсации временных искб1жений, содержащее последовательно соединенные первый синхроселектор, блок формирования импульсов прозки, усилитель-смеситель, блок коммутируемых линий задержки и управляемую линию задержки, последова тельно соединенные первый дискриминатор и формирователь импульсов ком мутации, второй дискриминатор, причем вход nepisoro синхроселектора яв ляется входом видеосигнала, выход первого синхроселектора подключен к первому ВХОДУ первого дискриминатора-, выходы формирователя импуль сов (коммутации подключены к соответствующим входам блока коммутируемых линий задержки, а выход управляемой линии задержки является выходом видеосигнала, введены блок подавления шумов, блок задержки опо ных импульсов, последовательно соединенные дискриминатор дифференциальной ошибки и сумматор, последова тельно соединенные блок дифференцир вания и элемент И, при этом вход бл ка подавления шумов соединен с входом первого синхроселектора,. строби рующий вход блока подавления шумов подключен к выходу первого синхроселектора, а выход блока пода.вления шумов подключен к второму входу уси лителя смесителя, вход блока задерж опорных импульсов является входом опорных импульсов и соединен с первым входом дискриминатора дифференциальной ошибки и с вторым входом первого дискриминатора, а выход бло ка задержки опорных импульсов подключен к первому входу второго диск риминатора, к второму входу элемента И, и к второму входу формирователя импульсов коммутации, выход элемента И подключен к второму вход второго дискриминатора, выход которого подключен ко второму входу сумматора, выход сумматора подключе к второму входу управляемой линии задержки, .первый вход которой соединен с входом блока дифференцирова ния, а выход управляемой линии задержки подключен к второму входу дискриминатора дифференциальной ошибки. При этом дискриминатор дифференциальной ошибки содержит последовательйо соединенные второй синхроселектор, блок стробирования, фазовый дискриминатор, генератор тока заряд усилитель-корректор, первый фильтр низкой Частоты, генератор тока, вто рой фильтр низкой частоты и регу лирующий усилитель, последовательно соединенные третий фильтр низкой частоты, блок регулируемой задержки первый генератор тока разряда и пер вый элемент памяти, второй элемент памяти и второй генератор тока разряда, при этом второй вход блока стробирования соединен с вторым вхб дом блока регулируемой задержки и является первым входом дискриминатора дифференциальной ошибки, вход второго синхроселектора является вторым входом дискриминатора диф.ференциальной ошибки, выход генератора тока подключен к входу первого элемента памяти и является выходом дискриминатора дифференциальной ошибки, выход регулирующего усилителя подключен к регулирующему входу генератора тока, выход блока регулируемой задержки подключен к второму входу фазового дискриминатора, второй выход.которого подключен к входу второго генератора тока разряда, выход второго генератора тока разряда соединен с выходам генератора тока заряда и подключен к входу второго элемента памяти, а выход усилителякорректора подключен к входу третьего фильтра низкой частоты. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство компенсации временных искажений содержит первый синхроселектор 1, блок 2 подавления шумов, усилитель-смеситель 3, блок 4 формирования импульсов врезки, первый дискриминатор 5, формирователь б импульсов коммутации, блок 7 коммутируемых линий задержки, управляемую линию 8 задержки, блок 9 дифференцирования, элемент И 10, блок 11 задержки опорных импульсов, второй дискриминатор. 12, сумматор 13, дискриминатор 14 дифференциальной ошибки, который включает в себя второй синхроселектор 15, блок 16 стробирования, фазовый дискриминатор L7, блок 18 регулируемой задержки, генератор 19 тока заряда, усилитель-корректор 20, первый фильтр 21 низкой частоты, генератор 22 тока, первый и второй элементы памяти 23 и 24, первый и второй генераторы 25 и 26 тока разряда, второй и третий фильтры 27 и 28 низкой частоты и регулирующий усилитель 29. Устройство работает следующим образом. На вход первого синхроселектора 1 подается видеосигнал с помехами воспроизведения. Первый синхроселектор выделяет строчные синхроимпульсы с некоторой задержкой. Передним фронтом строчного синхроимпульса запускается блок 2 подавления шумов, который подавляе,т шум, а также переходные процессы коммутаций на вершине строчного синхроимпульса. Подавление шума заканчивается перед задним фронтом строчного синхроимпульса за 1-2 МКС. Обработанный таким образом видеосигнал поступает на второй вход усилителя-смесителя 3. На первый вход усилителя-смесителя поступают корот кие импульсы, сформированные из передних фронтов строчных синхроим.пульсов. Задержка и формирование импульсов по длительности и крутизн фронтов производится в блоке 4 формирования импульсов врезки. Нормирование импульса врезки по крутизна обеспечивает прохождение этого импульса через набор дискретных линий задержки без каких-либо искажений. В усилителе-смесителе 3 происходит суммирование двух сигналов. Таким образом, положение;переднего фронта строчного синхроимпульса с соответствующим сдвигом во времени оказыiBaeTCH задублированным на вершине строчного синхроимпульса в виде короткого импульса врезки, причем на месте, очищенном от шума в видеосиг нале. Для того, чтобы сработала пер вая ступень коррекции, включающая набор дискретных линий задержки, строчный синхроимпульс с выхода син хроселектора 1 подается на первый вход первого дискриминатора 5, на второй вход которого подаются опорные умпульсы. Выходным сигналом первого дискриминатора 5 является напряжение ошибки, пропорциональное величине временного рассогласования между опорными импульсами и передни ми фронтами строчных синхроимпульсов. Это напряжение в формирователе 6 импульсов коммутации преобразуется в код, в соответствии с которым коммутируются линии задержки в блоке 7 коммутируемых линий задержки. Переключение линий задержки производится в момент времени межДУ передним фронтом строчного синхроим пульса и передним фронтом импульса врезки, что обеспечивается подачей на второй вход формирователя б импульсов коммутации опорных импульсо задержанных в блоке 11 задержки опо ных импульсов. Видеосигнал с времен ной ошибкой, равной величине дискре ности набора линии задержки, с выхо да блока 7 поступает на вход управляемой линии 8 задержки и на вход блока 9 дифференцирования, который работает по известному принципу оптимальной обработки импульсного сиг нала, позволяющему повысить точност выделения фронта сигнала при наличии помех. Помехи возникают в блоке коммутируемых линий задержки. Кроме того,В результате коммутации имеет ся переходный процесс, спадающий i концу задней площадки строчного гасящего импульса по экспоненциальному закону. Дополнительные ошибки возникают из-за наличия на вершине строчного синхроимпульса остатков о шума и помехи переключения видеоголовок . Выделенный блоком дифференцирования импульс врезки, подается на первый вход элемента И 10, а на второй его вход подается опорный импульс с блока 11 задержки опорных импульсов. Сигнал с выхода элемента И 10 поступает на второй вход второго дискриминатора 12. Положение фронта импульса врезки, ввделенного на выходе элемента И 10 соответствует величине временной остаточной ошибки видеосигнала, пропущенного через дискретные линии задержки, т.е. через первую ступень коррекции. Поэтому выходное напряжение второго дискриминатора 12 соответствует остаточной временной ошибке в видеосигнале, прошедшем первую ступень коррекций. Это напряжение подается на второй вход суммаiTOpa 13. С его выхода напряжением ошибки производится регулирование управляемой линии 8 задержки. Напряжение с выхода второго дискриминатора 12 является постояннымв течейие активной части строки, а точнее от импульса врезки до импульса врезки. Таким образом, временные ошибки устраняются практически полностью в районе заднего фронта строчного гасящего импульса, а к концу активной части строки происходит накопление временной ошибки, вызванное качанием двигателя блока головок. Это накопление дифференциальной сяиибки имеет максимальную величину в момент передачи переднего фронта строчного синхроимпульса. Следовательно, положение переднего фронта строчного синхроимпульса может служить датчиком величины дифференциальной саиибки, поскольку как коммутация дискретных линий задержки, так и смена напряжения регулировки, поступающего на управляемую линию 8 задержки происходит после того как передний фронт строчного синхроимпульса выйдет из управляемой линии 8 задержки. Для определения величины дифференциальной ошибки и выработки соответствующего напряжения регулировки, поступающего на управляемую линию задержки, видеосигнал подается на вход дискриминатора 14 дифференциальной ошибки. В синхроселекторе 15 происходит выделение переднего фронта строчного синхроимпульса, который подается на блок 16 стробирования. Выходные импульсы стробирования поступают на первый вход фазового дискриминатора 17, на второй вход которого подаются импульсы с выхода блока 18 регулируемой задержки. Передний tpOHT этих импульсов расположен посередине импульса, следующего с рыхода блока 16 стробирования. Выходными импульсами фазового дискриминатора 17 являются пара импульсов, суммарная длительность которых равна длительности импульса с выхода блока 16 стробирования. В случае отсутствия дифференциальной ошибки эти импульсы между собой рав .ны. При наличии дифференциалыяой -ошибки длительность этих импульсов друг относительно друга перераспределяется согласно изменениям в поло жении переднего фронта строчных син роимпульсов, оставаясь в сумме по.стоянной величиной. Эта пара импуль сов поступает на второй генератор 2 тока разряда и генератор 19 тока за ряда. На время действия каждого из этих импульсов включается соответствующий генератор тока, разряжая или заряжая загрузочный конденсатор второго элемента 24 памяти. Далее напряжение со второГо элемента памяти поступает на усилитель корректор 20, в котором происходит усиление сигнала ошибки и коррекция его по фазе в области верхних частот отстаиваемого внутристрочной ко рекцией частотного диапазона. С вых да уйийителя-корректора 20 напряжен ошибки чЪрез третий фильтр 28 низкой частоты поступает на блок 18 регулируемой задержки. Напряжением дифференциальной оши ки с выхода второго элементапамяти через первый фильтр 21 низкой часто ты производится управление генерато ром 22 тока.Этот генератор тока,раб тая в линейном режиме,обеспечивает на выходе ток, пропорциональный величине Напряжения дифференциальной ошибки. Кроме того, при смене полярности сигнала дифференциальной ошибки, меняется знак генерируемого тока. Генератор 22 тока нагружен на первый элемент 23 памяти. Разряд конденсатора первого элемента памяти осуществляет первый генератор 25 тока разряда, запуск которого производится импульсами с выхода блока 18 регулируемой задержки. Собственные нестабильности генератора 22 тока отрабатываются петлей обратной связи, в которую входи .второй фильтр 27 низ.кой частоты и регулирующий усилитель 29. Регулиро вка осуществляется таким образом, чтобы нулевому значению напряжения Дифференциальной ошибки на входе генератора 22 тока соответствовало нулевое значение напряжения на первом элементе 23 памяти. Пилообразно напряжение, соответствующееизменению дифференциальной ошибки внутри активной части строки, поступает на сумматор 13, где суммируется с напряжением, поступающим с выхода второго дискриминатора 12, и суммарное напряжение ошибки, соответствующее изменению временной ошибки в пределах активной части строки поступает на регулирующий вход уп-равляемой линии 8 задержки. Таким образом, внутристрочный корректор представляет из себя систему авторегулирования первого порядка. Параметр регулирования - отклонение положения переднего фронта строчного синхроимпульса от номинального положения. Наличие обратной связи уменьшает собственные нестабильности дискриминатора дифФеренциальной ошибки, улучшает как частотную, так и фазовую характеристики в полосе отстраиваемых внутристрочным корректором частот, а также стабилизируется коэффициент передачи внутристрочного корректора. Фазовая характеристика в данном случае особо важна, так как определение дифференциальной ошибки производится в конце активной части строки, а в пределах самой строки производится экстраполяция значения напряжения ошибки. За счет этого временные ошибки компенсируются не только в начальной части строки, но и во всей активной части строки, что выгодно от- личает данное устройство от прототипа. Формула изобретения 1. Устройство компенсации временных искажений, содержащее последовательно соединенные первый синхроселектор, блок формирования импульсов врезки, усилитель-смеситель, блок коммутируемых линий задержки и управляемую линию задержки, последовательно соединенные первый дискри- в минатор и формирователь импульсов коммутации, второй дискриминатор, причем вход первого синхроселектора |является входом видеосигнала, вы1ход первого синхроселектора подключен к первому входу первого дискриминатора,выходы формирователя импульсов коммутации подключены к соответствующим входам блока коммутируемых линий задержки, а выход управляемой линии задержки является выходом видеосигнала, отличающееся тем, что, с целью повышения точности компенсации временной ошибки, введены блок подавления шумов, блок задержки опорных 1мпульсов, последовательно соединенные дискриминатор дифференциальной ошибки и сумматор, последовательно соединенные блок дифференцирования и элемент И, при этом (вход блока -подавления шумов соединен с входом первого синхроселектора MVMon ° подавления УМОВ подключен к выходу первого синхроселектора, а выход блока полапления шумов подключен к второму входу усилителя-смесителя, вход бл ка задержки опорных импульсов является входом опорных импульсов и соединен с первым входом дискриминатора дифференциальной ошибки и с вторым входом первого дискриминатора, а выход блока задержки опорных импульсов подключен к первому .входу второго дискриминатора, к второму входу элемента И, и к второму вк ДУ Формирователя импульсов коммутации, выход элемента И подключен к второму входу второго дискриминатора, выход которого подключен ко вто рому входу сумматора, выход суммато ра подключен ко второму входу управляемой линии задержки, первый вход которой соединен с входом бло.ка дифференцирования, а выход управ ляемой линии задержки подключен ко второму входу дискриминатора дифференциальной ошибки. 2. Устройство по п. 1, о т л и чай)щееся тем, что дискриминатор дифференциальной ошибки содержит последовательно соединенные второй синхроселектрр, блок стробирования, фазовый дискриминатор, гене ратор тока заряда, усилитеЛь-корректор, первый фильтр низкой частоты, генератор тока, второй фильтр низкой частоты и регулирующий усилитель. 18 последовательно соединенные третий фильтр НИЗКОЙ частоты, блок регулируемой задержки, перв генератор тока разряда и первый элемент памяти, второй элемент памяти и второй генератор тока разряда, при этом второй вход .блока стробирования соеSV M Лом блока регулируемой задержки и является первым дискриминатора дифференциальной ошибки, вход второго синхроселектора является вторым входом дискриминатора дифференциальной ошибки выход генератора тока подключен к входу первого элемента памяти и является выходом дискриминатора диффе-. ренциалйной ошибки, выход регулирующего усилителя подключен к регулирующему входу генератора тока, выхоГ регулируемой задержки подключен ко второму входу фазового дискриминатора, второй выход которого подключен к входу второго генератора тока разряда, выход второго генератора тока разряда соединен с выходом генератора тока заряда и подключен к входу второго элемента памяти а выход усилителя-корректора подклюен к входу третьего фильтра низкой астоты, Источники информации, ринятые во внимание при экспертизе 1. Гончаров Л.В.и др. Техника маг °й видеозаписи . М. , Энергия, 2. Патент Великобритании № 1120348 л. Н 04 N 5/76, 1972 (прототип).

Авторы

Даты

1982-10-07—Публикация

1980-04-30—Подача